使用AXI4总线实现视频输入输出

描述

Xilinx vivado下通常的视频流设计,都采用Vid In to axi4 stream --> VDMA write --> MM --> VDMA read --> axi4 stream to video out这样的路径。网上例子很多,官方参考也有xapp521,实现起来参考无压力。

但这套方案明显的问题是,缓存图像带来帧延迟,对于一些延迟要求高的任务,反倒不希望有VDMA的参与。此外,对于一些简单的应用,不希望有Zynq PS核的参与配置,简化系统复杂度。因此我就有了 "Video In to AXI4-stream" to "AXI4-stream to Video Out" directly with VTC without VDMA的需求。

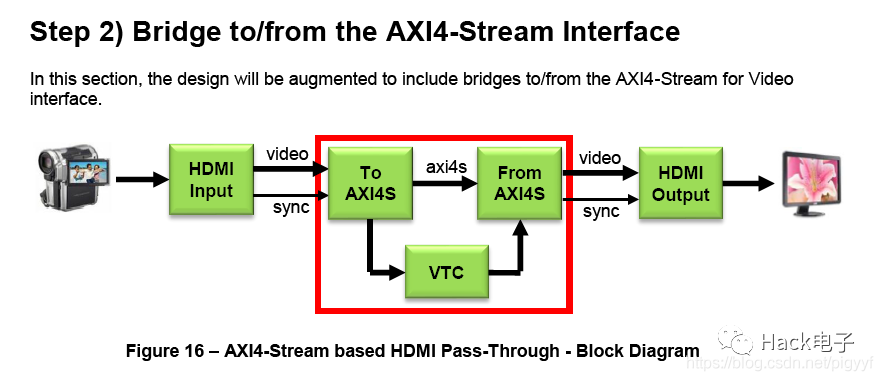

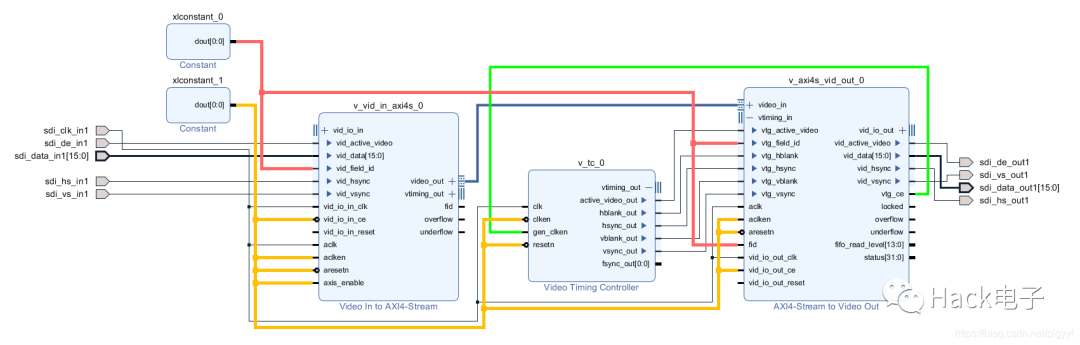

看过好几个Xilinx的product guide(pg043 vid_in_axi4s)和其他的第三方参考(AVNET的《building a video design from scratch tutorial》)都明确说可以实现如下图的框架。不需要VDMA的参与。但是没有官方的XAPP,按照这个框架搭建后,调试很久视频都不能正常显示。

网上有些帖子,给出了一些建议参考。

但是,或多或少都没有说明白的地方,配置GUI没有展开细说,我照着搭建依旧出现很多困难,没有成功。但反复琢磨上面几个例子的异同,反复读了pg043,pg016,pg044几份文档细节,终于找到了出路。现在总结如下。

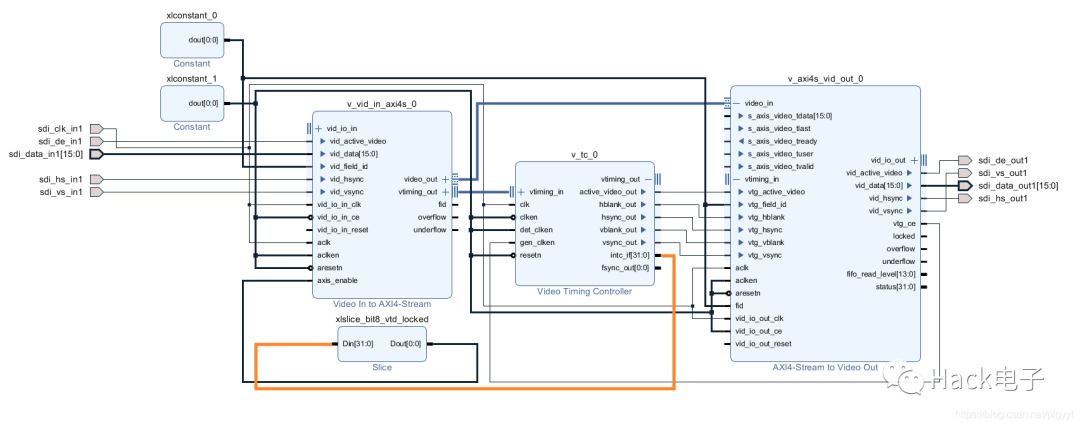

1.先上总设计框图

我是SDI输入输出(1920x1080@30P),用的GS2971和GS2972的组合,其他在顶层verilog测试好了,数据data、同步de/hs/vs直通显示是没有问题的,在这个基础上添加了上述的IP,把同步视频流转到axi4-stream总线上。

该框图设计在top.v接口代码如下:

design_1_wrapper sSDI_design( .sdi_clk_in1(wClkSDI), .sdi_data_in1({DOUT[9:2],{DOUT[19:12]}}), .sdi_de_in1(SDI_IN_DE), .sdi_hs_in1(SDI_IN_H), .sdi_vs_in1(SDI_IN_V), .sdi_data_out1({DIN[9:2],DIN[19:12]}), .sdi_de_out1(SDI_OUT_DE), .sdi_hs_out1(SDI_OUT_H), .sdi_vs_out1(SDI_OUT_V));

框图没什么难点,关键是一些细节的连线,和IP内部的设置,下面展开讲讲要注意的地方。

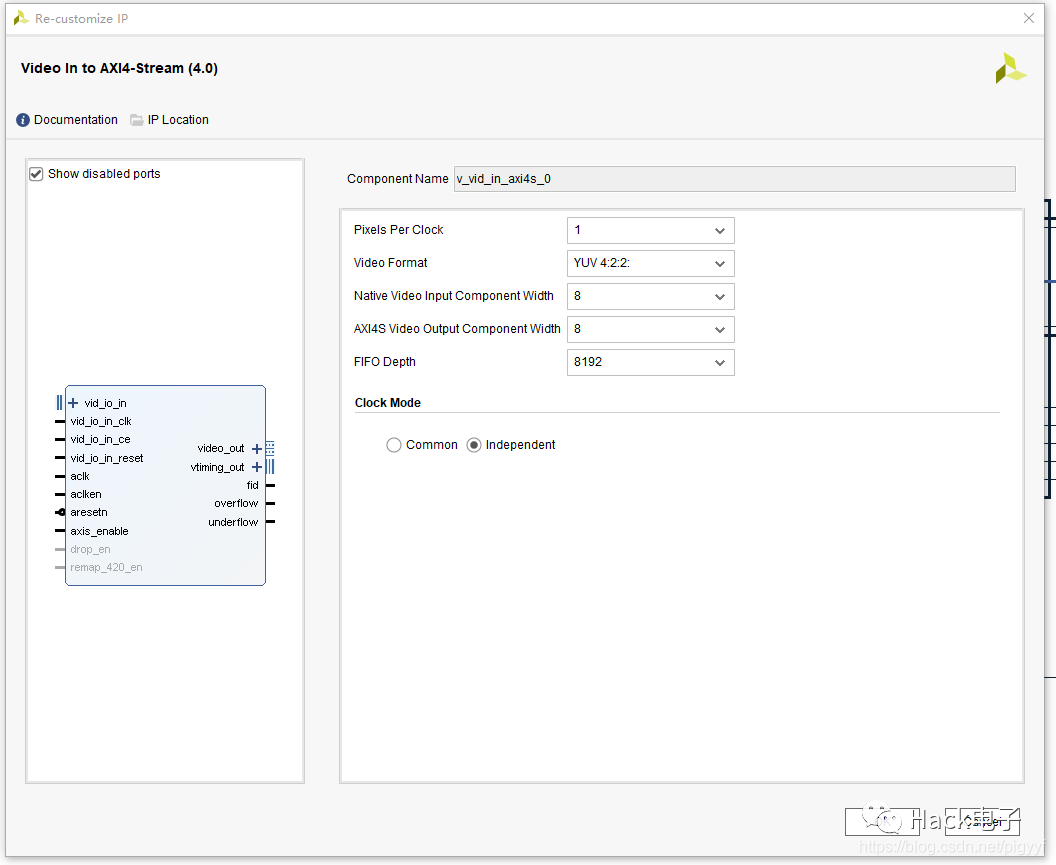

2. Video in to AXI4-stream下的配置

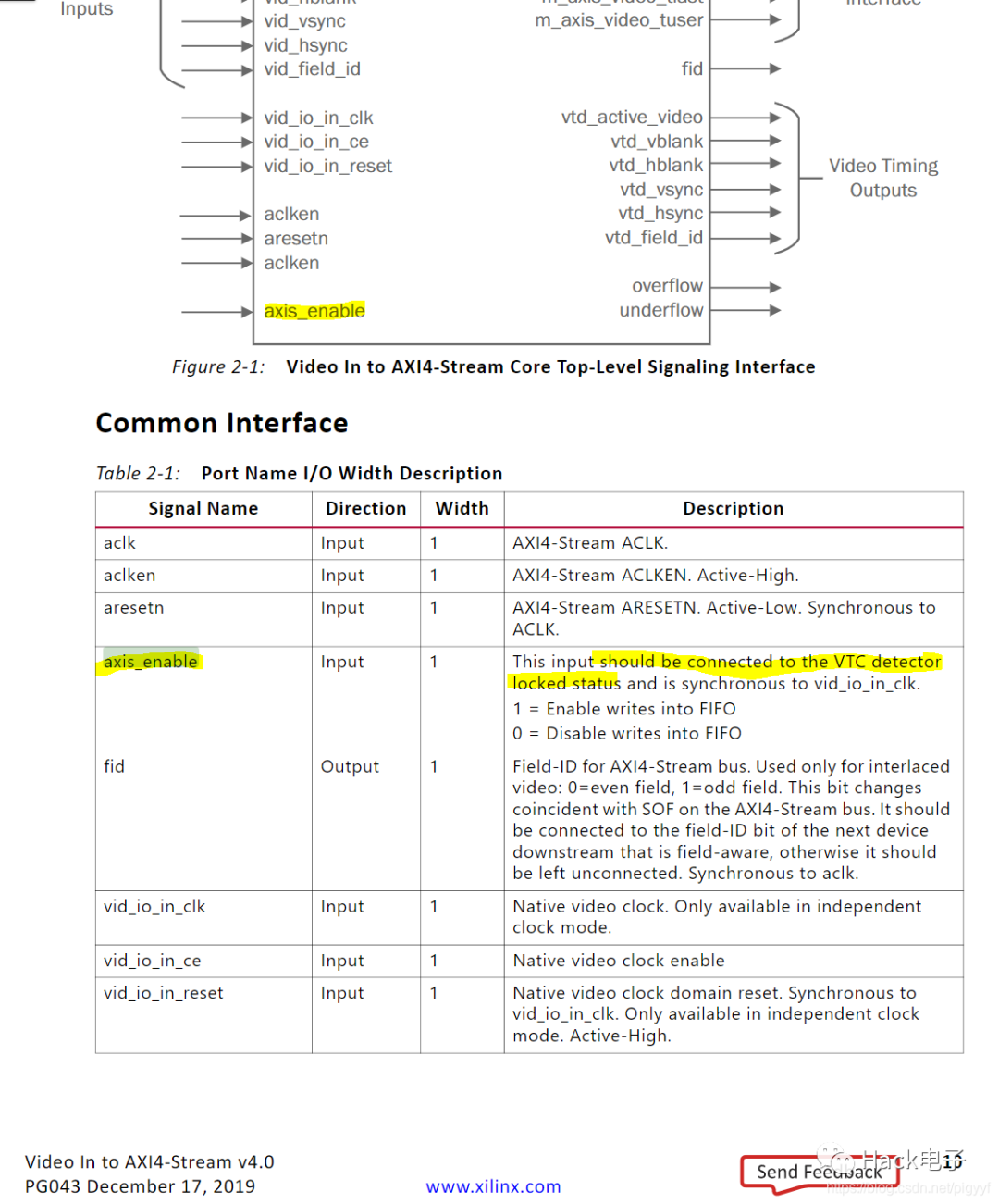

关于axis_enable管脚。

(1)axis_enable可以直接接“1”拉高,实测没有问题。

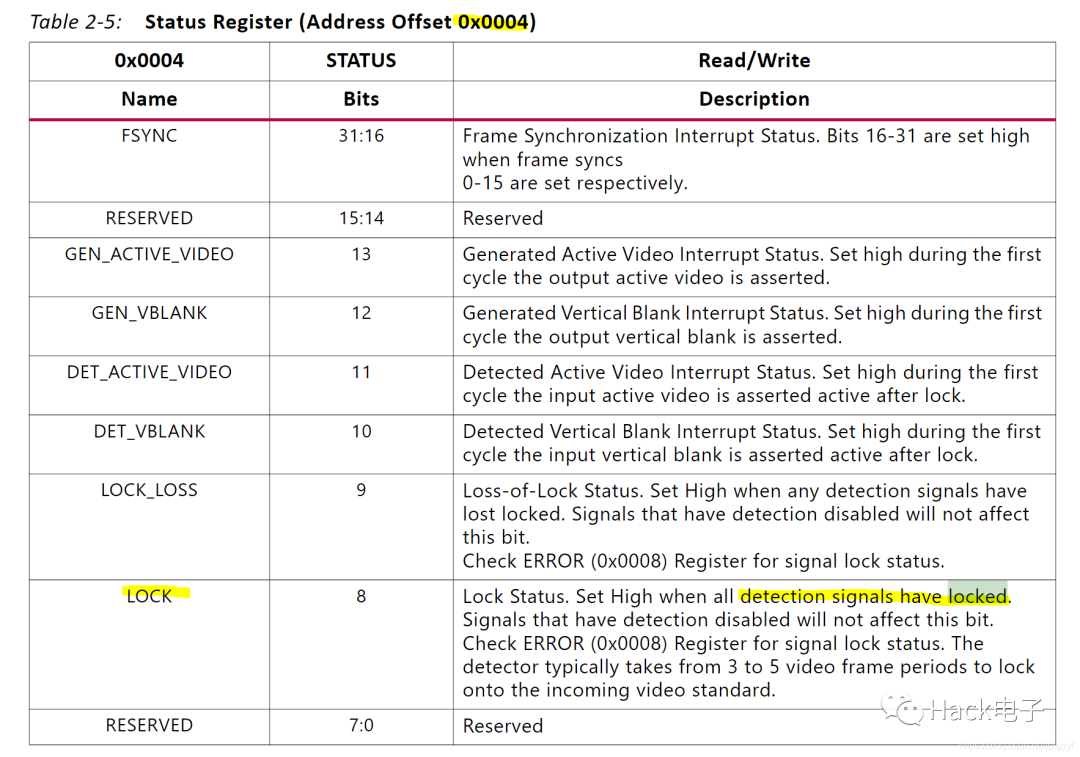

(2)这里我把axis_enable接了vtc的INTC中的第8位(Detect Locked信号),是参考文档上的描述,这样更准确。

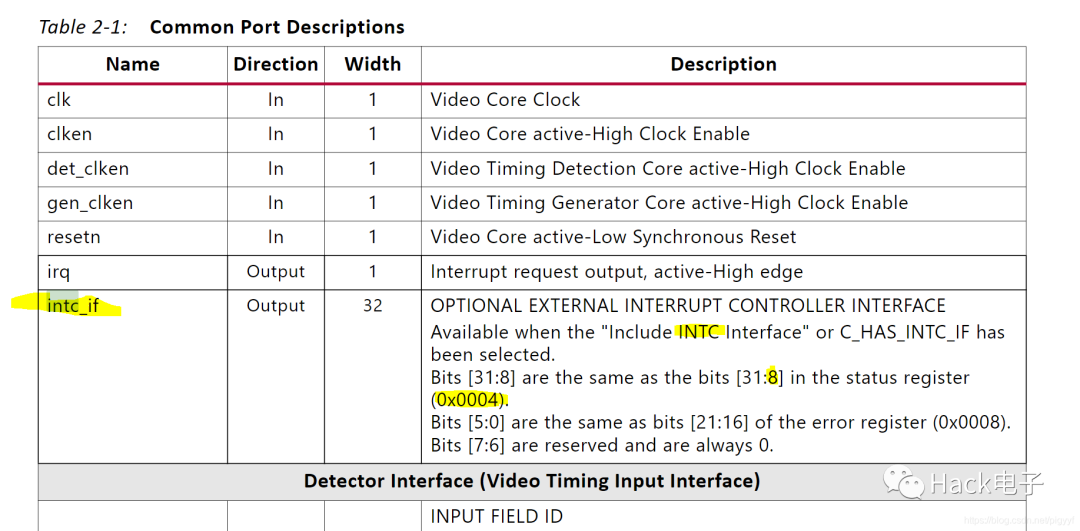

(pg043 pp10)

(pg016 pp12)

(pg016 pp25)

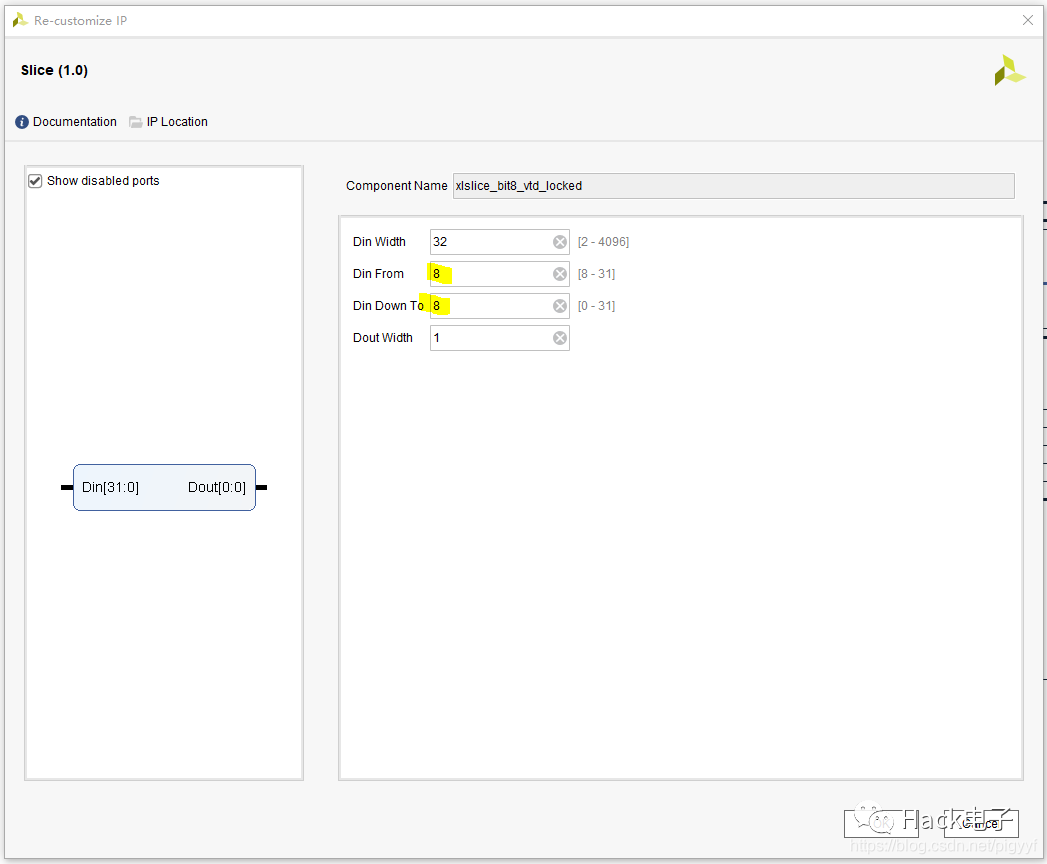

(3)去INTC中第8位出来的IP使用slice来截取。IP配置如下

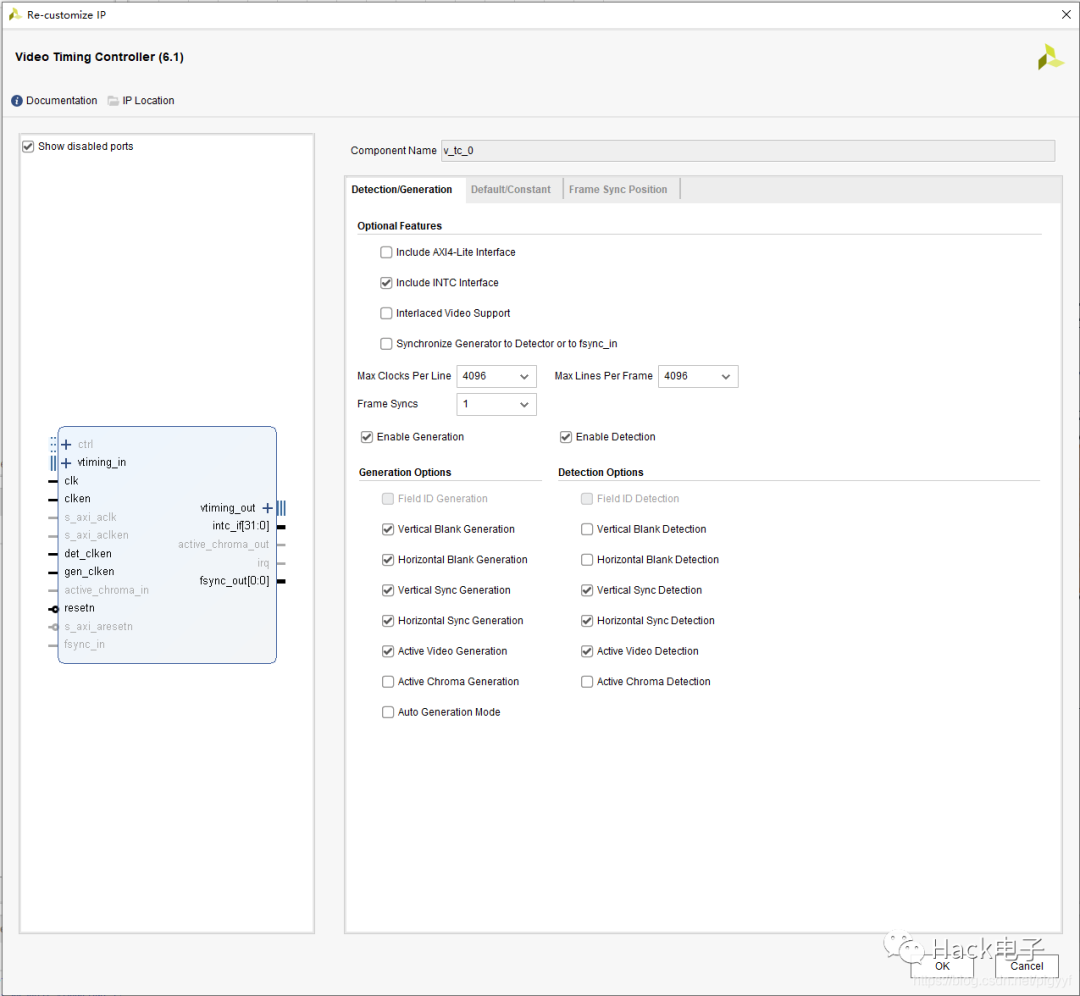

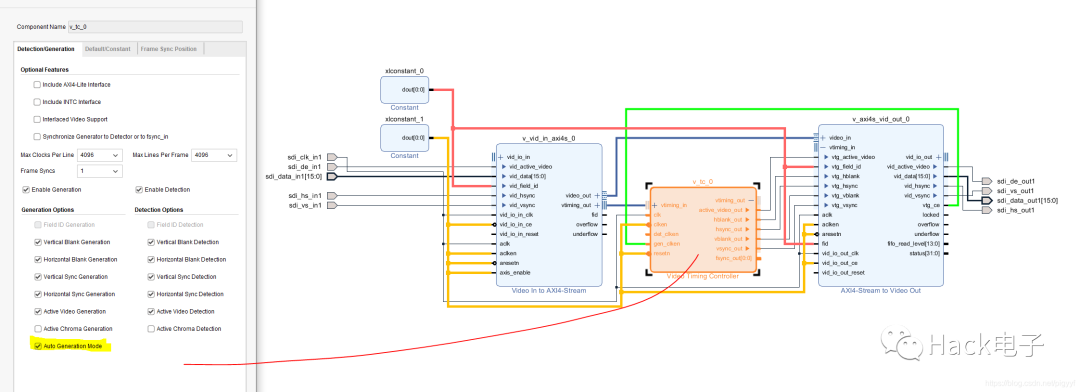

3. Video Timing Controller的配置

(1)注意synchronize generator to detector or fsync_in前的“勾"不能选! 选了就会显示输出不了。如果想让输入和输出同步,怎么弄我还没有搞明白,后续在研究。

(2) 不能选输入和输出同步,意味着enable detector可以不选,因此detect video in 的timing实际上没有必要。也就意味着video in的timing_out可以不用接到vtc的timing_in上。实测也是工作的。

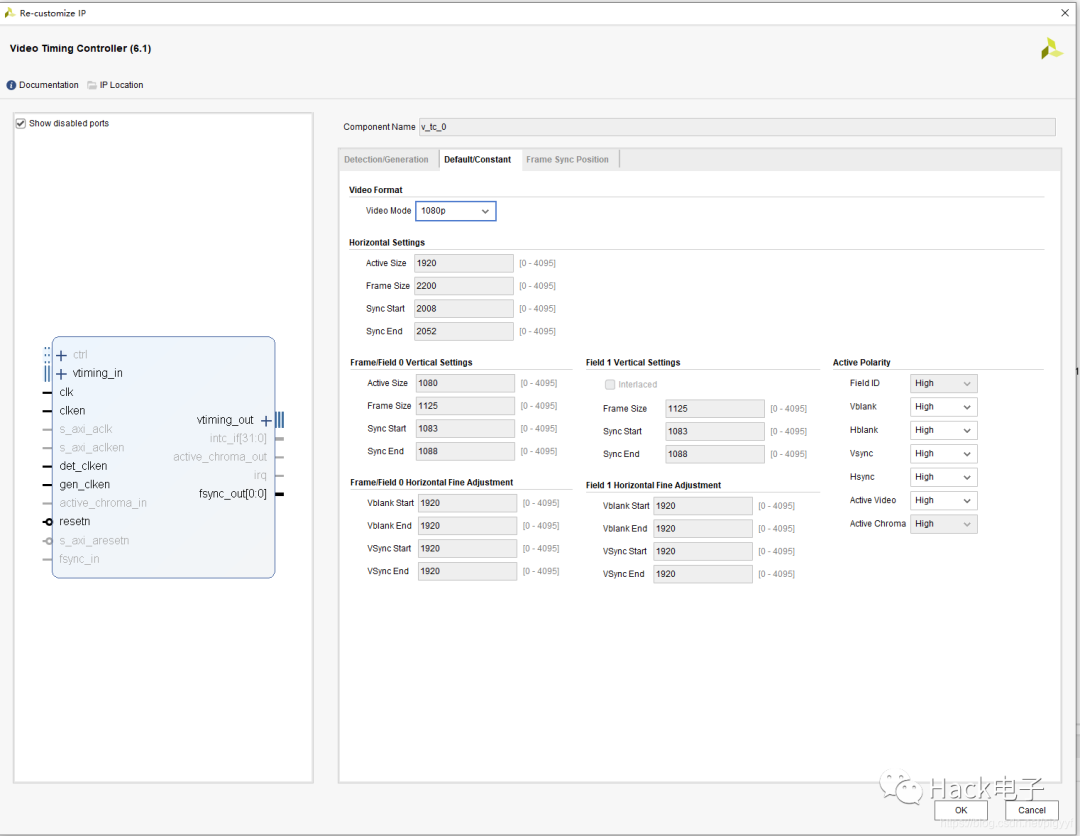

(3)第二页,选1080p的时序模式

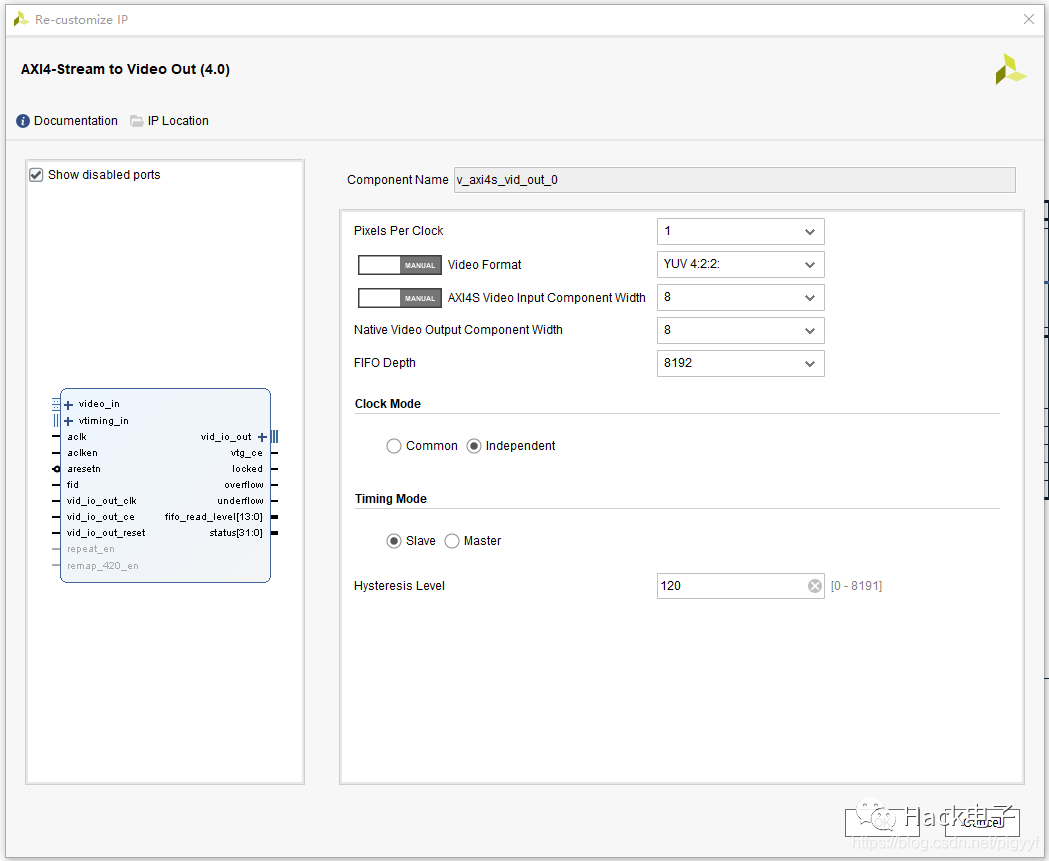

4. AXI4-stream to Video Out的配置

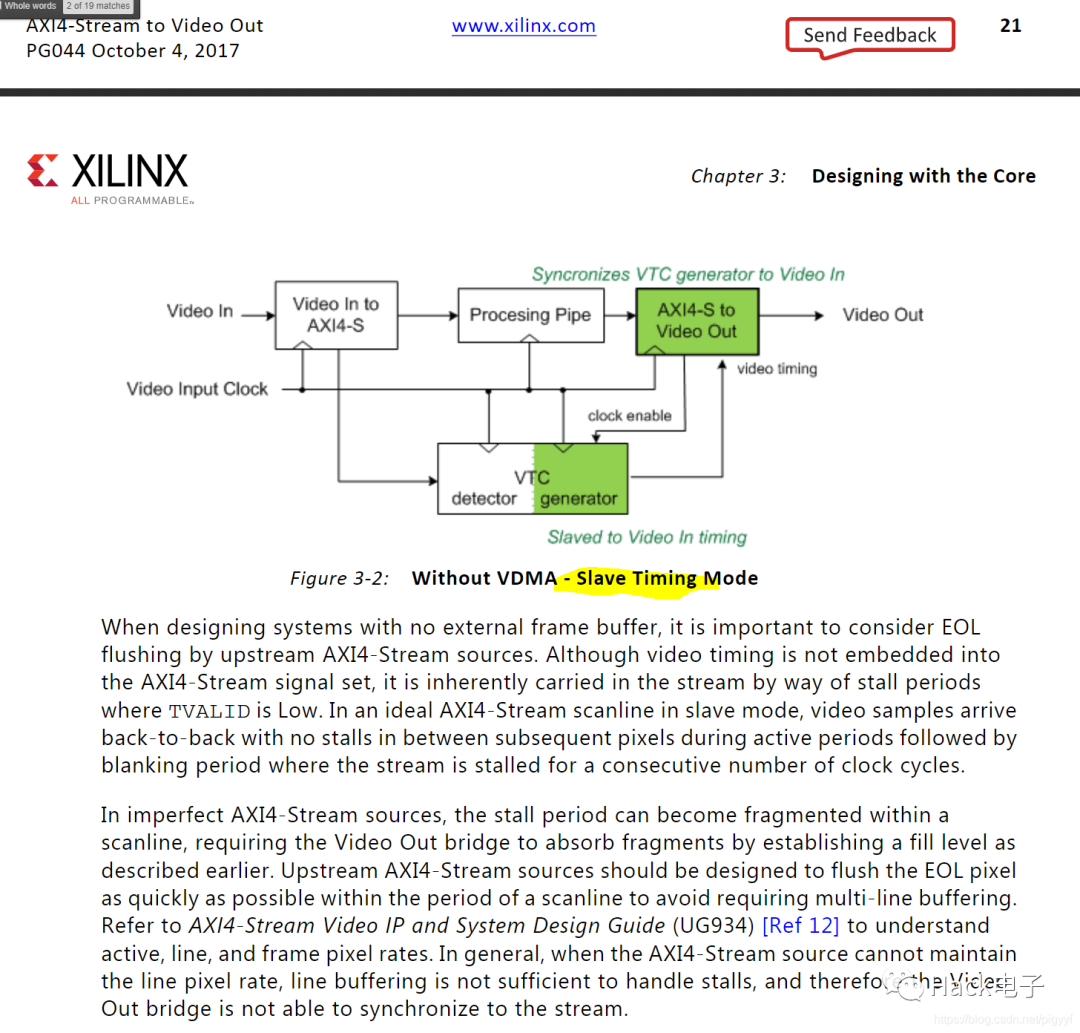

(1)这种没有VDMA的框架下timing mode要选slave模式。

为什么,具体解释参见pg044, pp21-22

换言之,如果包含VDMA的框架,这里要选master模式。

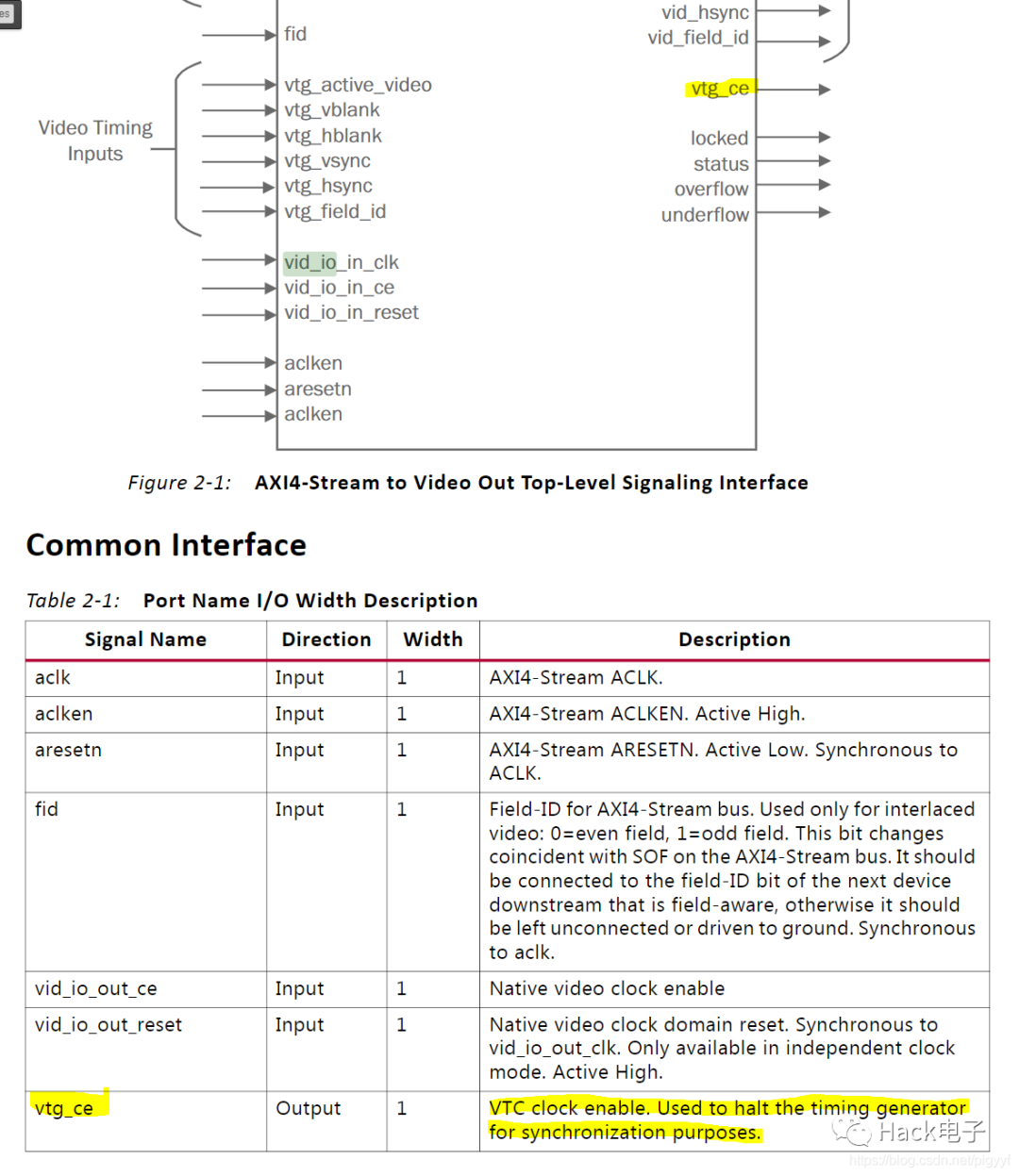

(2)vid_out输出管脚vtg_ce必须要接到vtc的gen_clken上,它的作用是slave模式下保证vid_out和vtc的同步。

(pg044 pp10)

5. aclken,reset等等为安全稳妥起见,连接按图上拉或下拉即可。

6.实测运行,显示正常。

补记:

1.我又精简了一下,vtc没有使能detector的模式,实测OK

2. 又测试了下vtc使能detector,并且使能了auto generation mode,测试也显示正常。(注意,这次意外的忘了连det_clken,也没什么异常)

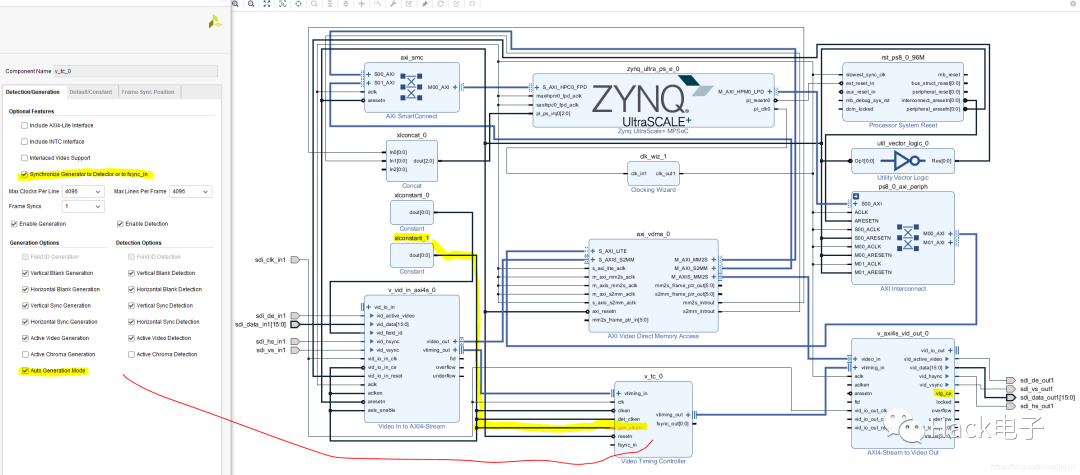

3. 关于synchronize detector to generater选项何时可以用的思考。

前面测试了无VMDA的video_out工作在slave模式,时序同步是通过vtc_ce反向传给gen_clken完成的。这种情形不允许,generator与detector同步。

那么在有VDMA参与的video out工作在master模式下呢?我返回了一个包含VDMA的工程,我们把vtc_ce反馈撤掉(之前也是把vtc_ce接到gen_clken的),gen_clken常拉高置1,此时再给vtc设置为synchronize detector to generater 打勾。这种情形下,输出可以与输入信号同步了,实测成功,显示正常。这样就实现了输出与输入的帧频同步了。

原文标题:不使用VDMA情况下使用AXI4总线实现视频输入输出(低延迟首选)

审核编辑:汤梓红

-

NVMe IP之AXI4总线分析2025-06-02 6197

-

看看在SpinalHDL中AXI4总线互联IP的设计2022-08-02 3299

-

AXI4接口协议的基础知识2020-09-23 7236

-

一文详解ZYNQ中的DMA与AXI4总线2020-09-24 7559

-

ZYNQ中DMA与AXI4总线2020-11-02 5294

-

深入AXI4总线一握手机制2021-03-17 1269

-

深入 AXI4总线 (四):RAM 读取实战2022-02-07 1034

-

AXI4 、 AXI4-Lite 、AXI4-Stream接口2022-07-04 10932

-

AXI3与AXI4写响应的依赖区别2023-03-30 2072

-

FPGA AXI4协议学习笔记(二)2023-05-24 3037

-

Xilinx FPGA AXI4总线(一)介绍【AXI4】【AXI4-Lite】【AXI-Stream】2023-06-21 3251

-

漫谈AMBA总线-AXI4协议的基本介绍2024-01-17 4554

-

FPGA通过AXI总线读写DDR3实现方式2024-04-18 2677

-

SoC设计中总线协议AXI4与AXI3的主要区别详解2024-05-10 13971

-

AMBA AXI4接口协议概述2024-10-28 1748

全部0条评论

快来发表一下你的评论吧 !