jitter的关键术语和参数

接口/时钟/PLL

描述

1. 背景

时钟电路是芯片中最基础的电路,时钟电路性能的好坏关乎SoC中所有电路能否达到预期目标,例如:计算核(CPU/GPU/NPU)的主频,DDR的带宽,高速接口(PCIE)的带宽等。对于时钟电路,其最关键的性能指标就是jitter,jitter会影响数字电路的频率,影响SerDes的误码率。因此,在设计初期合理的考虑各个模块的时钟jitter尤为重要。

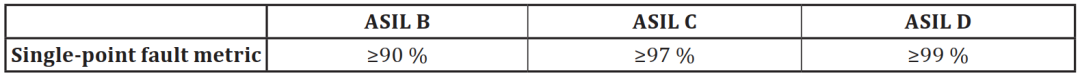

对于汽车芯片,由于其需要具备安全机制检测故障的能力,因此对jitter有更高的要求。ISO26262中做了明确的汽车安全完整性等级(ASIL)规定,由低到高分别为ASIL A、ASIL B、ASIL C和ASIL D四个级别,对应的单点故障率如Table 1所示。

Table 1. Possible source for the derivation of the target “single-point fault metric” value

同时,由于座舱芯片和ADS芯片对算力需求越来越大,进而导致芯片面积和功耗也越来越大。大面积和高功耗对芯片的时钟设计带来巨大挑战:长距离的时钟路径和电源噪声会使得时钟jitter发生显著恶化,使得整芯片性能发生恶化。因此,分析出各种jitter对芯片性能的影响进而对芯片进行精细化设计尤为重要。

对于真实物理世界的时钟源,包括PLL、DLL、晶振、甚至是函数发生器,它们的时钟输出周期都不可能是一个单点的固定值。所有的真实时钟源的输出周期都是随时间而变化的,即同一个时钟,它的此刻时钟周期的边沿与它下一个时钟周期的边沿都是会发生变化的。这种时钟周期的变化称为jitter。

本文详细描述了一些关于jitter的关键术语和参数,它可以帮助我们深入的理解时钟最重要的参数,从而根据不同的应用场景合理的选择PLL和设计对应的时钟电路。

2. 应用分析

不同的应用对jitter的需求是不同的。

2.1 数字系统

在数字系统中,时钟定义了电路可以完成一定工作量的时间段。由于每个基本单元的工作都需要一段时间(例如逻辑门的固有延迟、高低电平转换的延迟和线延迟等)来完成,因此数字系统的时钟频率主要是受逻辑复杂度以及组合电路的逻辑深度限制的。

在数字系统中,时钟边沿决定了每个基本单元的开始和结束时间。当jitter改变了时钟边沿从而导致时钟周期变短时,每个基本单元的有效工作时间也会变短。

Period jitter是用来衡量单个时钟周期变化的指标,它也是描述每个基本单元可用时间的最佳指标。这个指标是数字系统的设计人员最应该密切关注的指标。

2.2 RF系统

RF系统的本振时钟是通常用于混频器中,用于生产发射信号或者下变频的接收信号以进行后续处理。

在这种场景下,accumulated jitter(也叫long-term jitter)可以用来衡量系统中的相位噪声。当混频器工作时,源信号会乘以本振时钟来进行上变频或下变频,得到目标信号的频谱为源信号频谱与本振时钟频谱的乘积。本振时钟中的任何相位噪声都会在输出端产生不想要的信号并混在目标信号中,从而降低系统的信噪比(SNR)。

2.3 ADC/DAC

在模数转换器(ADC)和数模转换器(DAC)中,时钟决定了信号采样时间。如果jitter导致采样时间偏离了理想采样时间,这就会导致采样到的信号值相比于理想的信号值发生变化。

ADC和DAC对信号的采样的可以转换为信号与时钟乘积的模型。这就意味着该系统信噪比(SNR)的退化模型与2.2节描述的场景相同,因此对于ADC和DAC来说,accumulated jitter依然是最重要的参数。

2.4 SerDes系统

当使用Serdes发送或者接收串行bit流时,时钟是用于对传输的数据进行编码,并将时钟信息嵌入到传输的数据中。接收器会从传输的比特流中分离出单独的时钟,用于对数据进行采样和捕捉。在该系统中,accumulated jitter决定了bit到达与采样之间的时间差,因此它是最重要的。如果整个系统的jitter太大,那就会导致采样到错误的bit。

3. Jitter的随机性与确定性

在测量jitter时,需要将多个周期一并考虑进来,从而从统计学的角度来了解整体的性能。对于RF、ADC/DAC和SerDes等系统,从统计数据中可以直接得到设计人员需要的重要信息。而对于数字系统,统计数据可以给出时钟周期小于目标周期的概率,这是时序收敛的关键指标。

3.1 Random Jitter

PLL内产生的jitter主要是带宽有限的random jitter。此外,PLL电源的的白噪声也会转换为PLL输出上的random jitter。

Random jitter来自真正的随机行为,例如热噪声和闪烁噪声。random jitter也可能由电源噪声引起,该电源噪声也来源于随机行为,例如SoC电源,尤其是PLL电源中的热噪声。

Random jitter,顾名思义,在任何周期中都是无法预测的。只能预测一组时钟的统计特性。其中,最常用于RJ测量的是正态分布的标准差,也叫RMS jitter。

Figure 1. Normal Distribution

Figure 1是jitter的正态分布,通常用于描述jitter的概率。PLL产生的random jitter都符合正态分布。

对于1-6倍标准差(σ),Figure 1标示了时钟边沿超出几倍σ的概率。从图中可以看出,随着σ的倍数增大,概率很快地接近零,但是永远不会到达零。例如,时钟边沿超过1倍σ的概率为31.7%,但超过6σ的概率为1.97x10-9,这个概率非常小,以至于在几乎所有分析案例中,我们都可以将其近似为零。

需要注意的是,现代数字系统的设计通常要求非常严格,例如致信区间要处于5σ或6σ之间。串行通信标准通常具有更严格的标准,通常会指定更大倍数的来计算peak jitter。

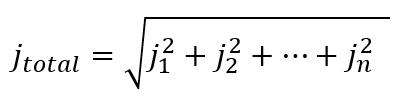

如果存在多个不相关的random jitter源,则需要以RMS的方式对它们进行汇总。因此得到组合后的:

其中:

jtotal是总的jitter

jk for k=1…n是单独的、不相关的jitter分量

3.2 Deterministic Jitter

Deterministic jitter是遵循已知模式的jitter。

在时钟输出中潜在的deterministic jitter源:

Spread Spectrum Clocking (SSC);

电源的确定性调制:如果SoC具有重复的高功率模式和低功率模式的切换,这可能会导致电源的确定性调整;

其他源的调制;

以确定性方式运行的任何其他机制。

Deterministic jitter的峰值可以直接测量。因为它是确定性的并且不依赖于出现的概率,所以测量的结果是绝对的。

例如,PLL的供电电压可能会存在500kHz的纹波,这是由于电源开关切换引起的。该电源的噪声分量将导致PLL输出具有deterministic period jitter,并且该jitter的峰值与输入电源的峰值波动成正比。在给定的时间内,电源电压与PLL输出时钟瞬时period jitter存在直接关系。随着电源电压的变化,PLL输出的周期变化将被视为deterministic jitter。

3.3 Random Jitter和Deterministic Jitter的组合

Random jitter和deterministic jitter只有峰值或者峰峰值可以组合在一起:

取给定σ的random jitter(Rj)

取deterministic jitter的峰值(Dj)

将两个峰值相加得到total jitter(Tj=Rj+Dj)

4 Jitter的定义与分类

4.1 Period Jitter

Period jitter是数字系统中最重要的jitter。它描述的是时钟周期与该时钟平均周期的偏差。

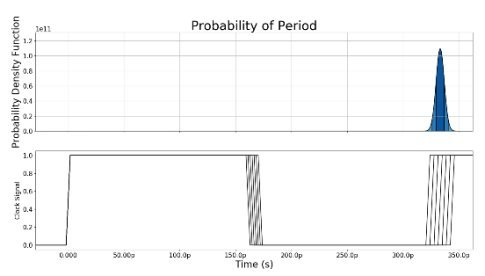

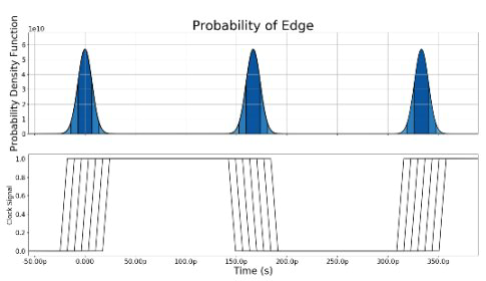

Figure 2. Period Jitter Example

Figure 2是3-GHz时钟的period jitter示例。绘制在下轴上的每个时钟周期与所有其他周期均不同。时钟周期开始时所有的上升沿均已对其,从而显示jitter带来的周期差异。时钟边沿差异遵循正态分布,如上轴所示。

在数学上,period jitter可以表示为:

jperiod = periodcurrent cycle-periodmean

其中:

jperiod是给定时钟周期的瞬时period jitter

periodcurrent cycle是当前时钟周期的瞬时周期

periodmean是被测量时钟的平均周期

Period jitter包含random jitter和deterministic jitter两个分量。这两个分量可以单独分析,但通常没必要这么做,因为在大多数应用中,唯一重要的参数是可能出现的最短周期。

在数字系统中,可能出现的最短周期就是数字逻辑可用的时间。

4.2 Cycle-to-Cycle Jitter

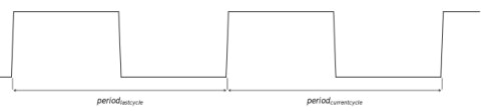

Cycle-to-cycle jitter表示两个相邻时钟周期间的变化,如Figure 3所示。

Figure 3. Cycle-to-Cycle Jitter Definition

数学上,cycle-to-cycle jitter可以表示为:

jcc = periodcurrent cycle-periodlast cycle

其中:

jcc 是给定时钟周期的瞬时cycle-to-cycle jitter

periodcurrent cycle是当前时钟周期的瞬时时钟周期

periodlast cycle是上一个时钟周期的瞬时时钟周期

虽然不同的应用对不同的jitter要求不同,但是通常cycle-to-cycle jitter并不常用,因为它与数字、RF、ADC/DAC或Serdes系统中的任何常用性能指标无关。

4.3 Accumulated Jitter

Accumulated jitter,也叫long-term jitter,是指多个时钟周期下给定时钟沿与理想时钟沿的偏差。这种偏差与period jitter不同,它是指在多个时钟周期上累计值。

Figure 4. Accumulated Jitter Definition

Figure 4显示了存在accumulated jitter的时钟信号。Accumulated jitter是多个周期内period jitter的累积。在实际系统中,我们只需要考虑特定带宽上的jitter,因此accumulated jitter会达到与时间无关的极限,不会变得无限大。

Accumulated jitter对于RF 系统、 ADCDAC、SerDes系统的时钟非常重要。Accumulated jitter是随机分量和确定性分量的总和。

-

请问CDCM6208 random jitter和total jitter各是什么含义?2024-11-12 525

-

吐血推荐:详解喷涂机器人的术语及关键参数2016-01-06 5722

-

运算放大器关键术语2009-04-27 468

-

JITTER ANALYSIS USING THE 54122010-07-08 512

-

Frequency agile jitter measure2010-07-15 781

-

Understanding Jitter and Wande2010-07-19 1160

-

Jitter Generation and Jitter M2010-07-21 838

-

什么是jitter,jitter是什么意思?2008-11-27 17387

-

固体继电器参数术语2009-07-25 692

-

用DSP实现抖动(Jitter)测量的方法2009-08-17 1454

-

Aperture Jitter Calculator for2009-09-18 2109

-

固体继电器参数术语大全2010-03-01 1019

-

光耦常用参数及术语2012-06-04 1173

-

基于示波器抖动分析的jitter分类及其特点2020-05-14 14227

-

物联网领域的关键术语2023-12-28 1899

全部0条评论

快来发表一下你的评论吧 !