华大电子MCU-CIU32F011x3、CIU32F031x5系统及存储器架构

电子说

描述

4. 系统及存储器架构

华大电子MCU CIU32F011x3、CIU32F031x5 器件是基于 ARM Cortex M0 处理器的 32 位通用微控制器存储器芯片。采用了哈佛结构,具有低中断延迟时间和低成本调试特性,而且高集成度和增强的特性使这颗处理器

适合于那些需要高性能和低功耗微控制器的市场领域。预先定义的存储器映射和高达 4GB 的存储空间,充分保证了系统的灵活性和可扩展性。

4.1. 系统架构

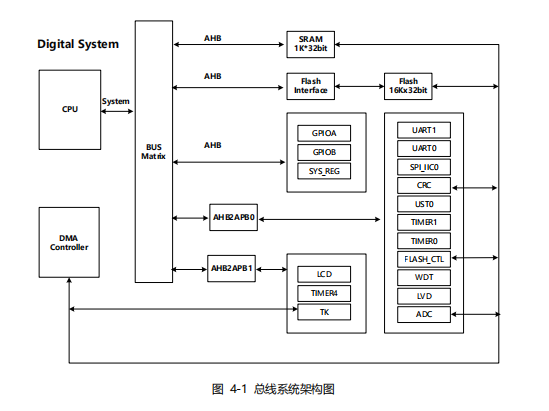

华大电子MCU CIU32F011x3、CIU32F031x5 器件采用 32 位多层总线结构,该结构可使系统中的多个主机和从机之间的并行通信成为可能。多层总线结构包括一个 AHB 互联矩阵、两个 AHB 总线和两个 APB 总线。AHB互联矩阵的互联关系接下来将进行说明。

CIU32F011x3、CIU32F031x5 主系统由以下两部分构成

• 2 个驱动单元

– CPU 内核系统总线(S-bus)

– DMA 总线

• 2 个存储单元

– 内部闪存存储器

– 内部 SRAM

系统总线

此总线连接 CPU 内核的系统总线(外设总线)到总线矩阵,总线矩阵协调着内核和各个高速部件间的访问。

DMA 控制器

此总线将 CPU 与各外设模块访问相联竞争,协调访问优先级,仲裁等。

总线矩阵(Bus Matrix)

• 总线矩阵管理着内核系统总线与各外设模块的访问仲裁,总线矩阵由主模块总线及从模块总线组成。

• AHB 外设通过总线矩阵与系统总线相连。

• AHB 到 APB 桥(AHB2APB bridges-APB)。

• AHB 到 APB 桥在 AHB 与 APB 总线间提供同步连接。

注:当对 APB 寄存器进行 8 位或者 16 位访问时,该访问会被自动转换成 32 位的访问;桥会自动将 16 位或者 8 位的数据扩展以配合 32 位的宽度。

4.2. 存储器映射

此 32 位处理器采用同一套总线来读取指令和加载/存储数据。指令代码和数据都位于相同的存储器地址空间,但在不同的地址范围。程序存储器,数据存储器,寄存器和 IO 端口都在同一个线性的 4GB 的地址空间之内。这是 32 位处理器的最大地址范围,因为它的地址总线宽度是 32 位。此外,为了降低不同客户在相同应用时的软件复杂度,存储映射是按 32 位处理器提供的规则预先定义的。在存储器映射表中,一部分地址空间由 32 位处理器的系统外设所占用,且不可更改。此外,其余部分地址空间可由芯片供应

商定义使用。CIU32F011x3、CIU32F031x5 器件的存储器映射表显示了 CIU32F011x3、CIU32F031x5器件的存储器映射,包括代码、SRAM、外设和其他预先定义的区域。简化了每个外设的地址译码。

审核编辑 黄昊宇

-

华大电子MCU CIU32M010、CIU32M030循环冗余校验计算单元及电源管理2023-06-20 1855

-

华大电子授权代理_MCU芯片CIU32L0_CIU32F0系列产品2023-02-10 2477

-

华大电子MCU-CIU32F011x3、CIU32F031x5通用输入输出2022-12-28 1796

-

华大电子MCU CIU32L061x8 系列特性分析2022-12-27 1325

-

华大电子MCU-CIU32L061x8产品特性2022-12-19 1594

-

华大电子MCU-CIU32F011x3、CIU32F031x5系统及存储器架构2022-11-11 1590

-

华大电子MCU-CIU32F011x3、CIU32F031x5电源管理2022-11-07 1342

-

华大电子MCU-CIU32F011x3、CIU32F031x5特点和简介2022-10-13 2314

全部0条评论

快来发表一下你的评论吧 !