浅析SystemVerilog中的枚举类型

描述

枚举类型定义了一组具有名称的值,在没有指定值时默认是int型数值。

enum {red, green, blue} light1, light2;

在上面的例子中,没有指定任何数据类型,因此使用默认的“int”数据类型。所以枚举类型light1和light2被定义为默认类型int的变量,其中包括三个成员:red, green, blue。由于没有指定各个含义的值,所以

red= 0,green= 1,blue= 2

再举一个例子

enum integer {IDLE, XX='x, S1='b01, S2='b10} state, next;

这里的数据类型是“integer”,这意味着可以将“x”和“z”值分配给枚举成员。

enum {bronze=3, silver, gold} medal;

以bronze = 3作为初始值。因此,silver等于4,gold等于5

enum {a=3, b=7, c} alphabet;

显式de为“a”和“b”赋值,因此,c将取b = 7后的值。所以c等于8,也就是说

enum {a=0, b=7, c, d=8} alphabet;

Synopsys – VCS:

Error-[ENUMDUPL] Duplicate labels in enum

The enum label 'd' has the value 4'd8 which is duplicate of enum label 'c' in the declared enum.

上面这种写法就会导致编译错误,因为c和d的值都等于8。

enum {a, b=7, c} alphabet;

“a”是第一个成员,它没有值。所以,a等于0。因此,

a = 0, b = 7, c = 8

enum bit [3:0] {red=‘h13, green, blue} color;

Synopsys – VCS:

Error-[ENUMRANGE] Enum label outside value range

The enum label 'red' has the value 'h00000013 which is outside the range of

the base type of the declared enum, which is 4 bit unsigned.

上面这个示例也会导致编译错误,因为red=‘h13超出了 bit[3:0]所能够表示的最大值('hF) 。修改成下面的写法就没有问题了。

enum bit [3:0] {red=‘d13, green, blue} color;

此时

red = 13, green = 14, and blue = 15

枚举类型在设计有限状态机时特别有用。例如,

你可以定义一个枚举类型来描述状态机的状态:

enum logic [1:0] { IDLE = 2’b00,

READ = 2’b01,

WRITE = 2’b10,

RMW = 2’b11,

ILLEGAL = ‘x } current_state,next_state;

因为类型是“logic”,所以可以将未知的('x)值分配给enum成员。这样的'x赋值对于仿真比较非常有用,而对于综合工具而言就进行合适的优化。该枚举可以在状态机编码中使用,如下所示:

always @(posedge clk, negedge reset)

if (!reset)

current_state <= IDLE;

else

current_state = next_state;

always @* begin

…

case (current_state)

IDLE : if (rdy) next_state = READ;

READ : if (go) next_state = WRITE;

…

endcase

end

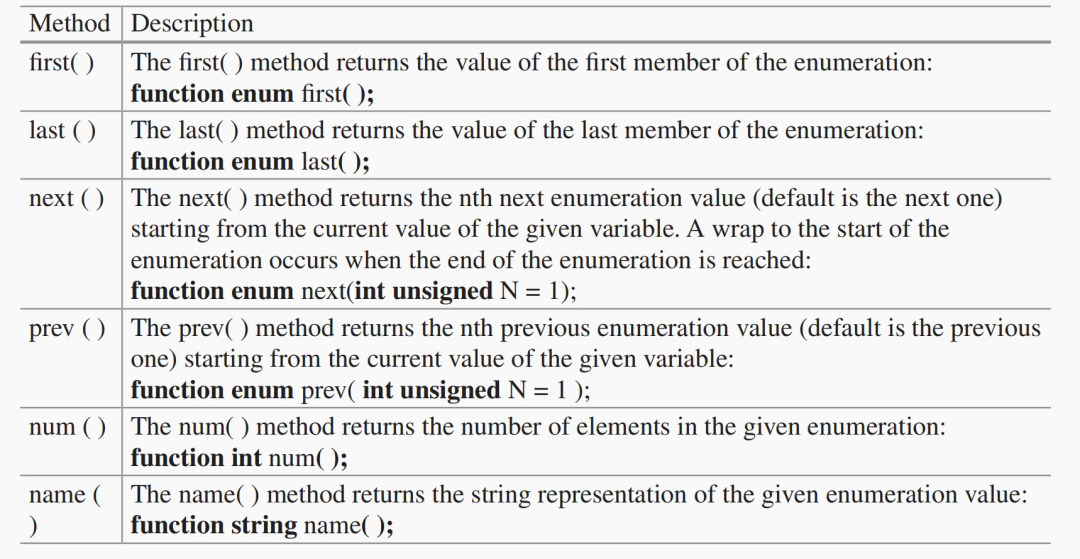

Enumerated-Type Methods

枚举类型的变量提供了很多内建的方法,方便提取枚举类型成员的值。

module enum_methods;

typedef enum { red, green, blue, yellow } Colors;

Colors c;

initial begin

$display("Number of members in Colors = %0d",c.num);

c = c.frst( );

$display("First member # = %0d",c);

c = c.next(2);

$display("c = %0d",c);

c = c.last ( );

$display("Last member # = %0d",c);

$display( "%s : %0d", c.name, c );

end

endmodule

Simulation log:

run -all; # KERNEL: Number of members in Colors = 4 # KERNEL: First member # = 0 # KERNEL: c = 2 # KERNEL: Last member # = 3 # KERNEL: yellow : 3 # KERNEL: Simulation has fnished. There are no more test vectors to simulate. exit

在这个例子中,我们定义了一个

typedef enum {red, green, blue, yellow} Colors;

Colors有四个成员,

red= 0, green= 1, blue= 2, yellow= 3

我们首先使用“num()”方法显示枚举中的成员数量。

枚举中有四名成员。所以,显示日志显示

Number of members in Colors = 4.

然后使用方法“frst()”获取第一个成员的值。第一个成员是值为0的“red”,因此打印显示

First member = 0.

然后我们使用“next(2)”,会获取后面第2个值2.

接下来,我们通过last()获得枚举类型最后一个成员的值3

Last member # = 3

下面是另一个简单的例子:

module datatype1;

enum bit [3:0] {red, green, blue=5} color;

int i1;

initial

begin

i1 = green;

$display ("color.name = %s", color.name);

$display ("red=%s green=%d blue=%d",color.

name,green,blue); //OK

$display ("red=%d green=%d blue=%d",red,green,blue); //OK

end

endmodule

Simulation log:

i1 = 1 color.name = red red=red green= 1 blue= 5 red= 0 green= 1 blue= 5 V C S S i m u l a t i o n R e p o r t

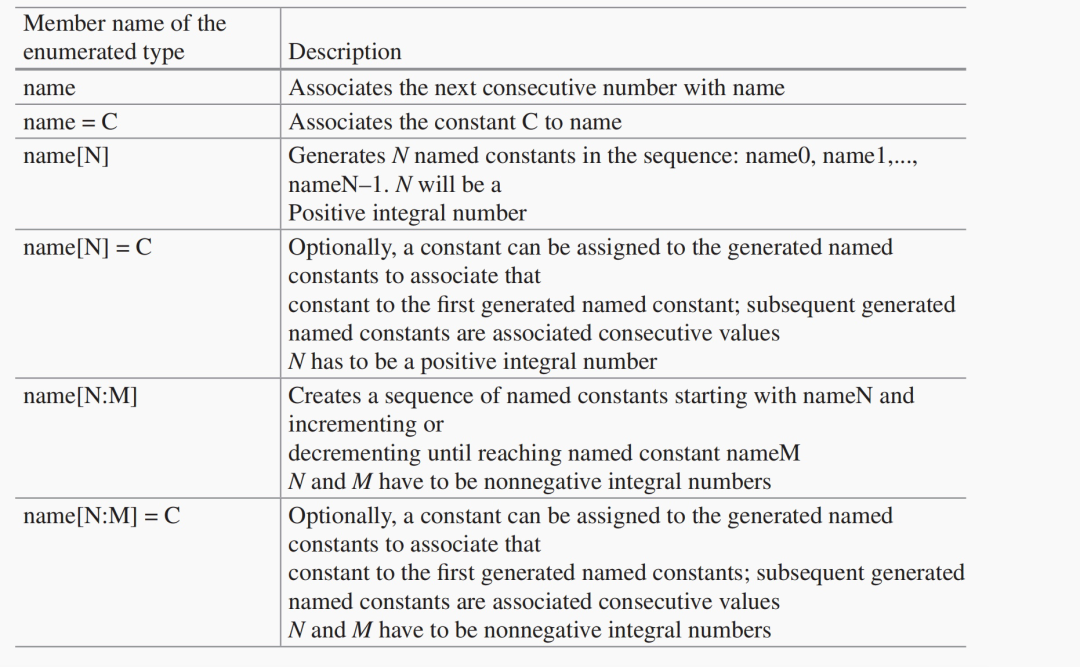

Enumerated Type with Ranges

枚举类型的成员可以指定范围

module datatype1;

typedef enum { read=10, write[5], intr[6:8] } cycle;

enum { readreg[2] = 1, writereg[2:4] = 10 } reg0;

initial

begin

$display ("read=%0d

", read);

$display ("write0=%0d write1=%0d write2=%0d write3=%0d

write4=%0d

", write0,write1,write2,write3,write4);

$display ("intr6=%0d, intr7=%0d intr8=%0d

",intr6,

intr7, intr8);

$display ("readreg0=%0d readreg1=%0d

",readreg0,

readreg1);

$display ("writereg2=%0d writereg3=%0d writereg4=%0d

n",writereg2, writereg3, writereg4);

end

endmodule

typedef enum { read=10, write[5], intr[6:8] } cycle;

定义一个包含三个成员的枚举类型“cycle”。第一个“read”;然后是一系列5个writes,分别是“write0”、“write1”、“write2”、“write3”、“write4”;然后是三个“intr”的,即“intr6”、“intr7”和“intr8”。

类似的,

enum { readreg[2] = 1, writereg[2:4] = 10 } reg0;

定义一个包含两个成员:

readreg0和readreg1,

writereg2, writereg3和writereg4。

下面是仿真log

read=10 write0=11 write1=12 write2=13 write3=14 write4=15 intr6=16, intr7=17 intr8=18 readreg0=1 readreg1=2 writereg2=10 writereg3=11 writereg4=12 V C S S i m u l a t i o n R e p o r t

审核编辑:刘清

-

枚举类型的讲解2025-12-08 118

-

枚举有多大?c语言枚举end的作用是什么?2024-01-19 1425

-

如何在Go中给GORM模型添加枚举类型2023-11-28 2315

-

使用枚举类型表示状态机进入死循环2023-11-07 1918

-

Java枚举的特点及用法2023-09-30 2629

-

枚举类型的简单扩展学习2023-05-25 1287

-

SystemVerilog中至关重要的的数据类型2023-01-21 1505

-

SystemVerilog中的struct2022-11-07 3449

-

SystemVerilog中$cast的应用2022-10-17 4130

-

SystemVerilog中枚举类型的使用建议2022-09-01 2741

-

数字硬件建模SystemVerilog-枚举数据类型2022-07-01 3071

-

go语言枚举类型怎么用2021-09-02 6059

-

枚举是C语言中的一种基本数据类型2018-09-25 9322

-

深入理解java枚举类型enum用法2017-09-27 1666

全部0条评论

快来发表一下你的评论吧 !