一个基本的pad library设计方案

描述

每当我们做好了core的电路和版图,下一步就是设计pad ring了。对于第一次接触pad ring的同学来说,这个概念可能会有点陌生。

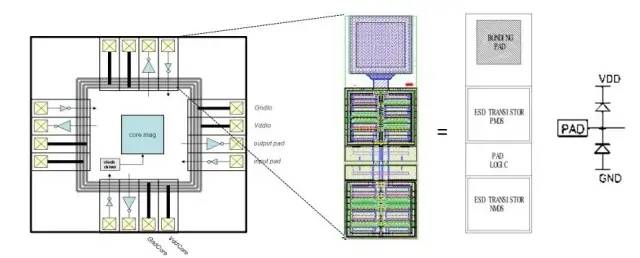

IO总的来说由两部分组成,一个是PAD,一个是电路。电路又分为pre 和 post。

PAD的作用是为了封装的时候连接金线。因此,为了防止金线短路,要求PAD之间要有最小距离,具体数值要看你的封装形式。

电路的作用有几方面:ESD保护,level shifter,施密特触发器等等。还有提供电源环路。

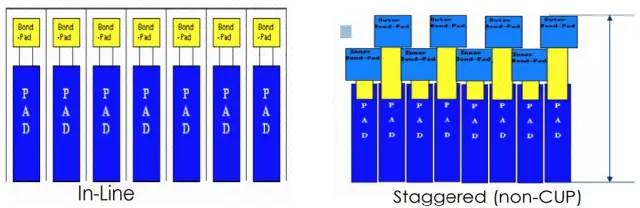

二者合在一起构一个IO(也就是I/O pad),有的时候PAD和电路是分开,stagger就是这种情况,在IO limiter的情况下,为了节省面积,将PAD分成两排甚至三排交错的排列,但是电路必须是在一条直线上的(因为电源环路的需求)。

Bonding pad是连接芯片和封装线的地方,ESD保护电路一般包括一对很大的反偏的PMOS,NMOS

作者君的珍藏,之前用电子显微镜查看引脚是否有短接,每个打孔的地方就是上图里面bonding pad

一个基本的pad library,应该可以提供如下几种pad:

给pad供电的pad,例如:PAD_VDD, PAD_VSS;

给core供电的pad,例如:VDD, VSS; (如果存在多个VDD domain, 还有AVDD, AVSS,之类的pad)

模拟信号的pad,例如ANIN (analog的pad一般就是一块铁片,有的vendor推荐用户可以自己基于要求自己再加上一定的ESD保护电路)

数字信号的pad,一般有input和output的区别,里面还有包括level shifter,buffers之类的数字电路(作者君用的不多,这里不展开说明了)。

建议设计pad ring之前,先去读一下vendor的文档,文档一般会说明各种类型的pad的用法,还有各种注意事项。不同的vendor提供的pad library不一样,所以有时候还是谨慎一点。

比如作者君最近用的一个pad library,里面有一种特定的提供PAD_VDD的pad,这个pad起到了类似POR的作用,它自己称之为POC(power on control)。这个pad会监控各个VDD的上升情况,只有当PAD_VDD, VDD之类的电源都基本上稳定了,它才会让core被最终供电。同时,文档里面还写了VDD的上升速度不可以太快(小于2us)之类的要求。(其实写到这里,作者君想到core的transient仿真里面,也需要模拟这个VDD的上升过程)

一般来说,pad ring会设计成一个方形或者矩形,这样给pad 供电的PAD_VDD, PAD_VSS可以比较均匀的分布在pad ring里面。当然,有时候遇到电路里面有高压的模块,可能不能share整个pad ring,那么pad ring就可能只有方形的三面,也是合理的。

相邻的pad之间需要隔开还是可以紧密挨着,主要是取决于最后封装时候的要求。举个例子,比如每个pad 的宽度是50um,但是封装引脚的最小距离是80um,那么相邻的pad之间就需要加filler(一种特定的cell,里面的PAD_VDD, PAD_VSS是连续的)同时,每个转角处还有专门的Corner cell,也是保证了pad ring里面ESD相关的信号的连续性。

首先需要确定的是关键的信号pad的位置,比如“尽量缩短走线长度”,让pad靠近layout core里面的信号pin的位置。(举个例子,如果做的test chip的core不大,可以选择core的位置靠近pad,不一定要正好在pad ring的正中间)。独立的敏感信号比如clock或者bidirectional pin与其他的switching pad之间,可以加入power或者ground的pads隔开,原理类似layout里面的signal shielding。

几个相邻的pad其实可以共享一个封装引脚pin(比如几根金线从几个pad上连到同一个封装pin上面),因为封装pin可以承受的电流一般大于pad的电流(比如一个pad电流最大是30mA)。同时,bonding wire有寄生电感,而电源上的变化电流可能会很大,并联很多条boding wire等于减小了寄生电感。

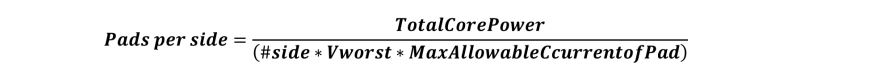

在可能的前提下,尽量多放power pad(可以减小bonding wire的弹跳效应),并让power pad均匀分布。然后是确定所需的电源pad的数量。用下面的公式粗略估计一下,比如总的电流是120mA,然后pad ring的四条边都加上VDD和VSS的pad,每个vdd pad的最大电流是30mA,如果Vworst和core power里面的电源电压一样大,那么每边一个pad就足够了。如果这两个电压值不一样,则应该增加vdd pad的数量。

VDD/VSS pad的数量计算

当然,如果面积有限,单层的inline pad ring放不下,还可以使用staggered的方式,也就是下面右图里面那种交叉摆放的方式。

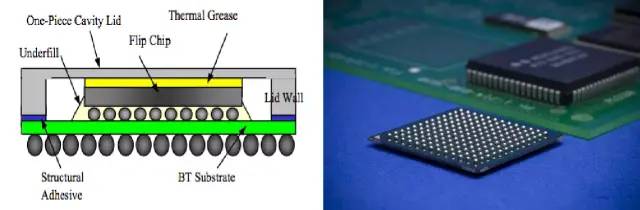

最后,多说几句package的基础知识,除了常见的dual-flat no-leads (DFN),dual in-line package (DIP)这些封装,现在还有Flip Chip with RDL,其中用到了一层Redistribution Layer (RDL),也就没有上面那些封装里面的金线了。对于超大规模的电路,Flip Chip现在已经很常见了。

传统封装方式

flip chip封装

审核编辑:刘清

-

创建一个Library工程2025-10-20 188

-

创建一个PLC设计方案2009-12-03 4743

-

【资料分享】STM32设计方案与示例分享 第一波2014-03-12 10993

-

求一个51或32的旋转LED设计方案2015-07-20 3778

-

求一个用单片机控制小车的设计方案2015-12-29 3999

-

STM32设计方案与示例分享2018-09-03 3698

-

希望提供一个信号源的设计方案或推荐一款DDS芯片?2018-10-11 3592

-

买一个免驱USB摄像头的pcb设计方案,包含具体的电路2019-08-08 2496

-

求一个基于DDC芯片的接口设计方案2021-04-20 1412

-

萌新求助,求一个变频调速恒压供药设计方案2021-11-04 1612

-

分享一个不错的Jlink下载器设计方案2022-01-19 1081

-

一个全自动洗衣机的设计方案2023-04-21 1458

-

并网逆变器的设计方案2016-01-11 1229

-

大联大世平集团推出基于NXP产品的无死角消毒触碰界面设计方案2021-06-07 3486

-

YS-TP035触摸PAD键盘方案2021-11-05 2759

全部0条评论

快来发表一下你的评论吧 !