CUP缓存(L1、L2、L3)是什么

处理器/DSP

描述

缓存(L1、L2、L3)是什么?

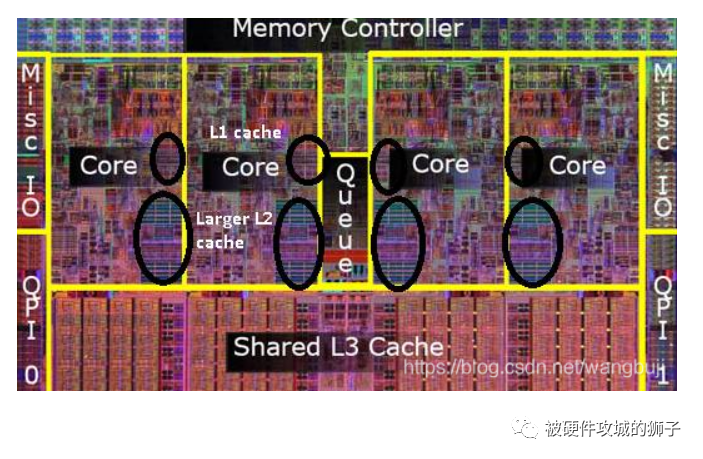

以近代CPU的视角来说,三级缓存(包括L1一级缓存、L2二级缓存、L3三级缓存)都是集成在CPU内的缓存,它们的作用都是作为CPU与主内存之间的高速数据缓冲区,L1最靠近CPU核心;L2其次;L3再次。运行速度方面:L1最快、L2次快、L3最慢;容量大小方面:L1最小、L2较大、L3最大。CPU会先在最快的L1中寻找需要的数据,找不到再去找次快的L2,还找不到再去找L3,L3都没有那就只能去内存找了。

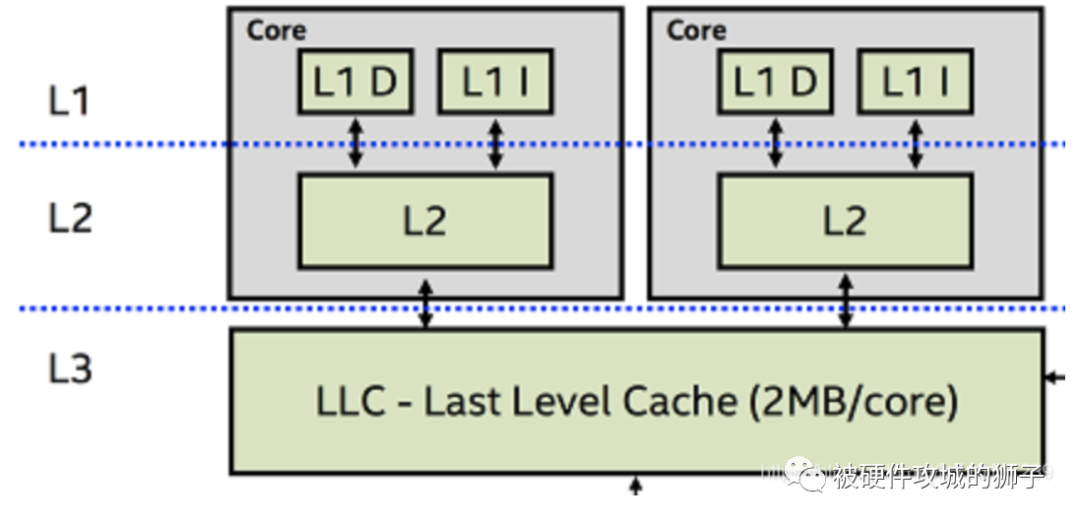

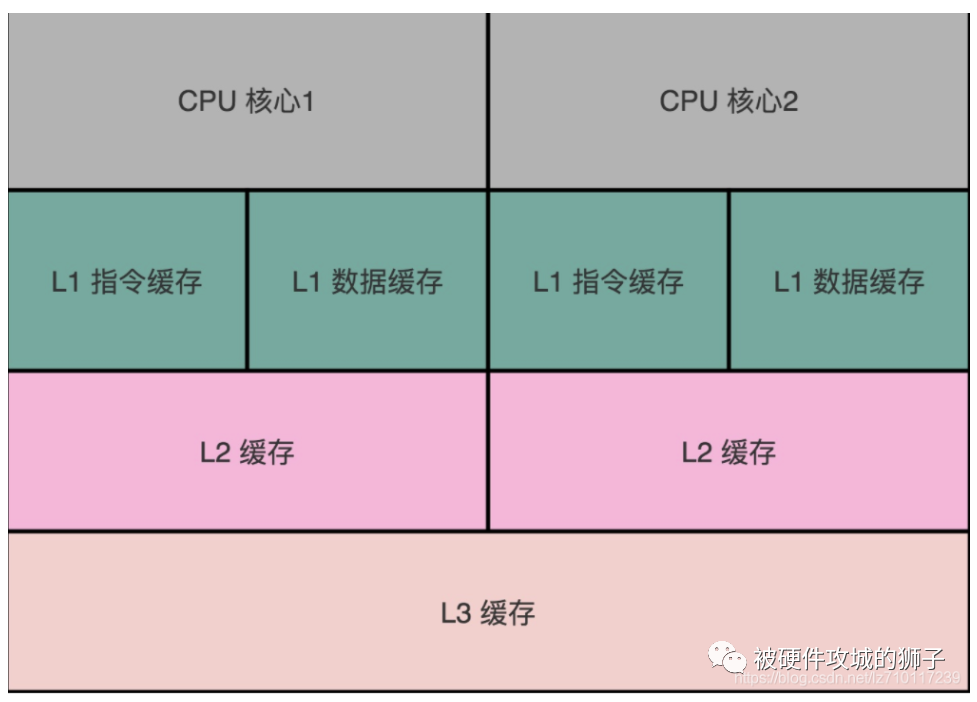

L1和L2cache是每个cpu核独享的,L3cache是多个cpu核共享。L1cache中又分为L1D(L1 Data Cahce)和L1I(L1 Instruction Cache)

一级缓存(L1 Cache)

一级缓存这个名词出现应该是在Intel公司Pentium处理器时代把缓存开始分类的时候,当时在CPU内部集成的CPU缓存已经不能满足整机的性能需求,而制造工艺上的限制不能在CPU内部大幅提高缓存的数量,所以出现了集成在主板上的缓存,当时人们把CPU内部集成的CPU缓存成为一级缓存,在CPU外部主板上的缓存称为二级缓存。

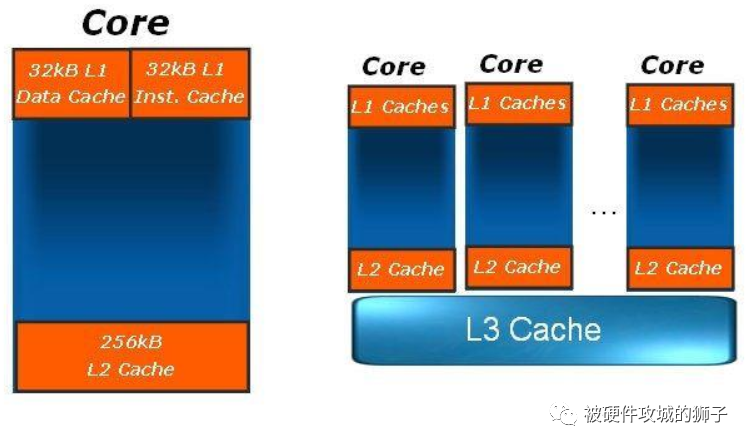

而一级缓存其实还分为一级数据缓存(Data Cache,D-Cache,L1d)和一级指令缓存(Instruction Cache,I-Cache,L1i),分别用于存放数据及执行数据的指令解码,两者可同时被CPU访问,减少了CPU多核心、多线程争用缓存造成的冲突,提高了处理器的效能。一般CPU的L1i和L1d具备相同的容量,例如I7-8700K的L1即为32KB+32KB。

二级缓存(L2 Cache)

随着CPU制造工艺的发展,本来处于CPU外部的二级缓存也可以轻易地集成进CPU内部,这种时候再用缓存是否处于CPU内部来判断一二级缓存已经不再确切。集成进CPU的L2二级缓存运行速率渐渐可以跟上CPU的运行速度了,,其主要作用为当CPU在L1中没读取到所需要的数据时再把数据展示给CPU筛选(CPU未命中L1的情况下继续在L2寻求命中,缓存命中的工作原理我们稍后再讲)。

L2二级缓存比L1一级缓存的容量要更大,但是L2的速率要更慢,为什么呢?首先L2比L1要更远离CPU核心,L1是最靠近CPU核心的缓存,CPU需要读取L2的数据从物理距离上比L1要更远;L2的容量比L1更大,打个简单的比喻,在小盒子里面找东西要比在大房间里面找要方便快捷。这里也可以看出,缓存并非越大越好,越靠近CPU核心的缓存运行速率越快越好,非最后一级缓存的缓存容量自然是够用即可。

L2二级缓存实际上就是L1一级缓存跟主内存之间的缓冲器,在2006年的时间点上,Intel和AMD当家在售的几款处理器可以看出他们对最后一级缓存不同的见解:Intel Core Duo不同于它的前辈Pentium D、EE,采用了双核心共享的2M L2二级缓存,是属于当时最先二级缓存架构,即“Smart Cache”共享缓存技术,这种技术沿用到以后的Intel推出的所有多核心处理器上;而AMD Athlon 64 X2处理器则是每个CPU核心都具备独立的二级缓存,Manchester核心的处理器为每核心512KB、Toledo核心为每核心1MB,两个核心之间的缓存的数据同步是通过CPU内置的SRI(系统请求接口)控制,这样的数据延迟及占用资源情况都要比Intel的Pentium D、EE核心要好,但还是比不上Core为代表的Smart Cache缓存共享。

三级缓存(L3 Cache)

最初出现L3三级缓存的应该是AMD的K6-III处理器,当时受限于制造工艺,L3只能集成在主板上。然后Intel首次出现L3三级缓存的是Itanium安腾服务器处理器,接着就是P4EE和至强MP。L3三级缓存的出现其实对CPU性能提升呈一个爬坡曲线——L3从0到2M的情况CPU性能提升非常明显,L3从2M到6M提升可能就只有10%不到了,这是在近代CPU多核共享L3的情况下;当L3集成进CPU正式成为CPU内部缓存后,CPU处理数据时只有5%需要在内存中调用数据,进一步地减少了内存延迟,使系统的响应更为快速。

Intel Nehalem L3 SmartCache示意图

同理,L3即为L2与主内存之间的缓冲器,主要体现在提升处理器大数据处理方面的性能,对游戏表现方面有较大的帮助。那么也许有人就会问了,是不是选择CPU的时候看准L3买,哪个CPU的L3大就买哪个?非也,只有同架构的情况下这种比较才具有意义,先举个比较久远的例子:Intel具备1MB L3的Xeon MP处理器仍然不是AMD没有L3的皓龙处理器对手,再来个现有的:Intel I7-8700K 12MB L3和AMD Threadripper 1950X 32MB L3相比,自然是32MB比12MB大,但是平均下来也是一个核心2MB L3,性能就见仁见智了。

由于数据的局限性,CPU往往需要在短时间内重复多次读取数据,内存的运行频率自然是远远跟不上CPU的处理速度的,怎么办呢?缓存的重要性就凸显出来了,CPU可以避开内存在缓存里读取到想要的数据,称之为命中(hit)。L1的运行速度很快,但是它的数据容量很小,CPU能在L1里命中的概率大概在80%左右——日常使用的情况下;L2、L3的机制也类似如此,这样一来,CPU需要在内存中读取的数据大概为5%-10%,其余数据命中全部可以在L1、L2、L3中做到,大大减少了系统的响应时间,总的来说,所有CPU读取数据的顺序都是先缓存再内存。

二 MESI缓存一致性

cpu中的高速缓存分成四种状态分别是:

M(Modified):已修改-数据被修改了

E(Exclusive):独占的-数据是此cpu核独占的

S(Shared):共享的-此数据是多个cpu核所共享的

I(Invalid):失效的-此数据被其他cpu核所修改了,失效

上图中,假使有一个数据int a = 1,这个数据被两个线程读取到了,线程1在cpu核心1上面执行,线程2在cpu核心2上面执行,此时数据a的状态在cup核心1和cpu核心2上面就是S(Shared)共享的,

线程1执行指“a=a+1”,此时数据a在cpu核心1中的状态就是M(Modified)修改的,数据a在cpu核心2上面的状态就变成了I(Invalid)失效的,此时如果cpu核心2再去读取a的数据,会发现a数据的状态是Invalid,那么就会直接去内存读取。

如果数据a,只在cpu核心1的高速缓存里面,而在cpu核心2的高速缓存里面没有,此时数据a在cpu核心1中就是E(Exclusive)独占的。

每个cpu核心与其他cpu核心交互,还要与一些内存等等数据通信,这样复杂度会很高。如果有一根总线,所有的cpu都与这根总线通信,复杂度就会降低很多,而真实的cpu的核心也是这样的,最新的Intel处理器中,有一种快速通道互联的技术。

审核编辑:汤梓红

-

一灯双控接线教程,L、L1、L2该接哪根电线?华哥现场教给你#电路原理电子搬运 2022-11-26

-

发现除了core 0 到core7的 L1,L2地址,还有一个Local L1,L2 SRAM ,这里不太懂2018-06-21 3824

-

C674x 平台(DM8148)数据从 DDR3 到 L1,L2,内存及cache设置2018-06-22 4174

-

请教关于C674x DSP L1 L2 及cache设置2018-07-24 3279

-

请教关于c6424 L2缓存设置问题2018-08-02 2613

-

2 级和3 级(L2 和L3)互连子系统 请问“基本功能性的引导时间软件测试”是怎么实现的2018-08-08 2251

-

如何在微机上测量l1相、l2相和l3相移差角?2019-10-18 1576

-

ARM架构下的L1和L2 cache结构有什么联系2022-08-12 3250

-

基于890085下的 L1/L2 Low Loss GPS SAW Diplexer2018-08-06 1257

-

自动驾驶:L1到L2到L3,难点在哪儿?2019-06-05 33663

-

自动驾驶汽车中的L2和L3级有什么不同2019-09-01 24522

-

接触器L1和A1连接有什么作用2019-12-22 10792

-

电灯开关L、L1和L2怎么接线2020-01-16 139817

-

丰田从L2逐步演进到L3的自动驾驶系统介绍2021-04-12 5860

-

开关上的l l1 l2是代表什么2022-01-29 93136

全部0条评论

快来发表一下你的评论吧 !