基于三维阻变存储器的存算一体技术

存储技术

描述

近年来,随着芯片工艺制造的进步,工艺制程逐渐接近物理极限,深度神经网络的发展使得计算量和参数量呈指数上升。具有高密度,非易失,易加工等优点的阻变存储器(RRAM),被认为是最具代表性的新型存储器之一,是低功耗,低成本、高算力兼备的理想选择。

为解决阻变存储器应用于大规模神经网络面临的多个挑战,由中国科学院微电子研究所微电子器件与集成重点实验室刘明院士、张锋研究员团队与北京理工大学集成电路与电子学院王兴华副教授团队,共同研发了“基于三维阻变存储器的存算一体技术”,首次突破了三维垂直结构阻变存储器存算一体宏单元芯片。项目吸引来自学术界与产业界的广泛关注,并于近日入选中国半导体十大研究进展候选推荐。

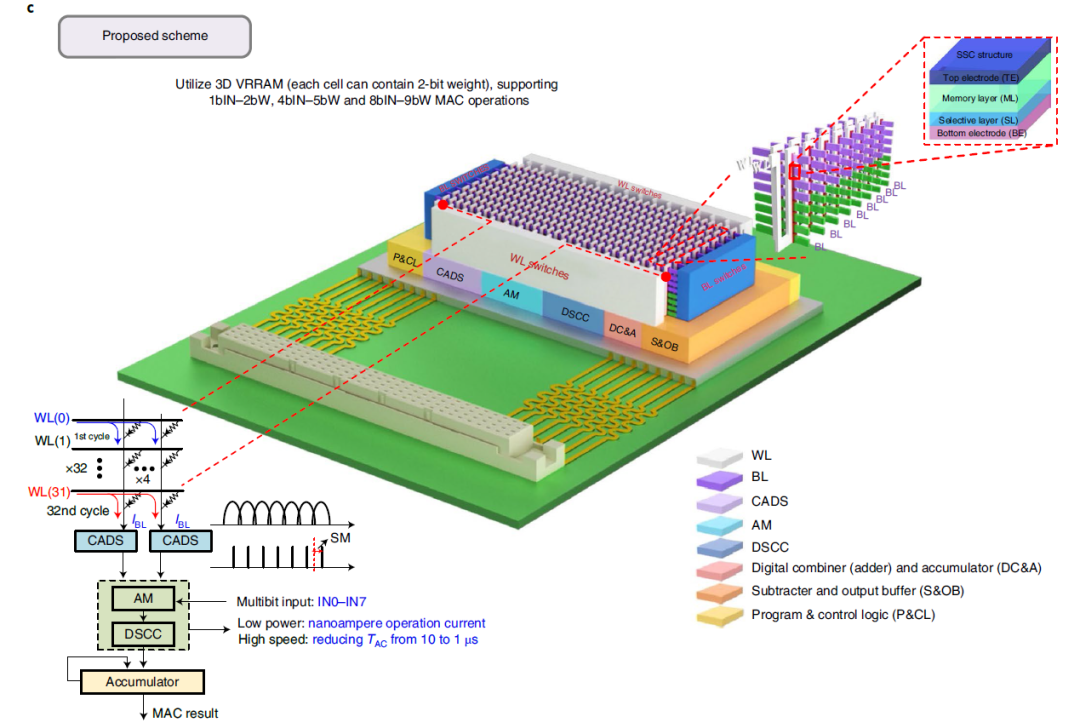

三维垂直结构阻变存储器存算一体技术(即图1)采用三维阻变存储器与外围运算电路堆叠结构,能够实现1bIN-2bW、4bIN-5bW和8bIN-9bW的乘累加计算精度的基于三维垂直阻变存储器阵列的存算一体功能。

图1. 基于三维垂直结构阻变存储器的

高精度存算一体宏单元

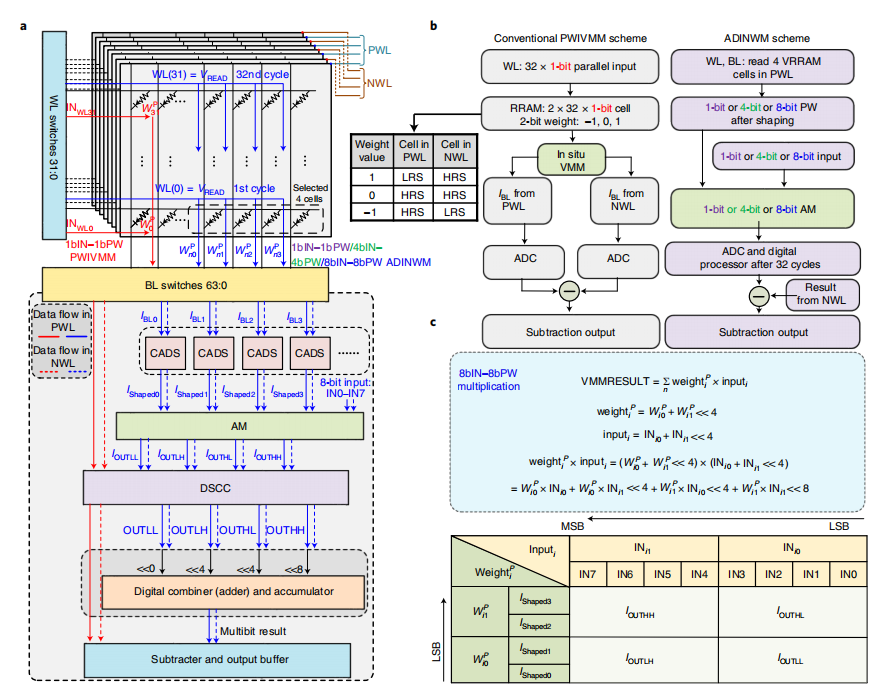

结构将多值自选通(Multi-level self-selective, MLSS)三维垂直阻变存储器与抗漂移多位模拟输入权值乘(ADINWM)方案相结合(如图2所示),实现了高密度计算;在抗漂移多位模拟输入权值乘方案基础上提出了电流幅值离散整形(CADS)电路用于增加读出电流的感知容限(SM)用于后续精确的模拟乘法计算,解决了由于三维阻变存储器阵列单元电导波动引起读出电流失真。

图2. 三维阻变存储器结构的存算模式

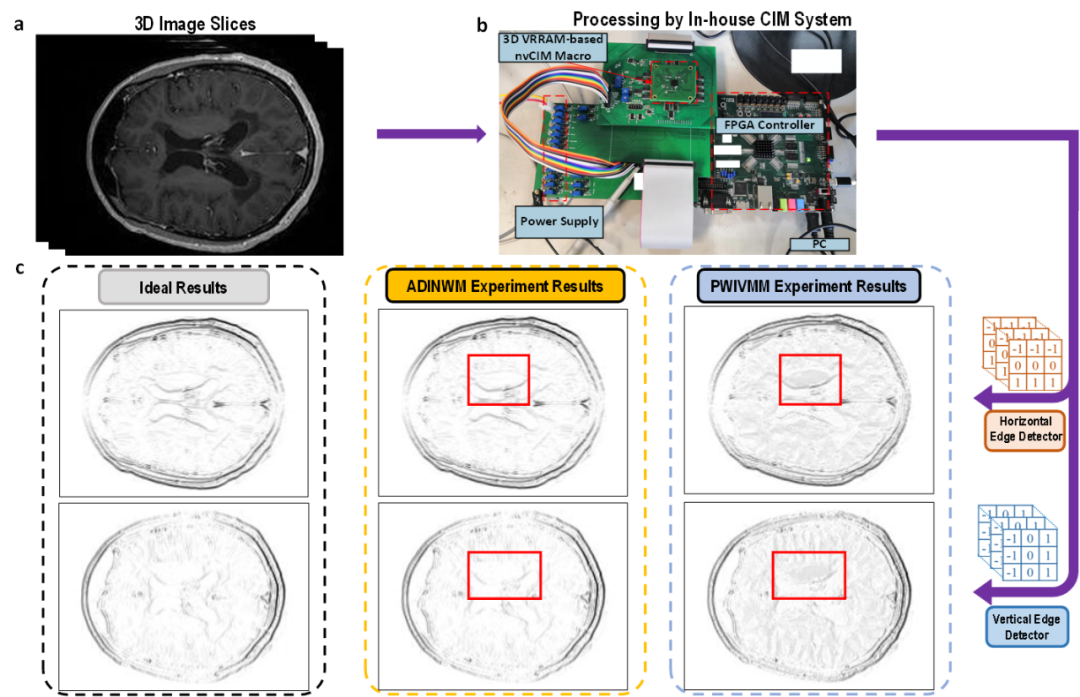

图3展示了硬件自动测试平台通过FPGA控制实现了采用抗漂移多位模拟输入权值乘方案的1bIN-2bW(1bit输入和2bit权重)、4bIN-5bW(4bit输入和5bit权重)和8bIN-9bW(8bit输入和9bit权重)精度的乘累加操作,作为对比,同时实现了采用传统并行字线输入原位乘累加方案的1bIN-2bW精度的乘累加操作。当采用1bIN-2bW的计算精度时,部署开发平台用于三维脑核磁共振图像的边缘检测,边缘检测是卷积神经网络前几层的主要功能之一。与传统方法相比,提供了更准确的大脑MRI边缘检测和更高的数据集推理精度。

图3. 芯片测试平台

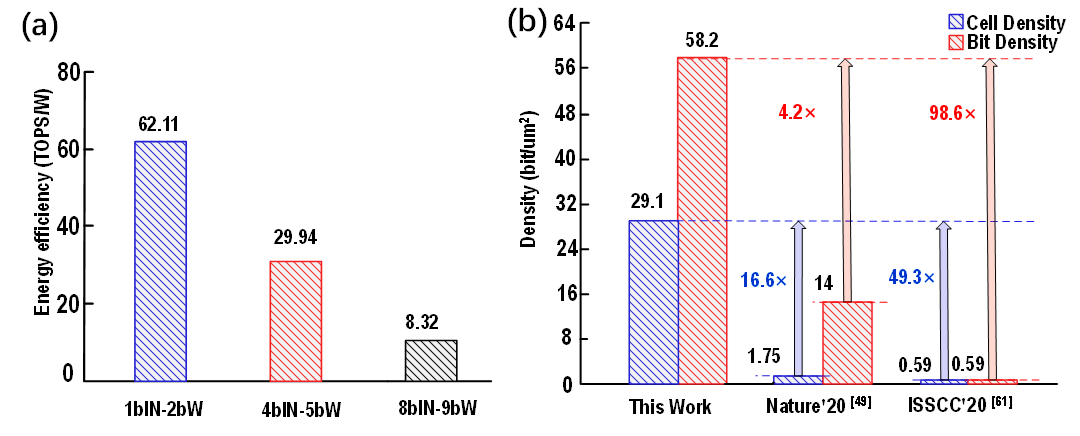

同时报告展示了该宏单元的能效情况(图4),该工作在1bIN-2bW、4bIN-5bW和8bIN-9bW精度配置下分别取得了62.11 TOPS/W、29.94 TOPS/W和8.32 TOPS/W的能效。该宏单元中计算位密度为58.2 bit/um2,可以看到,该三维阻变存储器阵列单元密度比基于二维阻变存储器的计算密度也高出多倍。

图4. 三维阻变存算一体芯片性能测试

最终通过实验证明,基于三维垂直结构的阻变存储器的存算一体结构,不但能够实现高密度的计算密度,还可以实现低功耗高能效的存算一体结构,在三维神经网络计算方面尤其独有的技术优势,未来在边缘智能计算领域有很好的应用前景,将很大程度上拓展存算一体方向的发展应用空间。

审核编辑:汤梓红

-

比存算一体更进一步,“感存算一体化”前景如何?2022-06-08 7683

-

存算一体技术路线如何选2022-06-21 11008

-

存算一体技术发展现状和未来趋势电子发烧友网官方 2023-04-25

-

NAND型三维多层1TXR阻变存储器设计2011-12-07 988

-

一文解析阻变存储技术2020-11-04 4170

-

国产存算一体超速前进 存算一体架构有机会解决很多AI面临的问题2022-11-25 3019

-

2023年存算一体是芯片设计的技术趋势2023-01-13 3396

-

关于存算一体,我们和ChatGPT聊了聊2023-02-09 2792

-

特斯拉的下一代AI芯片:存算一体2023-03-09 3499

-

浅谈存算一体技术的发展路线2023-06-20 3992

-

如何选择存储器类型 存算一体芯片发展趋势2023-09-06 1862

-

存算一体芯片的技术壁垒2023-09-22 2689

-

存算一体芯片新突破!清华大学研制出首颗存算一体芯片2023-10-11 2180

-

忆阻器(RRAM)存算一体路线再次被肯定2023-10-26 3386

-

一文看懂“存算一体”2025-08-18 1662

全部0条评论

快来发表一下你的评论吧 !