与PDM接口相关的开源项目

描述

优秀的 Verilog/FPGA开源项目介绍(三十四)- PDM音频接口设计及信号处理

绪论

今天介绍几个与PDM接口相关的开源项目。

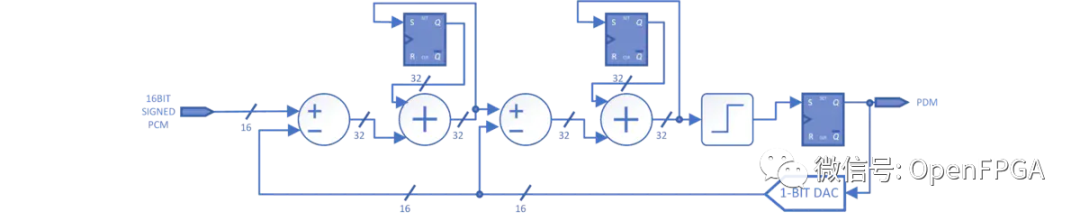

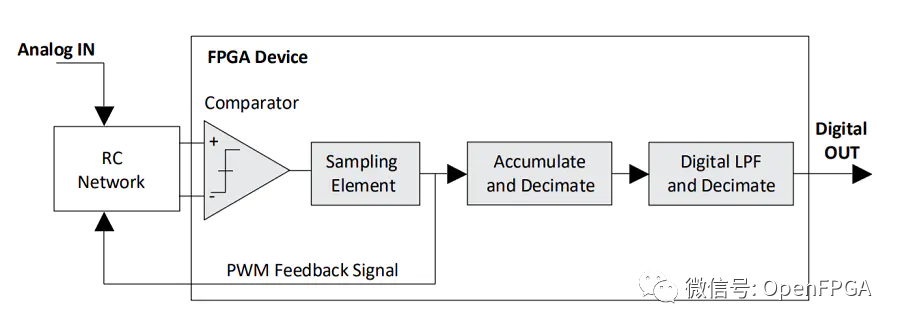

FPGA使用Delta-sigma ADC实现PDM音频输出

https://github.com/Elrori/Delta-sigma-ADC-verilog

https://www.jianshu.com/p/f5e17ee2fd25

介绍

整个方案实现的原理主要是将PDM输出到FPGA管脚然后经过低通滤波接到比较器负端,Digital Filter换成累加器,就变成了真正的1-Bit ADC。可以量化模拟比较器正端电平。参考见下图:

License

No license

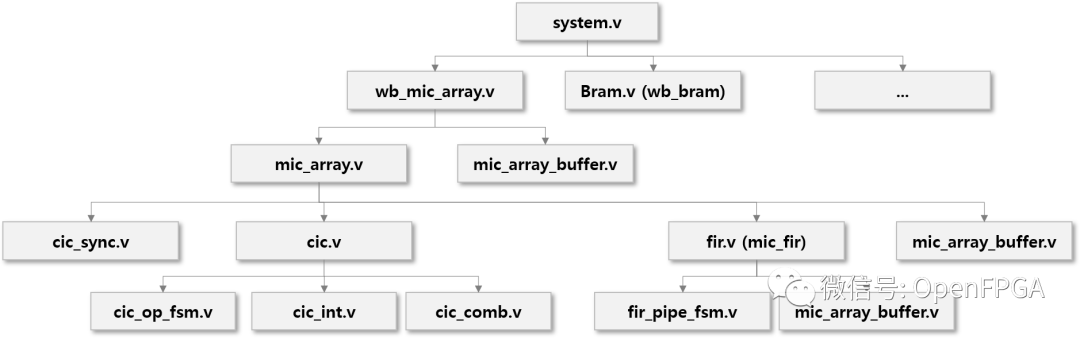

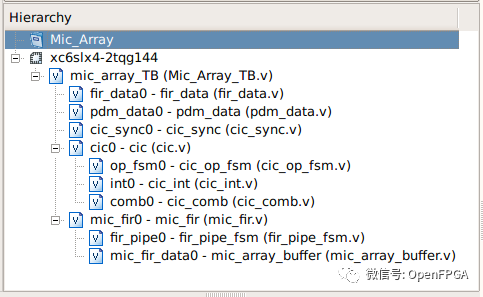

PDM-MIC信号处理

https://github.com/Hoi-Jeon/Verilog-for-Mic-in-Matrix-Creator

这个项目的目的是研究其接收来自 8 个PDM 麦克风的信号处理的 FPGA 代码。这个代码的结构如下:

测试结构:

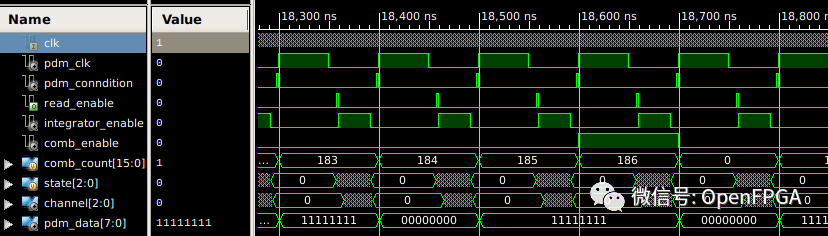

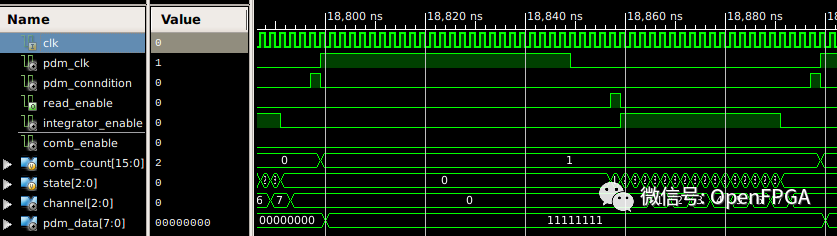

仿真结果:

pcm2pdm-example

https://github.com/kazkojima/pcm2pdm-example

https://github.com/kazkojima/pdmmic-example

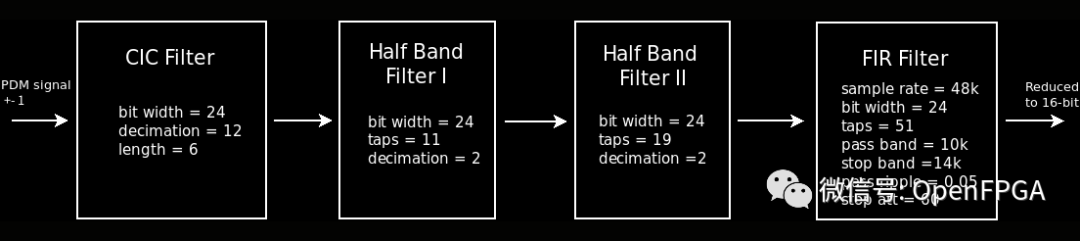

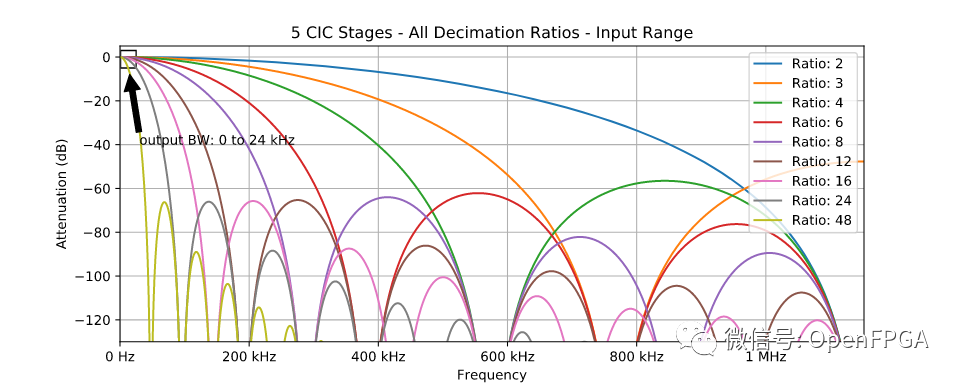

这两个项目都是kazkojima大神带来的项目,都是PDM-MIC的信号处理,同时有详细的设计过程:

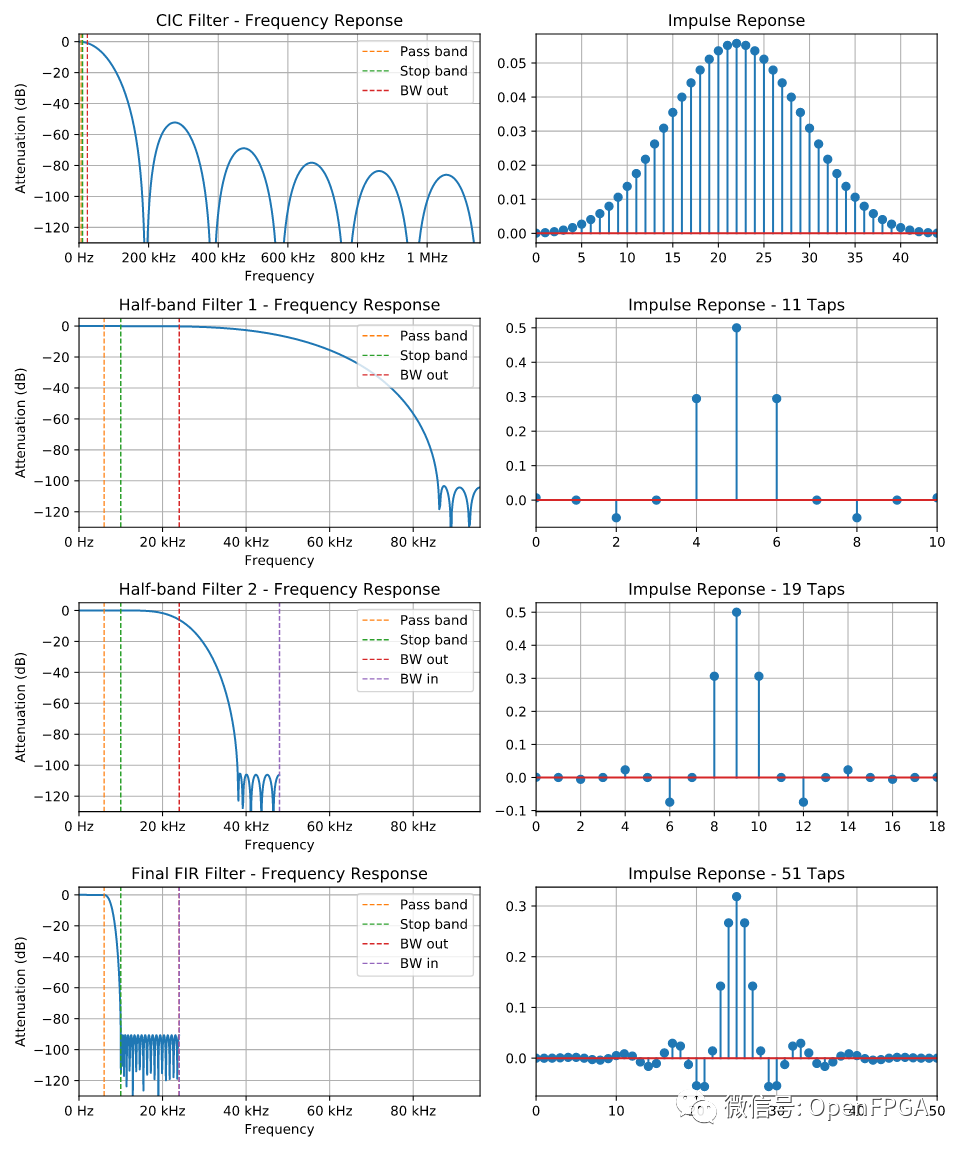

https://tomverbeure.github.io/2020/12/20/Design-of-a-Multi-Stage-PDM-to-PCM-Decimation-Pipeline.html

包括仿真设计等。

icebreaker-verilog-examples

https://github.com/icebreaker-fpga/icebreaker-verilog-examples

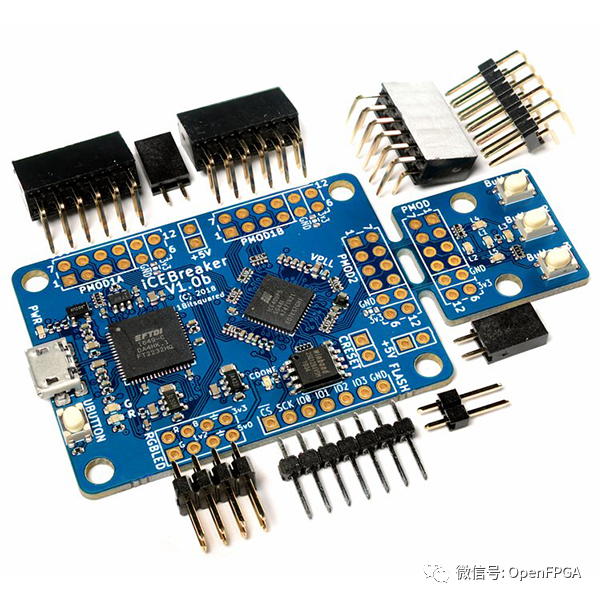

这是一个基于Lattice iCE40UP5k FPGA的开发板(极其经典)。

介绍

初识Lattice iCE40UP5k FPGA就是通过这个板卡,小巧及强大的开源板卡,其自带的开源工程极其丰富,链接就是这个板卡及类似板卡的参考项目。

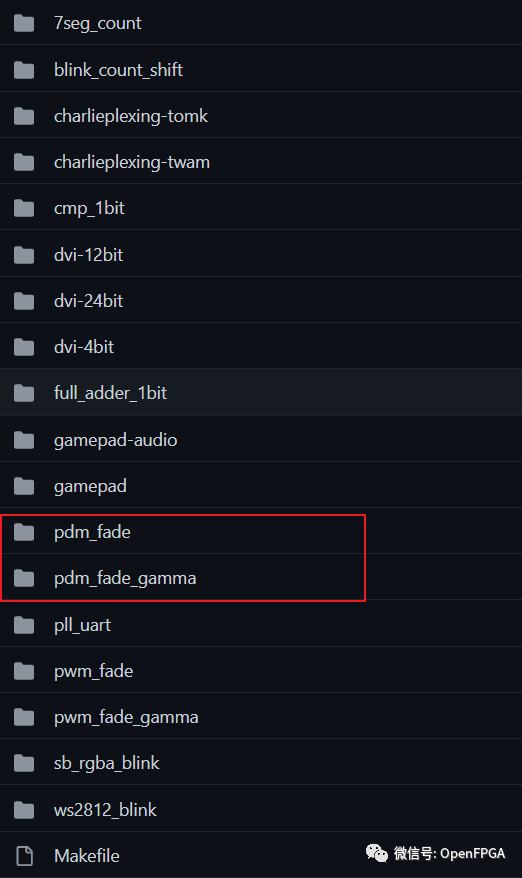

其中PDM相关文件夹就是我们需要的项目,其他项目也很基础,也适合学习。

axi_pdm

https://github.com/Pieter-Berteloot/PYNQ_Video_overlay/tree/1010a7a2a32e0a1c246423989b5acbfcf45a4eab/boards/ip/d_axi_pdm_1.2

介绍

基于BD设计目前在国内流行还是比较广的,所以这个项目就是我们需要的-一个基于AXI总线的IP值得学习。

catena-riscv32-fpga

https://github.com/mcci-catena/catena-riscv32-fpga

RISC-V这么火,怎么能没有音频,这个项目就是用在RISC-V系统里的音频IP,详细的地址如下:

https://github.com/mcci-catena/catena-riscv32-fpga/tree/master/hw/src/lib/pdm_audio

其他

https://github.com/JAMBD/ice_pdm

总结

今天介绍的基于PDM项目,分为实现和处理两部分。

-

PDM是什么?2025制造PDM/PLM系统盘点2025-06-19 2391

-

TLV320AIC3262可配置为立体声数字麦克风脉冲密度调制 (PDM) 接口,请问可以支持几个PDM接口?2024-10-17 437

-

如何在TAS2563中配置PDM接口?2024-10-09 456

-

TAS2563 PDM麦克风接口和回声参考2024-09-13 581

-

请问ESP32-C3 I2S接口支持PDM接收吗?2023-02-17 687

-

FPGA使用Delta-sigma ADC实现PDM音频输出2022-10-17 3285

-

Apple磁盘接口开源项目2022-08-04 650

-

限位开关接口板开源项目2022-08-01 649

-

分享一些高星开源项目2022-02-28 1913

-

智能硬件设计中I2S、PDM、TDM选什么音频接口2022-02-23 14211

-

嵌入式相关开源项目资料分享2021-10-27 2785

-

openharmony开源项目2021-06-21 2841

-

基于Web服务的航空项目管理与PDM系统集成2009-04-14 794

全部0条评论

快来发表一下你的评论吧 !