二维半导体晶体管实际沟道长度的极限

电子说

描述

高性能单层二硫化钼晶体管的实现让科研界看到了二维半导体的潜力,二维半导体材料的发展让我们看到了晶体管纵向尺寸下目前的缩放极限(< 1 nm),同样的科学家们也没有停止追寻二维半导体晶体管横向尺寸的极限(也就是晶体管沟道长度的缩放极限)。我们知道目前的工艺节点已经发展到5 nm以下,工艺节点名称的含义早就不再是实际的栅极或者半节距(half-pitch)长度,更多的应该理解在延续摩尔定律下的一个工艺代称,实际制备的晶体管的沟道长度是大于节点名称的,且基于当前的EUV以及硅基工艺体系,实际沟道长度的缩小越来越难。与传统硅基工艺相比,目前二维半导体晶体管的制备大多采用EBL(电子束光刻)工艺,它可以实现更小尺寸沟道器件的制备,可以制备的二维半导体晶体管的实际沟道尺寸达到10 nm以下,这和EBL工艺本身的分辨率强相关,然而单单通过EBL工艺本身带来的沟道尺寸缩小也已经发展到了极限。在当前技术体系下硅基晶体管的实际沟道长度不能低于5 nm,而二维半导体材料则没有这一限制,因此如何实现更小沟道尺寸的二维半导体材料晶体管以及其性能的探索一直是一个热点科研问题,今天要讲解的两篇文章分别发表在Science和Nature上,文章中分别用碳纳米管和石墨烯作为栅电极,实现了1 nm以及< 1 nm沟道长度的二硫化钼晶体管,这也是当时二维半导体晶体管实际沟道长度的极限。

文章一:MoS2 transistors with 1-nanometer gate lengths

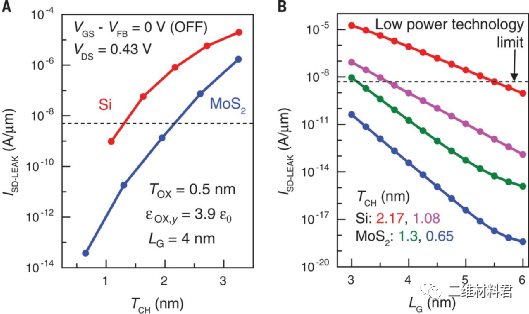

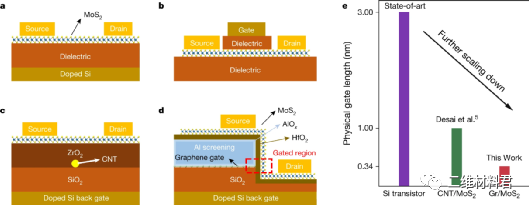

图1 Si基和MoS2晶体管源漏隧穿电流(MoS2明显优于Si基)

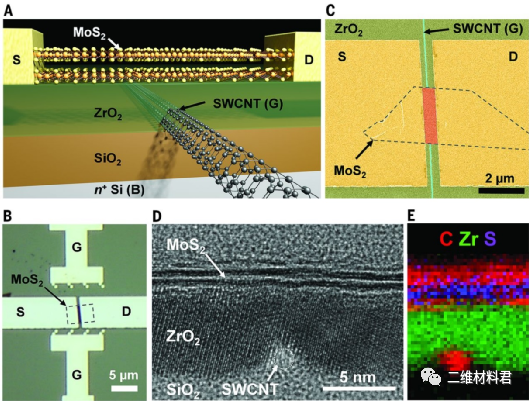

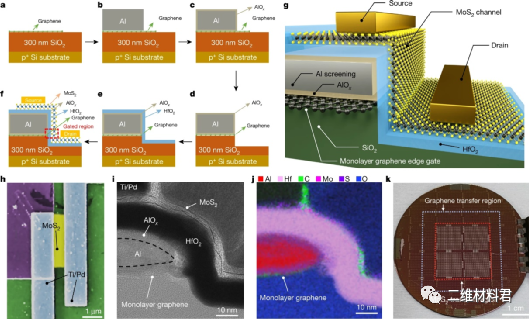

图2 器件结构以及表征测试

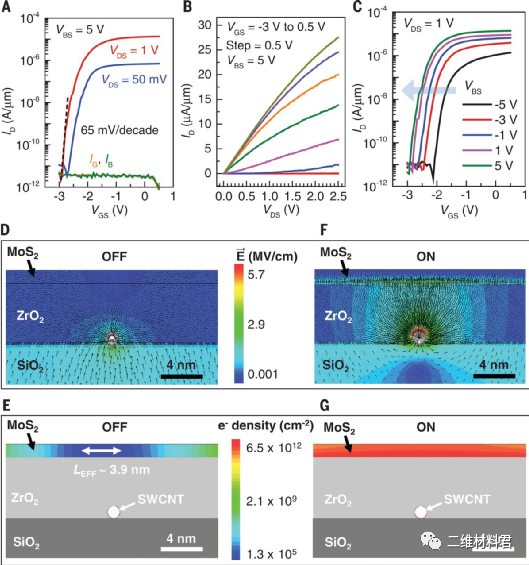

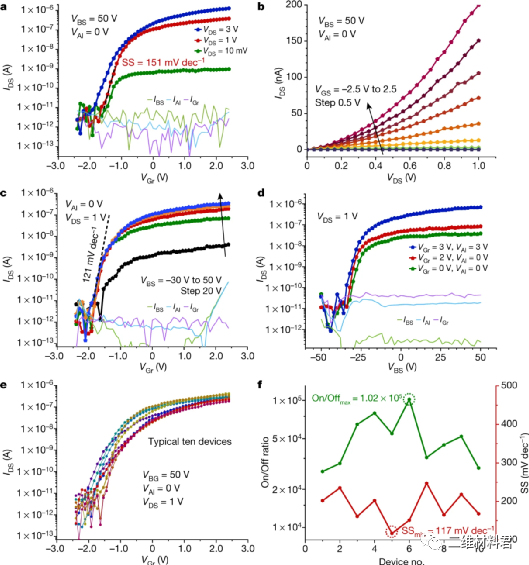

图3 器件的电学性能测试及TCAD仿真

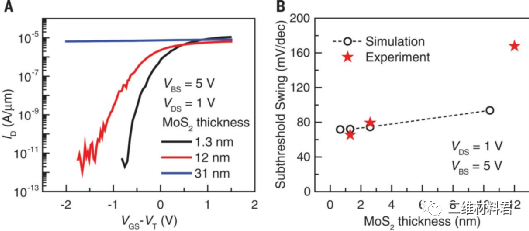

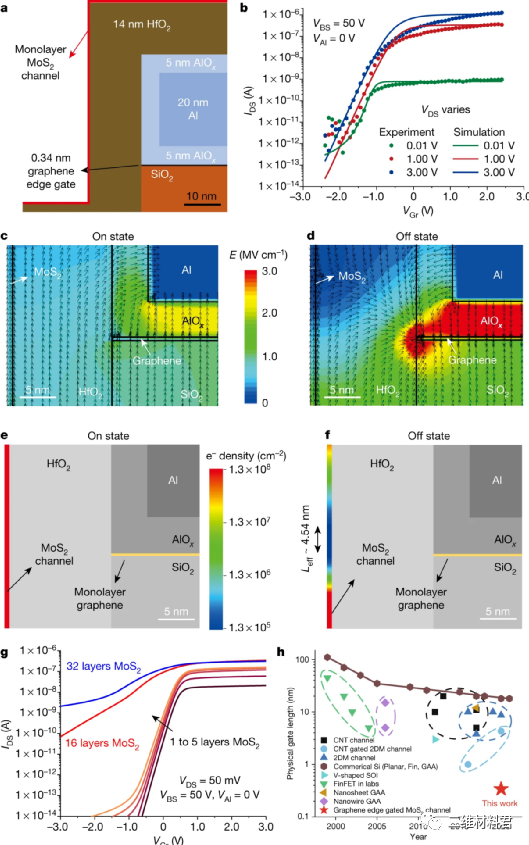

图4 MoS2薄膜厚度对器件性能影响

文章2:Vertical MoS2 transistors with sub-1-nm gate lengths

图1 0.34 nm沟道长度侧壁晶体管和其他晶体管结构对比

图2 0.34 nm沟道长度侧壁晶体管结构与表征

图3 0.34 nm沟道长度侧壁晶体管的电学性能

图4 TCAD仿真结构及性能对比

这两篇文章中,作者关于器件结构的设计都有着自己独特的巧思,想到是一个层次,真正实现又是另一个层次,不管是工艺制备的实现以及后续对于器件的TCAD仿真结果的实现都需要很多的知识积累。从这两篇文章可以看到二硫化钼晶体管在1 nm甚至1 nm沟道尺寸之下仍有着相当好的性能表现,它们可以说是二维材料发展路上的两盏明灯,指引我们继续二维的探索。

-

面向硅基产线:二维半导体接触电阻的性能优化2025-09-29 2616

-

首次实现GHz频率的二维半导体环形振荡器电路2023-11-24 2018

-

制造二维TMD晶体管面临的挑战2023-11-07 3189

-

什么是晶体管 晶体管的分类及主要参数2023-02-03 2565

-

基于垂直架构的新型二维半导体/铁电多值存储器2022-11-28 1176

-

准费米能级相空间及其在双极型二维场效应晶体管中的应用2022-05-26 2689

-

湖南大学成功实现1纳米物理沟道长度的垂直场效应晶体管2021-05-10 4355

-

剖析二维电子器件的高k介电薄膜——氟化钙2021-04-20 5997

-

二维半导体能拯救摩尔定律吗?2020-10-25 2313

-

一种由石墨烯和二维超导体制成的新型晶体管问世2020-03-22 3442

-

哪里可以找到Xilinx芯片晶体管通道长度的规格?2019-11-11 2013

-

场效应晶体管的分类及作用2019-05-08 4256

-

半导体晶体管的基本概念2018-12-15 2179

-

晶体管的极限参数2010-01-26 8156

全部0条评论

快来发表一下你的评论吧 !