FPGA设计高级技巧(Xilinx篇)

可编程逻辑

1397人已加入

描述

随着HDL (Hardware Description Language,硬件描述语言)语言、综合工具及其它相关工具的推广,使广大设计工程师从以往烦琐的画原理图、连线等工作解脱开来,能够将工作重心转移到功能实现上,极大地提高了工作效率。

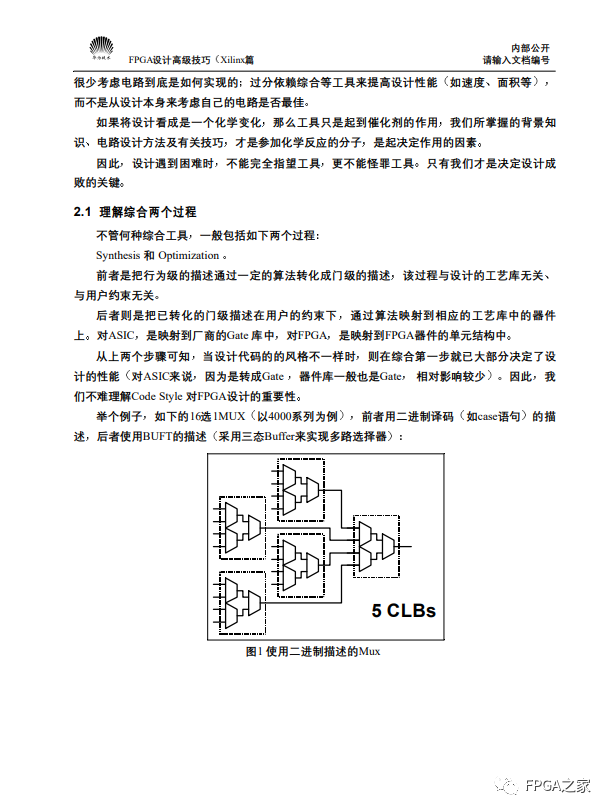

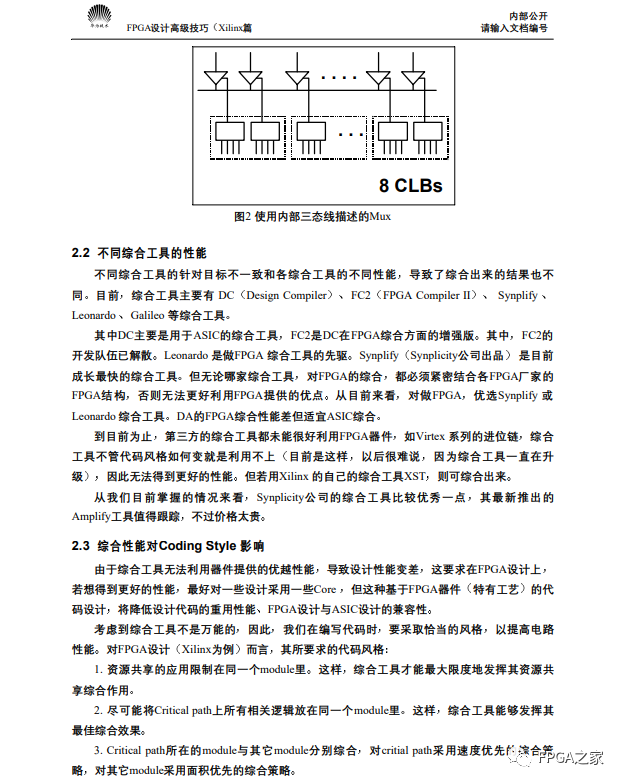

任何事务都是一分为二的,有利就有弊。我们发现,现在越来越多的工程师不关心自己的电路实现形式,以为“我只要将功能描述正确,其它事情交给工具就行了”。在这种思想影响下,工程师在用HDL语言描述电路时,脑袋里没有任何电路概念,或者非常模糊;也不清楚自己写的代码综合出来之后是什么样子,映射到芯片中又会是什么样子,有没有充分利用到FPGA的一些特殊资源。

遇到问题,立刻想到的是换速度更快、容量更大的FPGA器件,导致物料成本上升:更为要命的是,由于不了解器件结构,更不了解与器件结构紧密相关的设计技巧,过分依赖综合等工具,工具不行,自己也就東手无策,导致问题迟迟不能解决,从而严重影响开发周期,导致开发成本急剧上升。

编辑:黄飞

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA设计高级技巧 Xilinx篇2024-01-08 891

-

FPGA设计高级技巧(Xilinx篇)2022-10-24 684

-

【精选福利】精选FPGA资料免费领!!2021-05-27 13001

-

华为FPGA设计高级技巧Xilinx篇资料免费下载2020-05-26 1034

-

【专辑精选】嵌入式FPGA开发学习书籍与资料汇总2019-05-17 4913

-

FPGA培训资料2018-11-23 3279

-

FPGA设计高级技巧(Xilinx篇)2017-12-08 3440

-

FPGA设计高级篇(Xilinx版)2017-09-28 2538

-

华为内部资料:FPGA设计高级技巧(xilinx篇)以及Verilog HDL代码书写规范2015-08-25 59643

-

教你如何学习FPGA~2014-12-11 8209

-

FPGA设计高级技巧Xilinx篇2012-08-11 5907

-

华为 FPGA设计高级技巧Xilinx篇2010-11-19 2892

全部0条评论

快来发表一下你的评论吧 !