eda设计:7nm和更小工艺节点的高性能时钟设计

EDA/IC设计

描述

在曾经经历过在过去的好日子里,时钟信号看起来像方波,并且电压摆幅为 5V or 3.3V,但是使用 7nm 技术,时钟信号现在看起来更像锯齿信号,实际上在芯片的核心内部可能无法达到 0.65V 的完整 Vdd 值。接下来我将介绍一些半导体市场趋势,然后介绍分析 7nm 和更小工艺节点的高性能时钟的挑战。

市场走向

台积电、三星和英特尔等代工厂正在为从事各种 SoC 设备的设计人员提供 7nm及更小的节点技术,这些设备用于:人工智能、机器人、自动驾驶汽车、航空电子设备、医疗电子、数据中心、5G 网络和移动设备。这些设计需要数十亿晶体管范围内的高集成度,以及在电池或严格的功率预算内运行的低功率。

7nm 设计挑战

高级节点存在许多设计挑战,例如:

晶体管老化效应

更高的设计成本,每个7纳米设计的成本在1.2-4.2亿美元之间

使用较低的 Vdd 水平降低了设计裕度

功耗随时钟频率上升

工艺变化的影响

更大的延迟变化

互连 RC 变化增加

更高电阻的互连导致信号失真

更快的晶体管开关时间带来更大的功率瞬变

更多具有多电压电源域的时钟

与开关相关的功率密度和芯片温度增加

DRC 规则组复杂性显著增加

老化效应

随着晶体管器件的开启和关闭,有两个主要的物理效应会影响可靠性:

负偏压温度不稳定性 ( NBTI )

热载体注入 (HCI)

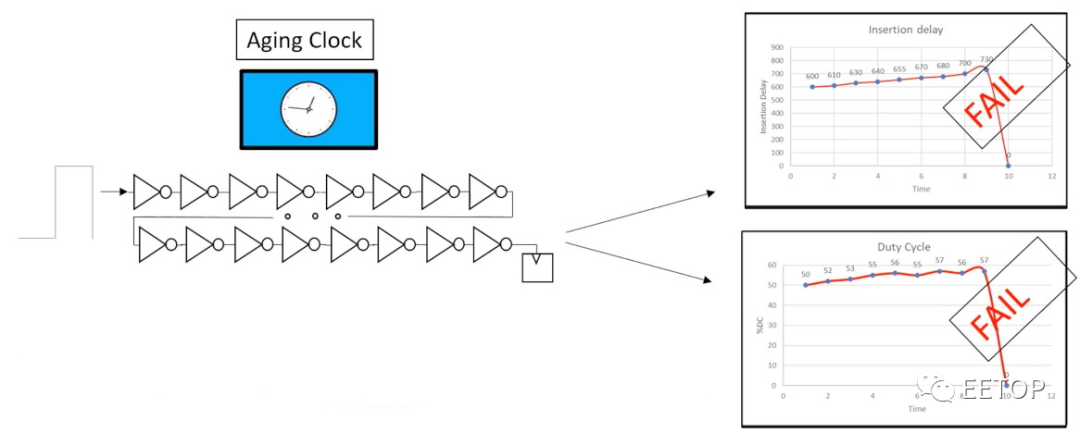

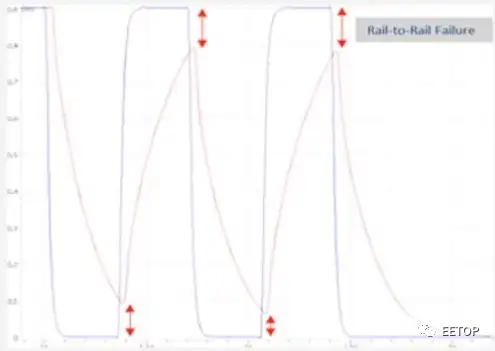

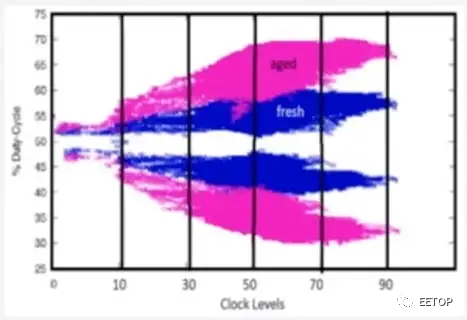

电路设计人员了解到,这些老化效应会改变器件的 Vt,进而减慢时钟信号的上升和下降时间。随着时间的推移,这些老化效应会扭曲时钟的占空比,实际上会导致时钟电路出现故障。下面显示的是两个图表,其中时钟插入延迟和占空比最终因老化效应而失败。时钟抖动和轨到轨(R2R) 违规的增加也表现为老化效应。

老化时钟

老化时钟

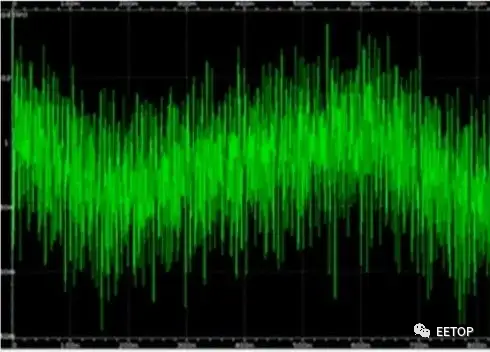

静态时序分析 (STA)

多年来,EDA用户一直依赖于STA工具,然而这些工具对老化效应做了简化的假设,通过应用覆盖式定时降额,而不是根据实际的开关活动应用老化。在长信号网络中,由于电阻屏蔽,STA中的互连延迟模型会忽略占空比畸变误差。STA工具也不能直接捕捉轨到轨故障,尽管它可以测量插入延迟和切换速率。抖动不是作为 STA 工具的一部分进行模拟的,因此设计人员不知道哪些区域需要修复的噪声最高。

克服分析限制

理想的时钟分析方法将提供整个时钟域的SPICE级精度,即使有数百万个器件。它将允许工程师测量整个时钟路径上每个节点的R2R和抖动,包括有无老化。多个时钟可以在许多工艺角和Vdd组合中进行分析,在当前EDA工具流程中工作,并在一夜之间产生结果。

Infinisim 方法

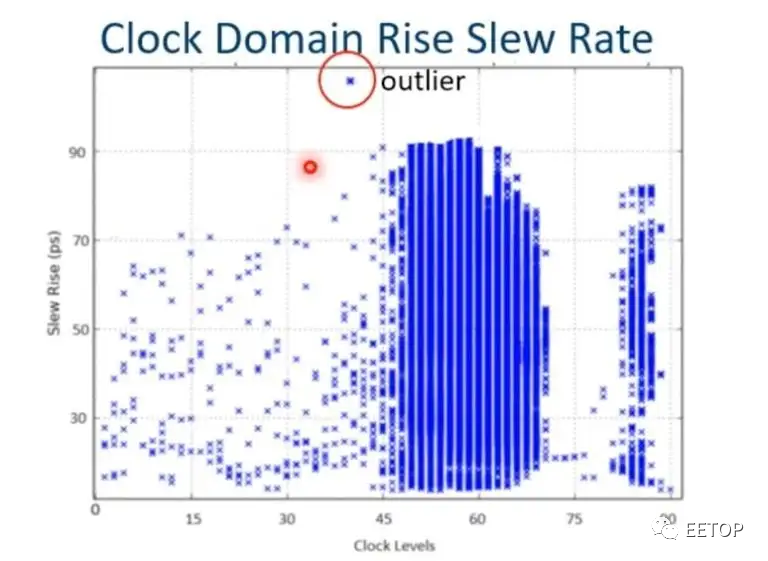

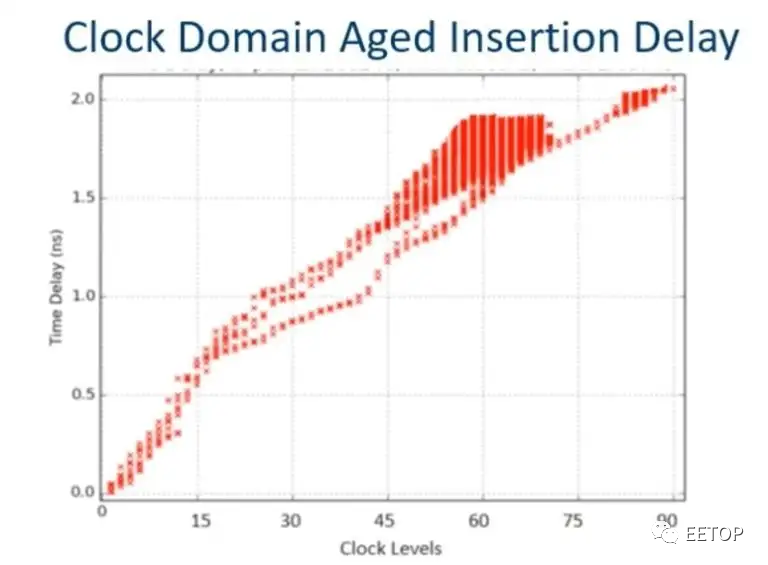

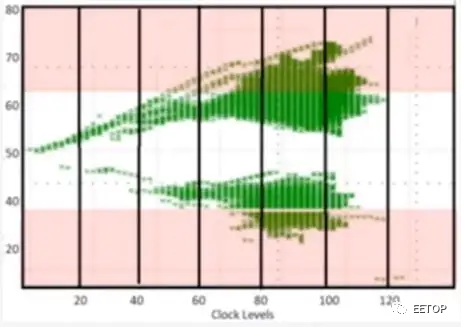

Infinisim 是一家专注于时钟分析的 EDA 供应商,他们的工具称为ClockEdge。以下是他们工具中时钟域上升摆率和时钟域老化插入延迟的两个分析示例:

Infinisim 的 EDA开发人员想出了如何模拟整个时钟域,产生具有 SPICE 精度的完整模拟结果,允许 SoC 团队在老化时实际测量时钟占空比,或测量 R2R,甚至测量噪声引起的抖动。ClockEdge 工具甚至以分布式方式跨多个服务器运行,以便在较快地产生结果。

时钟占空比退化

轨到轨故障检测

老化效应

抖动

ClockEdge 确实是 STA 的补充, ClockEdge 将成为您的时钟签核工具。所有设备老化模型均由您的代工厂提供。作为 ClockEdge 性能的一个例子,它运行在一个有 450 万个门、包含数十亿个晶体管的时钟电路上;跟踪需要 4.5 小时,仿真总共需要 12 小时,在 250 个 CPU 上运行。

总结

设计 7nm 和更小工艺节点的 SoC 是一项艰巨的任务,需要专业的时钟分析知识以确保首次通过硅片成功。

编辑:黄飞

-

2018年AMD将率先使用GlobalFoundries 7nm工艺2016-11-08 1435

-

一文详解芯片的7nm工艺2023-12-07 12082

-

中芯国际7nm工艺Q4季度问世:性能提升20% 功耗降低57%2020-02-28 6431

-

10nm、7nm等制程到底是指什么?宏旺半导体和你聊聊2019-12-10 10354

-

Fusion Design Platform™已实现重大7nm工艺里程碑2020-10-22 2386

-

芯片工艺从目前的7nm升级到3nm后,到底有多大提升呢?2021-06-18 12928

-

从7nm到5nm,半导体制程 精选资料分享2021-07-29 8370

-

介绍分析7nm和更小工艺节点高性能时钟的挑战2022-11-04 2703

-

【图文】ARM、赛灵思首发TSMC 7nm:2017年初流片,2018年将上市2017-01-13 2287

-

AMD将聚焦7nm工艺 每瓦性能将提升至2倍2018-08-28 744

-

格罗方德退出7nm工艺大战2018-09-06 3669

-

7nm工艺或将成为Intel下一个高性能节点2020-09-17 2065

-

Intel还在努力推进7nm工艺,最快2021年量产2019-10-12 3416

-

英特尔推出10nm SF工艺,号称比其他家7nm工艺还要强2020-09-27 4599

-

EDA软件介绍分析与EDA软件发展前景解密2020-11-16 6932

全部0条评论

快来发表一下你的评论吧 !