全流程EDA模拟电路设计解决方案

EDA/IC设计

描述

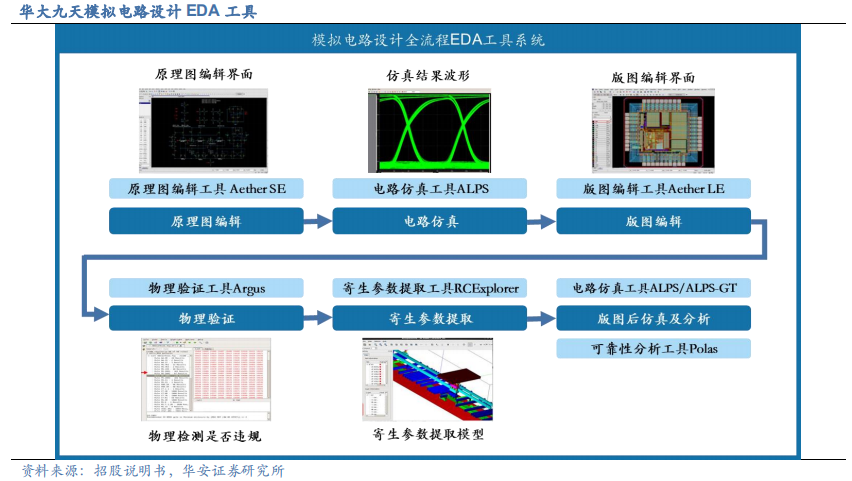

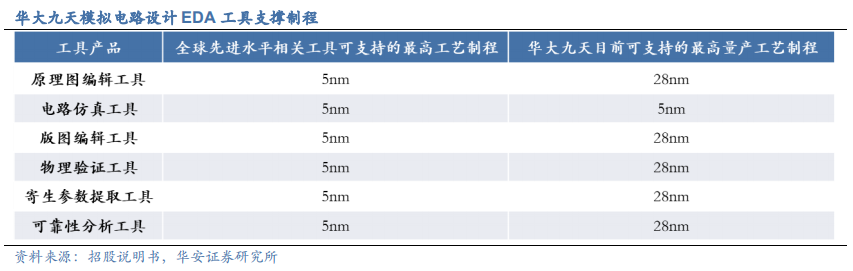

本文选自“华大九天:国产替代叠加景气下游,国产EDA龙头未来可期(2022)”。华大九天是国内唯一模拟电路全流程 EDA 工具供应商,电路仿真工具支持 5nm 制程。拥有模拟电路全流程 EDA 工具,包括原理图及版图编辑工具、电路仿真工具、物理验证工具、寄生参数提取工具和可靠性分析工具等,致力于为用户提供从电路到版图、从设计到验证的全流程模拟电路设计解决方案。

具体来看,公司电路仿真工具 ALPS 支持最先进的 5nm 量产工艺制程,处于国际领先水平,其余EDA 工具则支持 28nm 工艺制程。当下,模拟芯片的生命周期较长、对先进工艺制程要求较低,大部分模拟电路芯片产品仍在使用 28nm 及以上的成熟工艺制程,下游芯片设计者更关注性能、可靠性和成本指标,公司的模拟电路设计 EDA 工具系统已经能够满足大部分的市场需求。

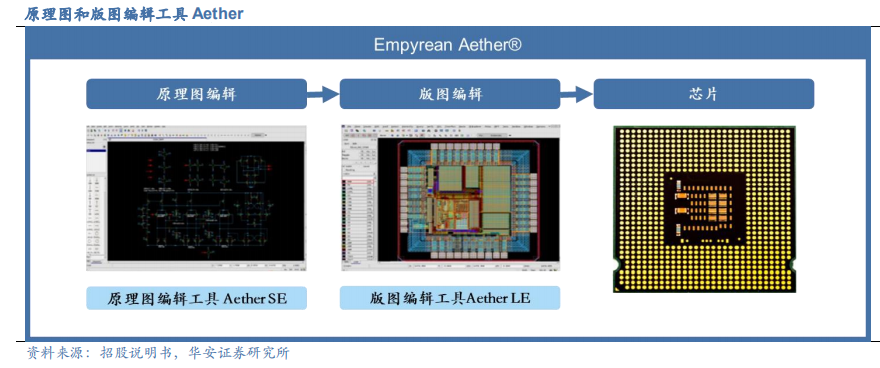

原理图和版图编辑工具 Aether:先进的多工具集成平台,为用户提供一站式的高效设计体验。原理图和版图编辑工具主要用于帮助设计者实现符号库和电路图的创建和编辑。

电路仿真工具 ALPS :搭载仿真加速和大规模矩阵智能求解技术,支持世界领先的5nm 制程。电路仿真工具可以模拟电路的功能和实时状态,而不需要建立实际的电路,进而省去昂贵的实物建立成本。随着电路规模显著上升,平衡仿真时间和仿真精度成为电路仿真软件的核心难点。面对行业痛点,公司创新性地开发了两大核心技术:

1)CPU-GPU 异构系统的仿真加速技术,该加速技术利用 GPU 更适合进行运算量较大的特征,将仿真算法中的器件计算、矩阵求解交给 GPU,显著提升仿真效率。

2)大规模矩阵智能求解技术,该技术可以根据电路中不同模块的矩阵特点,自动选择最优的矩阵求解算法,显著提升了矩阵的求解效率。

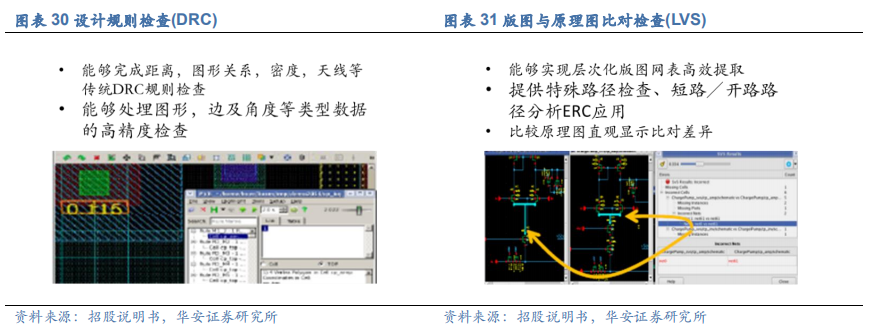

物理验证工具 Argus:两大技术助力创新,大幅缩短设计周期。物理验证工具主要用于检查电路设计版图与制造加工之间的适配性以及版图设计与电路设计之间的一致性,起到消除设计错误、降低设计成本和减少设计失败的作用。公司的物理验证工具Argus 主要包括设计规则检查(DRC)和原理图版图一致性检查(LVS)。一方面,公司在传统的扫描线技术基础上,开发了基于边的扫描线技术和版图预处理技术两大核心技术,以提升分析效率;另一方面,Argus 可以无缝集成到原理图版图编辑工具 Aether中,形成一站式设计和验证解决方案。从下游客户来看,Argus 已经取得了多家先进晶圆厂的认可,现已成功流片超过十亿颗。

寄生参数提取工具 RCExplorer:兼顾高速与高精度要求。寄生效应在复杂 IC 设计中会对模型精确性产生显著影响,寄生参数提取工具能对其进行分析和优化设计。公司寄生参数提取工具RCExplorer 能根据不同的精度要求,在侧重速度和侧重精度的提取模式之间进行切换,为芯片版图设计的各个阶段,进行准确快速的寄生效应分析,为优化电路性能和可靠性提供支撑。

速度方面,公司自研的电阻网络快速提取技术通过多种先进的优化算法,对分析对象进行切割、等效简化,实现大规模版图电阻网络的快速提取。

精度方面,公司自研的偏微分方程求解技术,能够基于边界元素法的区域分解加速算法、自适应网格划分算法以及高效的迭代求解算法,实现高精度的寄生参数提取。

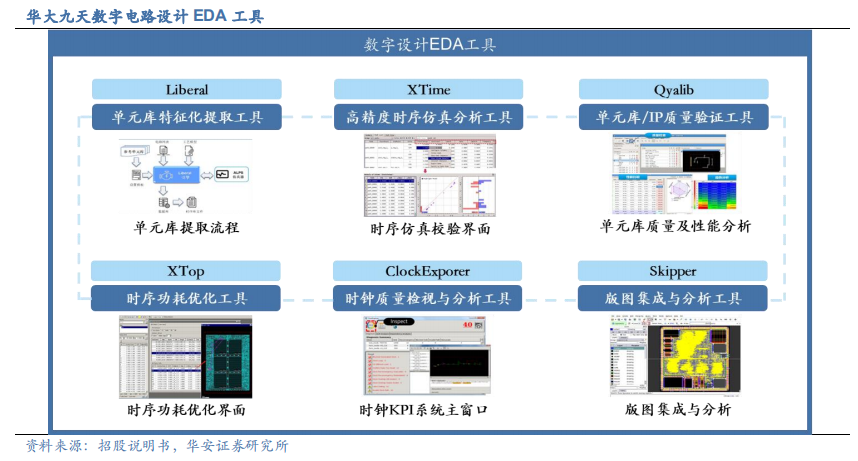

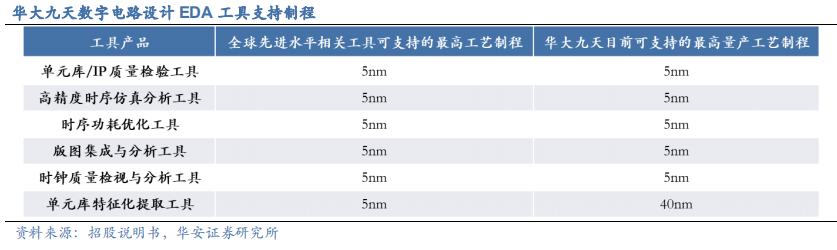

数字电路 EDA 实现点工具突破,数字电路设计可分为前端和后端两部分:前端设计:将设计需求转化为门级网表电路,主要流程包括规格制定、详细设计、仿真验证、逻辑综合等。后端设计:将门级网表电路转化为设计版图,主要流程包括布局布线、寄生参数提取、时序分析优化、版图物理验证等。公司数字电路设计 EDA 工具已经涵盖单元库/IP 质量验证工具、高精度时序仿真分析工具、时序功耗优化工具、版图集成与分析工具、时钟质量检视与分析工具和单元库特征化提取工具,除单元库特征化提取工具外均已支持 5nm 级别工艺。

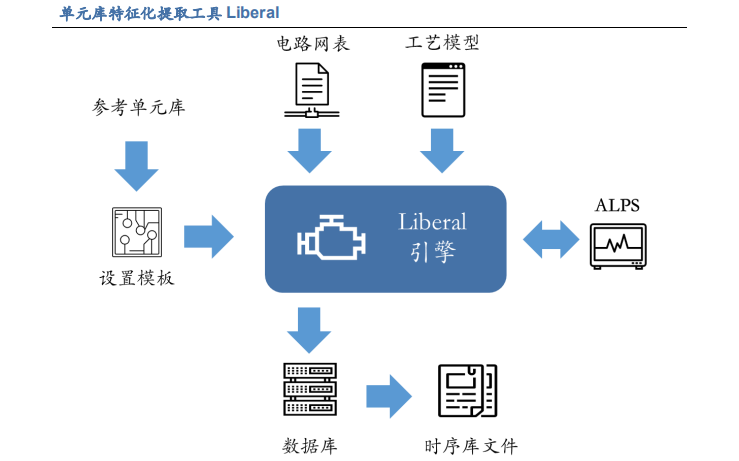

单元库特征化提取工具 Liberal:采用分布式并行调度技术,有效提升仿真效率。标准单元库是指集成电路设计过程中预先定义好的、特征化的标准模块的集合,是数字集成电路设计的基础模块。

高精度时序仿真分析工具 XTime :适应先进 5nm 制程,有效提升电路时序分析可靠性。时钟节拍是数字电路的主要驱动逻辑,而时序直接影响到芯片的功能实现和性能发挥,因此时序分析是设计流程中的关键一步。

时序功耗优化工具 XTop:依托三大核心技术,提供一站式时序功耗优化解决方案。时序和功耗是数字电路设计最重要的两大性能指标,设计者需要通过技术手段进行优化和改进。依托三大核心技术,公司的 XTop 可以针对先进工艺、大规模设计和多工作场景的时序功耗优化任务,提供一站式解决方案。

版图集成与分析工具 Skipper:高效的一站式版图集成与分析解决方案。随着芯片集成度与规模显著上升,芯片的版图数据随之剧增,常规的版图查看和编辑工具难以适应超大规模的读取和分析。

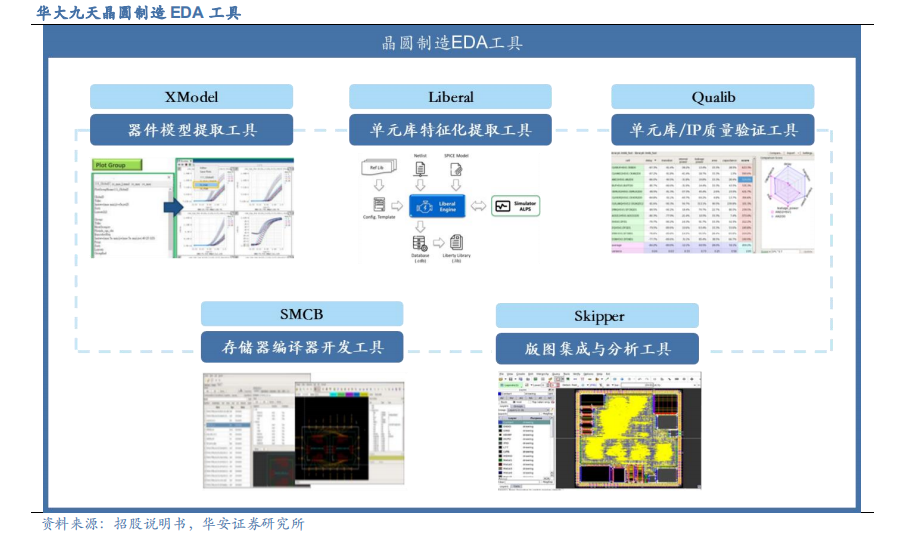

开拓晶圆制造类 EDA 业务,打造芯片设计制造的全方位解决方案。公司现有晶圆制造 EDA 工具包括器件模型提取工具、存储器编译器开发工具、单元库特征化提取工具、单元库/IP 质量验证工具、版图集成与分析工具等。伴随公司数字电路 EDA 工具研发投入的增加和研发速度的加快,晶圆制造 EDA 工具有望获得协同发展,覆盖更多制造流程,开拓更为广阔的市场。

器件模型提取工具 XModel:采用器件模型参数拟合技术,实现高效的模型拟合。器件模型是涉及工艺器件功能与性能的具体参数,精确描述器件电流电压关系,为电路仿真提供依据。工艺发展带动器件模型复杂度提升,高效的参数拟合技术成为应对器件提取难题的关键。

存储器编译器开发工具 SMCB:一站式储存器编译器开发方案。存储器编译器是用来生成不同容量储存器和相关数据文件的基础 IP,由晶圆厂提供给设计方。公司的存储器编译器开发工具 SMCB能提供电路拼接、版图拼接、特征化提取及 IP 发布等功能,形成了发布多工艺、多类型储存器编译器的一站式解决方案。

从整个产业链来看,EDA 产品开发模式为铁三角模式,EDA 的进步背后是整个产业链能力的提升。在这个三角中,第一个顶点为 EDA 厂商,其为 Fabless 提供支持;第二个顶点是 Foundry厂商,通过 Foundry 厂在工艺文件、工艺参数(PDK)上的支持,EDA 厂商才能将设计出的曲线与实际流片曲线进行拟合,吻合度越好说明工具越成熟;第三个顶点是 Fabless,其是 EDA 工具的主要使用者,EDA 的研发重点在于解决设计过程中遇到的问题,而新的问题来源都是新工艺和复杂设计,Fabless 厂商复杂设计的演进会带给 EDA 厂商新的机会和改进空间。

编辑:黄飞

-

EDA全流程的重要意义,以及国内EDA全流程进展2023-12-14 3772

-

硬件电路设计流程系列2017-10-17 3771

-

凌力尔特模拟电路设计手册:应用及解决方案指南丛书PDF2017-12-01 92632

-

【视频教程】75分钟掌握立创EDA电路设计与制作全流程2020-04-25 7234

-

新思科技发布业界首款全栈式AI驱动型EDA解决方案Synopsys.ai2023-04-03 1635

-

针对全定制模拟和混合信号设计的全流程工具平台2018-03-05 832

-

华大九天宣布IC设计解决方案已进入TowerJazz公司参考流程 通过iPDK验证2018-08-30 2520

-

一文知道EDA的设计流程2020-05-15 15920

-

CMOS模拟集成电路EDA设计技术part22022-06-27 1080

-

概伦电子正式发布EDA全流程的平台产品NanoDesigner2022-08-01 2437

-

eda技术的核心是仿真吗 EDA的四要素 EDA技术的作用2023-04-24 3873

-

国产PCB全流程电路设计解决方案2023-06-19 1239

-

师资培训 | 集成电路-华大九天模拟电路设计全流程EDA工具系统师资培训圆满结束2023-08-16 2074

-

国产EDA“夹缝”生存 集成电路设计和制造流程2023-09-28 3607

-

活动预告|多领域,全流程,华大九天多地技术研讨会邀您参与2023-12-13 982

全部0条评论

快来发表一下你的评论吧 !