在FPGA中利用CORDIC算法IP核实现三角函数关系的转换

描述

FPGA实现CORDIC核的应用和解卷绕

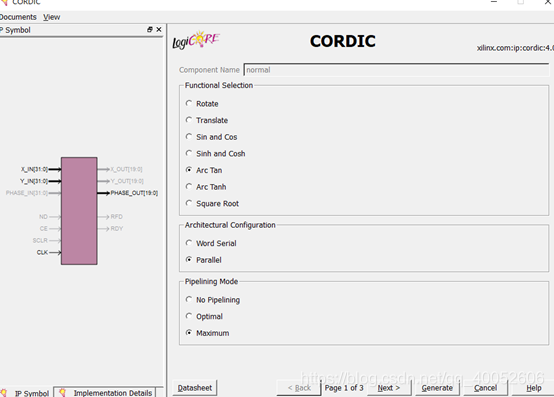

在FPGA硬件实现CORDIC的逻辑其实是很简单的,就是设置好输入输出的位宽,然后建立好对应的精度表,通过旋转加得到运算结果。但是在IP核的使用中需要特别注意输入数据的位宽和大小。IP核的申请配置如下图:

这个选项卡里主要是选择功能、处理速度和模式。

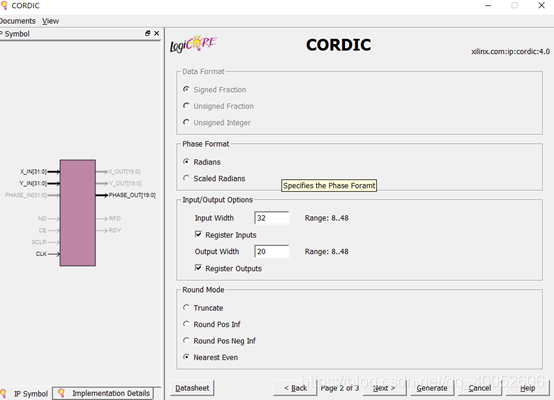

这个选项卡主要是选择弧度输出还是±1输出、输入输出位宽和截位方式,一般选择四舍五入的截位方式。

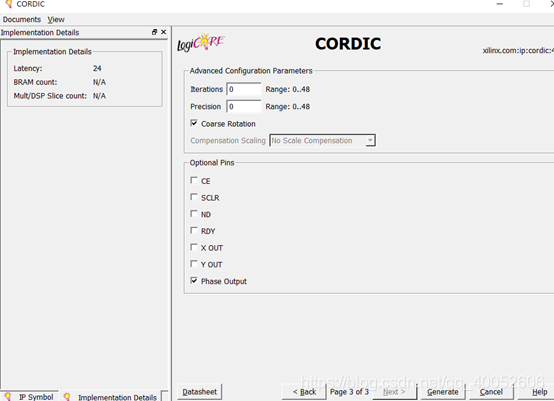

这个选项卡是配置输出项的。还需要特别注意的就是输入与输出的延时latency;

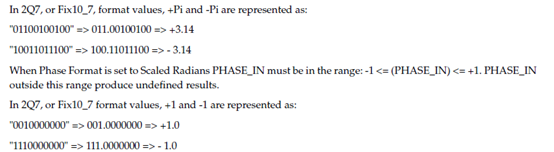

这个IP的申请比较简单,在实际仿真时需要注意的是输入数据的大小。在官方文档LogiCORE IP CORDIC v4.0中对输入数据有着很严格的规定,我们在使用时也需要严格的遵守。数据输入规定如下图:

在满足了上面IP的例化后通过modelsim仿真。分别输入两个信号,通过CORDIC核输出相位信号,仿真波形如下图:

从图中可以看出输入信号是连续的,而输出信号存在跳跃,这是因为CORDIC核只能输出-3.14到+3.14之间的信号,因此输出信号存在着卷绕现象,这样的输出结果不能反映实际的相位信息,因此需要进行解卷绕处理。

在CORDIC核输出的相位信号发声突变是在-3.14到+3.14处,因此我们只要根据突变前后数据的符号和大小即可通过加上或者减去6.28来实现解卷绕的过程。利用FPGA进行解卷绕时至少需要两个点,通过判断这两个点的符号和差值的绝对值是否等于6.28来进行确定相位突变的点和方向。在实际代码仿真可知通过两个点判断这种方式是可行的,仿真波形如下图所示:

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

RX系列三角函数单元(TFU)的使用介绍2023-12-04 4791

-

三角函数的查表法2025-11-19 272

-

ARM7如何实现三角函数2013-11-12 3177

-

FPGA设计中必须掌握的Cordic算法2019-09-19 6384

-

labview中的三角函数问题2022-04-09 10009

-

Cordic IP用户手册2023-08-09 811

-

基于DSP的三角函数快速计算2010-04-07 727

-

反三角函数arcranx运算电路2009-04-09 3110

-

利用Cordic算法来计算三角函数的值2017-11-17 7787

-

基于三角函数搜索因子的混合蛙跳算法2017-11-24 878

-

如何使用Cordic算法C语言实现三角函数的计算2019-04-25 3267

-

如何使用DSP汇编语言实现高精度的三角函数2020-08-28 3316

-

AD639:通用三角函数转换器废弃数据表2021-05-17 1605

-

TI Arm内核三角函数的优化2024-09-11 555

-

三角函数的应用广泛性:从算法设计到DSP芯片实现的探索2025-02-20 2228

全部0条评论

快来发表一下你的评论吧 !