RISC-V CPU调试机制的设计原理

处理器/DSP

899人已加入

描述

欢迎加入知识星球,带你全流程参与RISC-V SoC芯片开发。

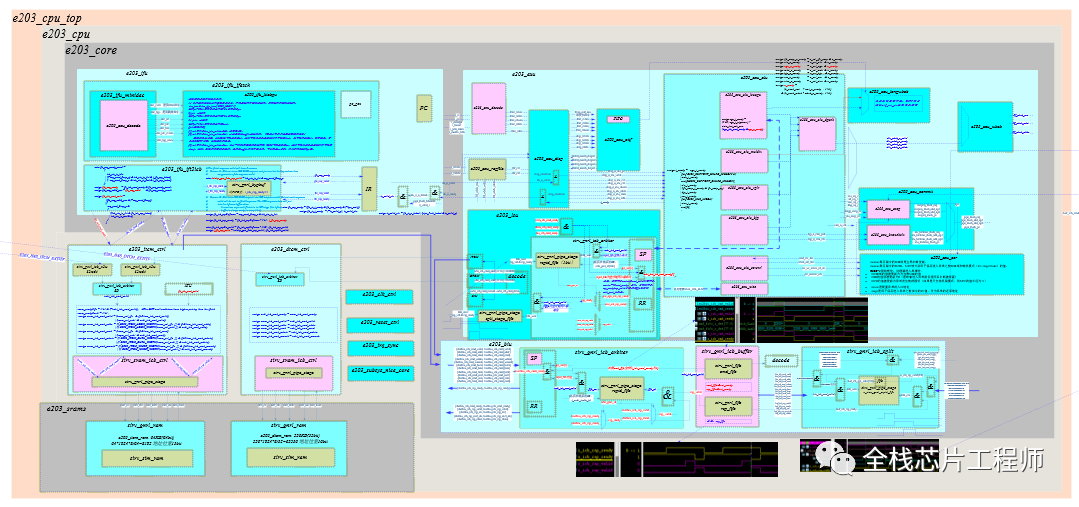

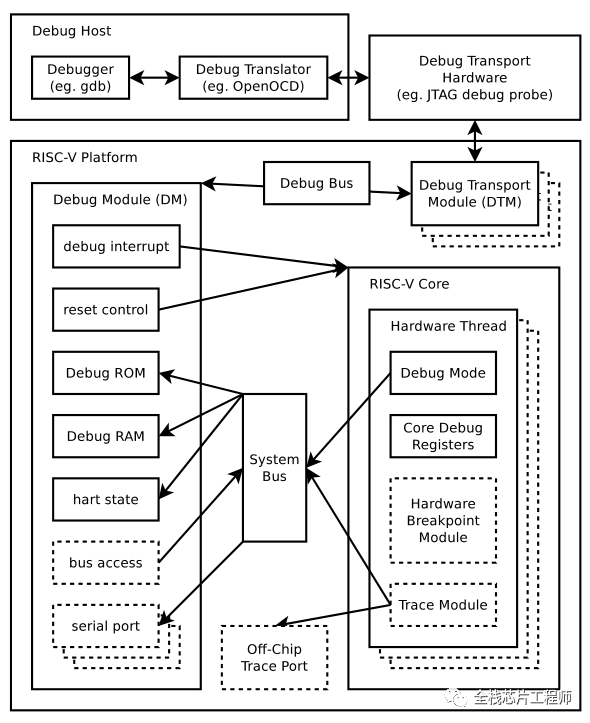

本文将详细介绍RISC-V CPU调试机制的设计原理,架构如下图:

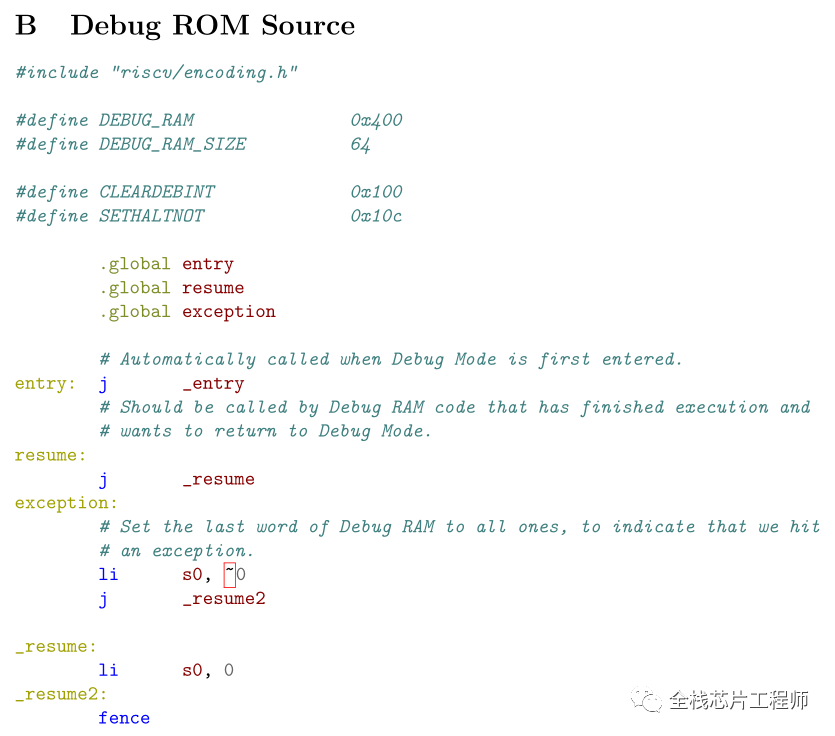

如胡振波老师所说,CPU调试机制可能比CPU core本身的调试还要费时间,cpu进入debug模式,此时pc应指向debug rom,在debug rom内,cpu会根据当前状态执行一段固定程序,程序入口包括entry、resume或exception。

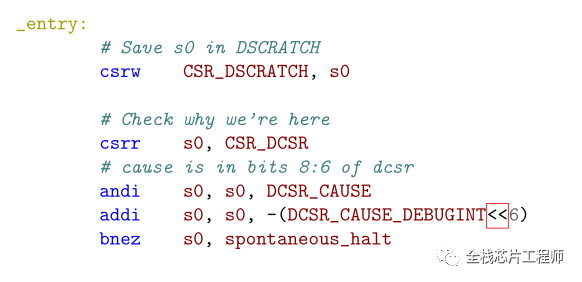

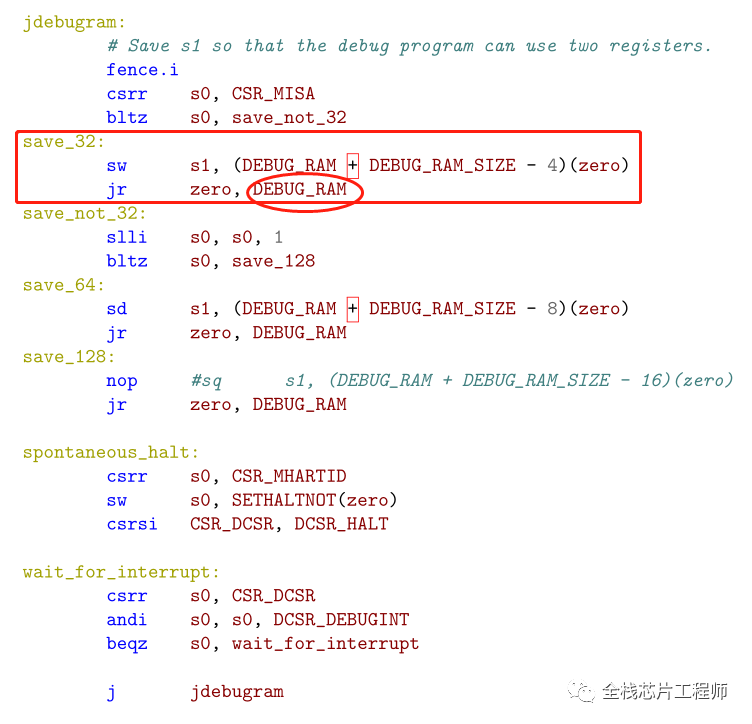

entry的作用是将s0存入CSR_DSCRATCH寄存器、然后进行状态寄存器检查、s1存到debug ram最后位置(DEBUG_RAM + DEBUG_RAM_SIZE - 4)、接着程序跳入DEBUG_RAM。

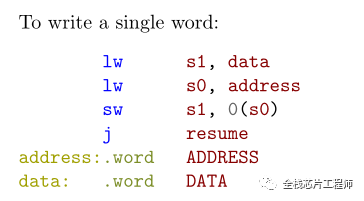

调试需要通过debug ram完成,比如,要对SoC中的寄存器或内存进行写入操作,就需要先将如下程序和数据通过dtm写入到debug ram:

为什么RISC-V External Debug Support Version 0.11nov12这个spec规定32位的risc-v至少要28byte(7 words)的debug ram?

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

RISC-V Summit China 2024 青稞RISC-V+接口PHY,赋能RISC-V高效落地2024-08-30 3670

-

Imagination CPU 系列研讨会 | RISC-V 平台的性能分析和调试2024-08-10 956

-

RISC-V为何如此重要?2024-04-29 1300

-

Imagination:RISC-V CPU的重要力量2024-03-07 1534

-

使用ANSI C代码实现RISC-V CPU内核2023-07-23 1943

-

RISC-V调试和完善的跟踪解决方案2023-07-14 547

-

RISC-V指令异常调试实例2023-06-08 3810

-

RISC-V的 CPU 验证挑战2022-07-27 3345

-

RISC-V的调试标准及跟踪技术2021-06-23 3872

-

RISC-V中国峰会:RISC-V产业及生态发展2021-06-22 3786

-

RISC-V如何填补CPU知识空白2020-09-25 3432

-

SiFive及晶心科技共同推展RISC-V_扩大RISC-V市占率2018-05-26 5125

全部0条评论

快来发表一下你的评论吧 !