怎么使用 Pin Planner 工具

描述

以前看到过官网提供excel类型的IO BANK的示意图,但是后来找不到了,就自己从软件里面生成吧,看上去都差不多,而且还附带解释图,挺好的。

FPGA Type: Cyclone V - 5CEFA7F27C6

Software: Quartus II 13.0 sp1

Steps

目前为前期评估阶段,需要对I/O的资源按照不同的BANK处理,针对一些I/O的特殊功能,及数量需求,对PCB板子布局等进行整体的规划。

PIN PLANNER

按照新建工程的向导,新建工程。这里默认已经选好指定FPGA型号了,在新建工程中选择已选型号的FPGA。

选择菜单栏 Assignments

选择 Pin Planner

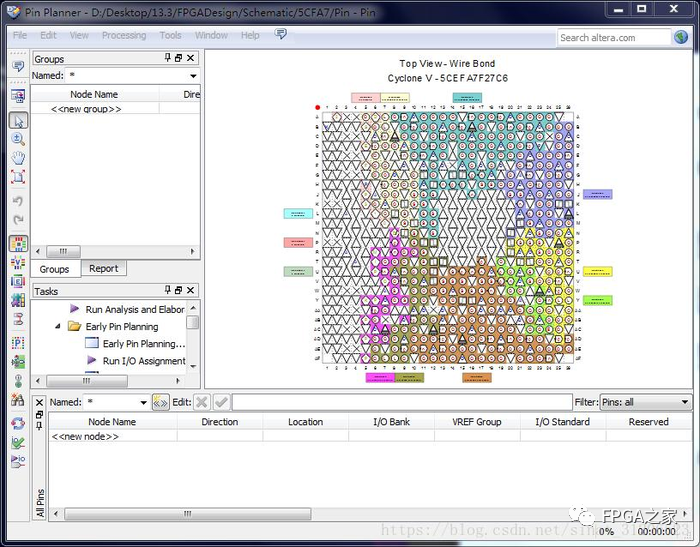

出现Pin Planner 对话框:

最大区域中的 Top View - Wire Bond 即为标注有不同BANK的IO区域分布。

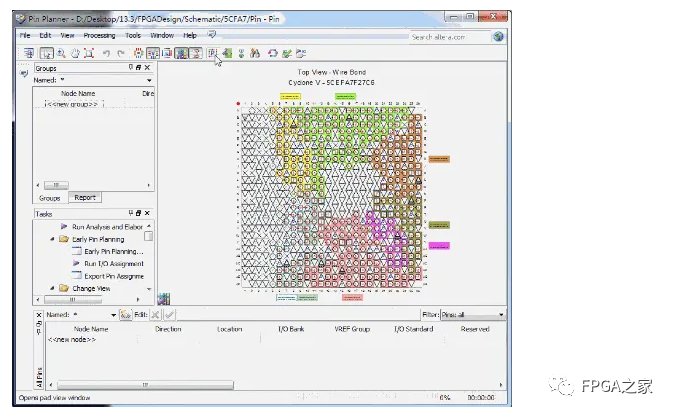

Tool Bar

工具栏中有显示的选项以供点击,也可通过菜单栏 View--> show 进行选择,详情见如下示意:

简单介绍几个Tool Bar 的按钮:

Show Differential Pin Pair Connection: 可以观察差分线的使用情况

Pin Legend Window:可以看到不同符号Pin对应的功能定义,一般的圆形为用户IO;三角形向上为power,向下为GND;正方形为clock;五边形为special configure;叉号为no connect。

Enable Live I/O check:可以检查IO的电气特征

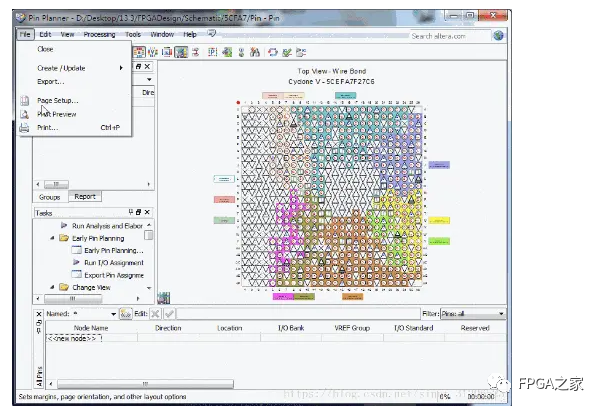

可以把 IO BANK VIEW 打印出来,注意打印的时候设置,这里页面默认为 A3 的,需要根据打印机的设备进行调整,打印出来包含 Pin Legend 的List:

也可以打印为 PDF档 ,供在PC上进行查看,需要注意黑白打印出来的颜色等级可能会混在一起,所以不好看到IO BANK的分界,如果有条件,建议彩色打印。

IO COUNT

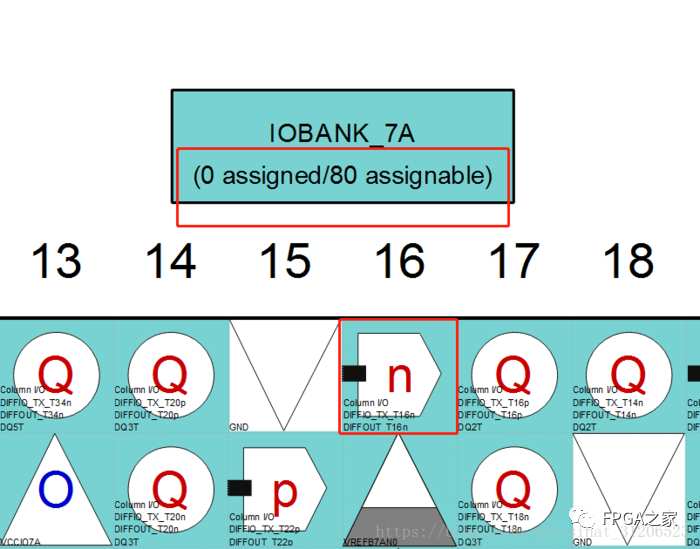

放大 IO BANK VIEW 会看到对于每个BANK 还会有详细的已使用和未使用的IO 计数。

再仔细一看,在每一个Pin上还会有 Pin Assignment ,这个软件设计时非常到位的。

I/O Distribute

因为每个BANK的Pin COUNT 并不是一致的,而且功能也是有特殊限制的,需要根据设计使用的资源,来对IO BANK进行合理的分配。

先从 I/O COUNT 上进行考虑,比如本设计需要使用3颗 SDRAM ,地址线复用,数据线不复用;这样计算地址线一共16,数据线一共 12*3 ,这一起就52个IO了,再加上其他控制PIN 10*3 ,一共80 PIN +,这样就只能选择BANK 7或者BNAK 4了;

根据PLL的分布区域,要适当的选择的区域,需要倍频的模块优先使用;

需要 mini LVDS 信号输出,那么要看IO口定义,哪些可以输出差分信号,需要注意 差分信号的时钟 分布是固定的,需要结合差分时钟来进行差分输出的BANK;

需要注意每个BANK的电压是该BANK内的 VCCIO 来决定的,结合IO输出能力,需要对不同BANK提供不同的 VCCIO ;

After All

IO 分配问题还需要单独列出来,这里主要讲述怎么使用 Pin Planner 工具。

-

西门子PCB叠层设计工具Z-planner Enterprise 2510版本的新增功能2026-01-04 409

-

浙大博导开源飞控planner源码2024-06-12 546

-

微软planner新版增强To Do功能,优化经典planner,助你更高效地工作2024-04-23 1430

-

为ROS navigation功能包添加自定义的全局路径规划器(Global Path Planner)2021-05-16 4892

-

HTG-910 Power Planner2021-01-30 739

-

Versal AI Core XCVC1902 Power Planner2021-01-28 891

-

Quartus的pin planner 变成了只读属性2018-03-14 17113

-

在quartus 15.0中如何将PPF文件导入到Pin Planner中2017-12-12 5426

-

例说FPGA连载32:PLL例化配置与LED之使用Pin Planner进行引脚分配2016-09-14 5042

-

Quartus II打开Pin Planner后在管脚分配时有一项Reserved不知道里面列表的含义2015-10-29 12901

-

chip planner的使用2013-11-15 5841

-

Pin Planner 问题2013-11-05 10273

-

Allegro FPGA System Planner中文介绍2013-04-08 3227

全部0条评论

快来发表一下你的评论吧 !