深度解析EUV光刻工艺技术

制造/封装

描述

三星电子的代工业务几个月前在国际互连技术会议 (IITC) 上发表了一篇关于 EUV 最小间距单一图案化主题的论文。一下这篇文章是为了帮助更多的人了解这篇论文,以及 EUV 技术的特点。

光刻是半导体工艺中最关键的步骤之一。EUV是当今半导体行业最热门的关键词,也是光刻技术。为了更好地理解 EUV 是什么,让我们仔细看看光刻技术。

在雕刻或切割之前,我们经常勾画出要完成的工作。通过这种方式,我们确保在我们计划的地方进行切割和雕刻。光刻与此草图步骤非常相似。半导体工艺可以描述为堆叠和切割的重复。我们使用光刻技术勾勒出这些切口的位置。

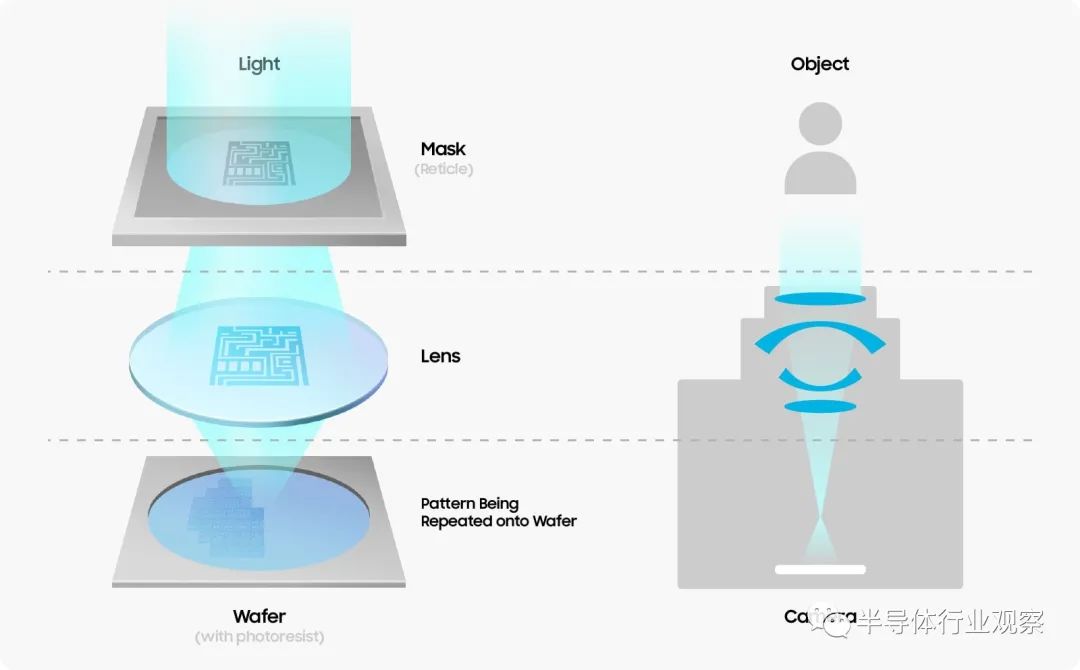

我们通常使用钢笔之类的工具来创建草图(sketch)。然而,顾名思义,在光刻中,使用光将草图印在胶片上。这可以在 [图 1] 中看到。首先,创建一个包含所需图案的薄板。板上的图案可以阻挡或让光线通过胶片,从而形成所需的图案。这种用于控制光线的板称为“掩模”或“标线”。

图1

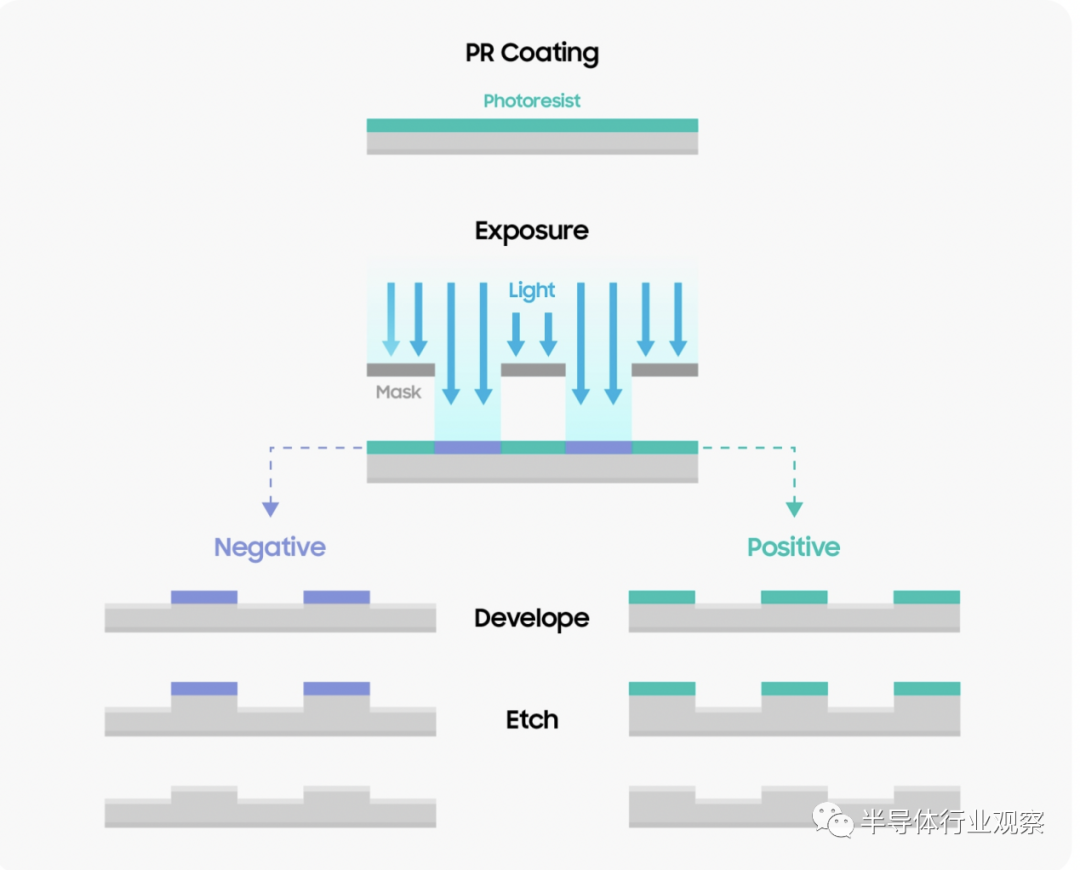

然而,简单地在纸上照射光并产生阴影不会将阴影刻在纸上。我们需要相当于相机中的胶卷来打印入射光的图案。在光刻中,PR(光刻胶)在光线照射之前应用,起到了这个作用。PR 会根据光线改变其属性。如图 [2] 所示,将 PR 应用在要切割的材料上,然后光线穿过掩模。这会改变曝光区域中 PR 的特性。这种性质的改变允许在显影步骤中选择性地去除暴露于光的 PR 或未暴露于光的 PR。换句话说,PR 被留在了掩膜的形状中。

图2

在图案化步骤之后是切割材料的步骤,称为“蚀刻”。同时对整个区域进行蚀刻(切割)。开发后剩余的 PR 可防止底层材料被切掉,并允许生成所需的草图。这是对光刻工艺的基本作用和原理的简要说明。看来光刻是一个相当简单的过程,只涉及通过掩模照射光。那么,为什么光刻技术的进步会受到半导体行业的如此关注呢?

缩小工艺规模——即使用更小的晶体管生产半导体——需要克服许多限制。障碍之一涉及光刻。那么,我们在光刻方面面临哪些障碍呢?

A. 光衍射和干涉阻碍图案化

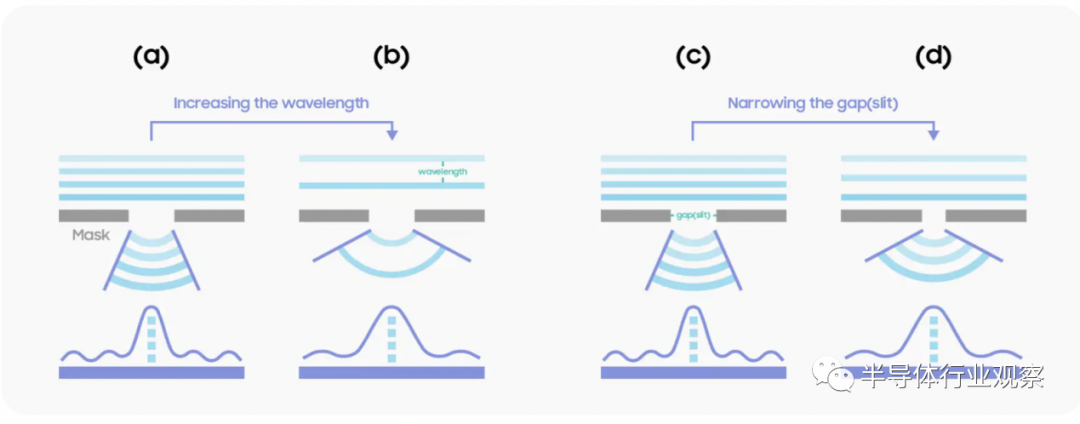

衍射是光通过狭窄狭缝时扩散的性质,而干涉是两个光波相遇并相互加强或抵消的性质。这些是目前光刻中图案化过程的两个最大障碍。如图[3]所示,光具有衍射特性,通过狭缝时不能沿直线运动。相反,它以从狭缝辐射的扇形波传播。如果狭缝窄或波长长,则衍射图案趋于更宽。

图3

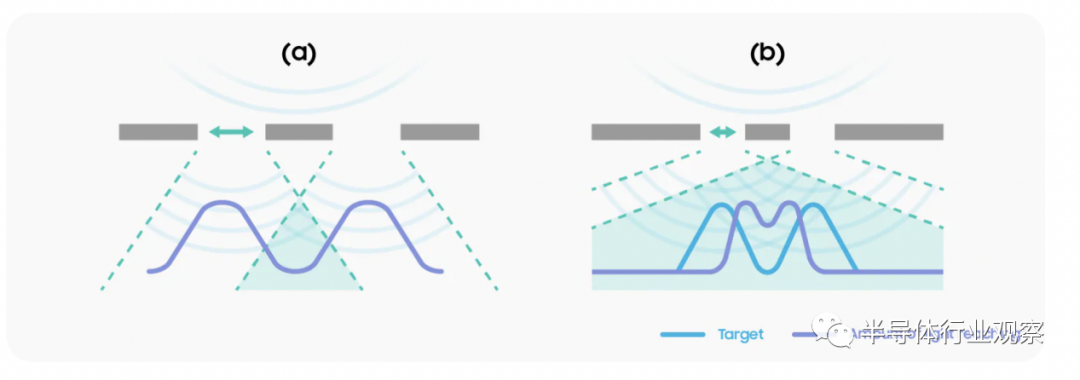

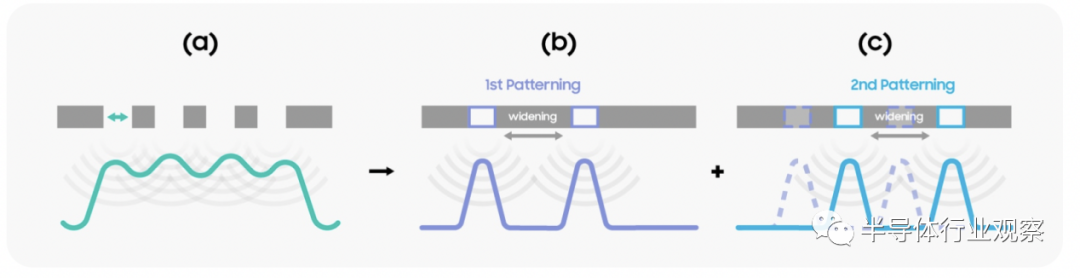

此外,当光通过两个或多个狭缝并在每个狭缝处发生衍射时,衍射图案重叠并产生干涉图案,如图 [4] 所示。当狭缝和狭缝之间的距离相对于波长足够宽时,这不是问题,如图 [4] 的 (a) 所示。但是,如果狭缝和狭缝之间的距离很窄,如 (b) 所示,就不可能在 PR 上准确地显影所需的图案。换句话说,草图上的线条越窄,线条之间的空间越小,就越难以精确地展开草图。

图4

随着工艺技术的进步,晶体管变得越来越小。因此,光刻中涉及的线变得更窄和更密集。这意味着光刻工艺的难度越来越大。我们是如何克服这些光刻障碍的?

有几种不同的方法可以克服光属性带来的限制。让我们看一些如何克服与衍射和干涉相关的问题的例子。

A.Multi Patterning Technology (MPT)

如果问题是衍射光线之间的干涉,那么也许我们可以将光线分散得更远一些?将狭缝放置得更远是克服光衍射问题的一种方法。在图 [5] (a) 中,使用 4 个狭缝进行图案化。这里,如(b)和(c)所示,4个狭缝被分成对,狭缝间隔得更远。通过以这种方式形成图案,可以减少干扰。

图5

B. OPC - 太小?让它变大。太大?让它变小!

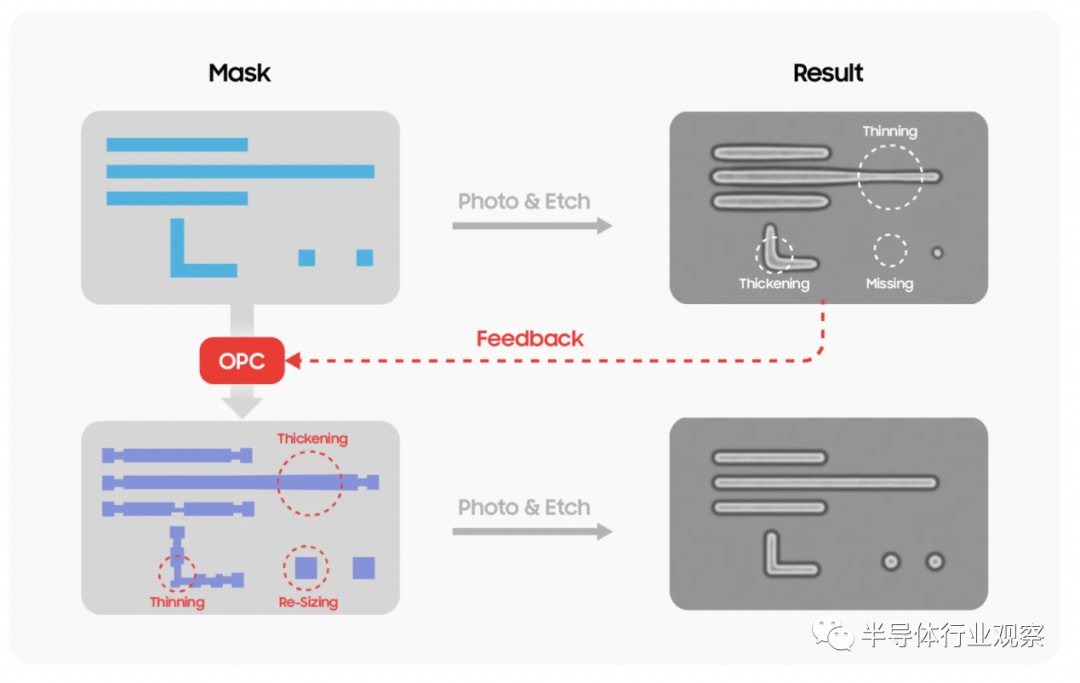

在射箭中,如果瞄准目标中心的箭在某个方向偏离了路线,我们会通过调整相反方向的目标来纠正这个错误。换句话说,我们重新计算我们的目标以补偿错误。在创建掩模以纠正图案化错误时,可以采用类似的方法。此过程称为光学接近校正 (OPC)。在这种方法中,如图 [6] 的过程所示,掩膜本身使用来自最终结果的反馈故意扭曲。

图6

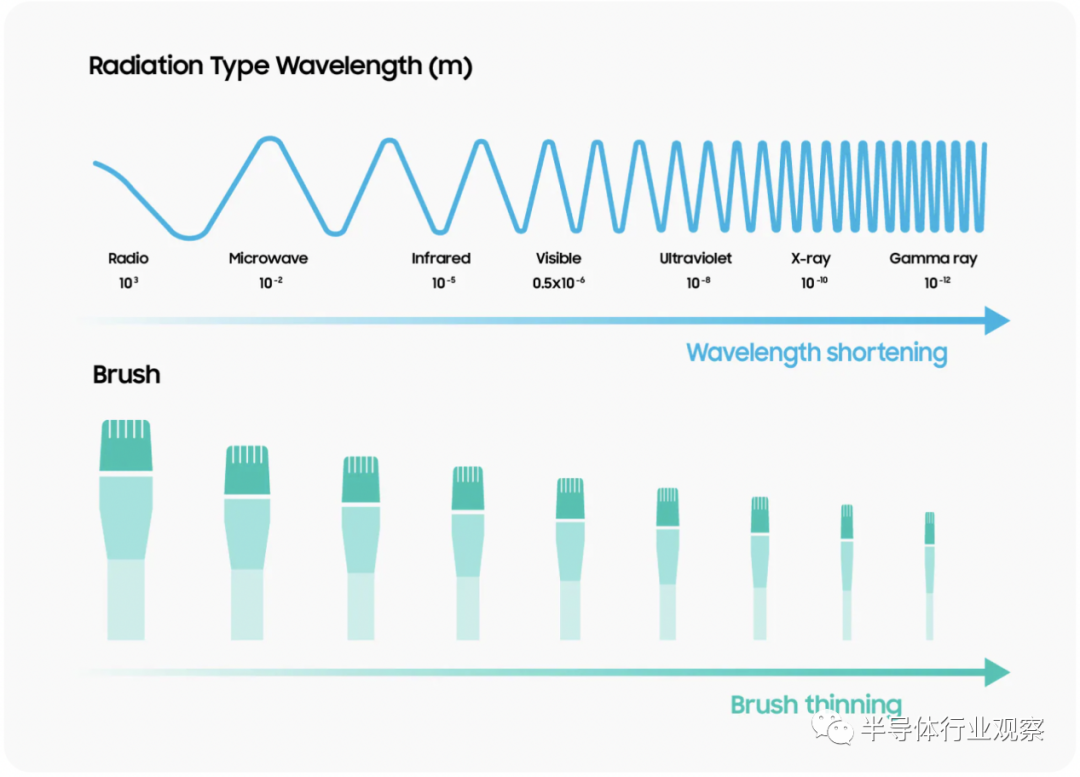

由于光的性质,我们以各种不同的方式克服了光刻工艺的限制。然而,归根结底,由光的特性引起的问题的最根本解决方案是减少波长。这是因为波长决定了衍射的程度。较短的波长使光被衍射的角度变窄,并提高了光刻工艺的性能。您需要使用更细的画笔来绘制更细的线条。如图 [7] 所示,使用较短的波长是解决较长波长造成的图案化限制的解决方案。

图7

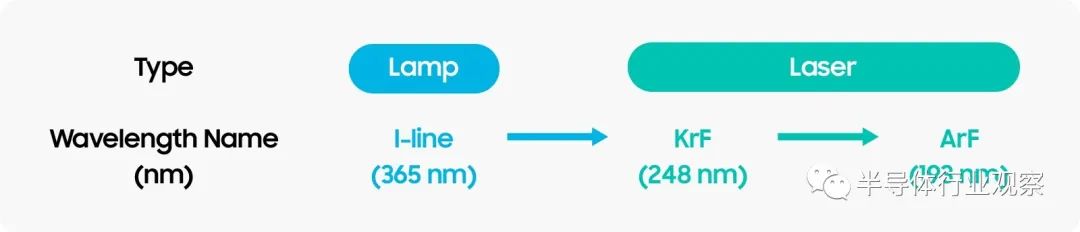

这就是为什么光刻工艺的进步涉及减少用于图案化的光的波长以绘制更小的草图,即更小的图案,如图 [8] 所示。

图8

然而,即使是 ArF 的波长(198nm)也太大,无法满足对更小晶体管的需求。这就是 EUV(极紫外)的用武之地。

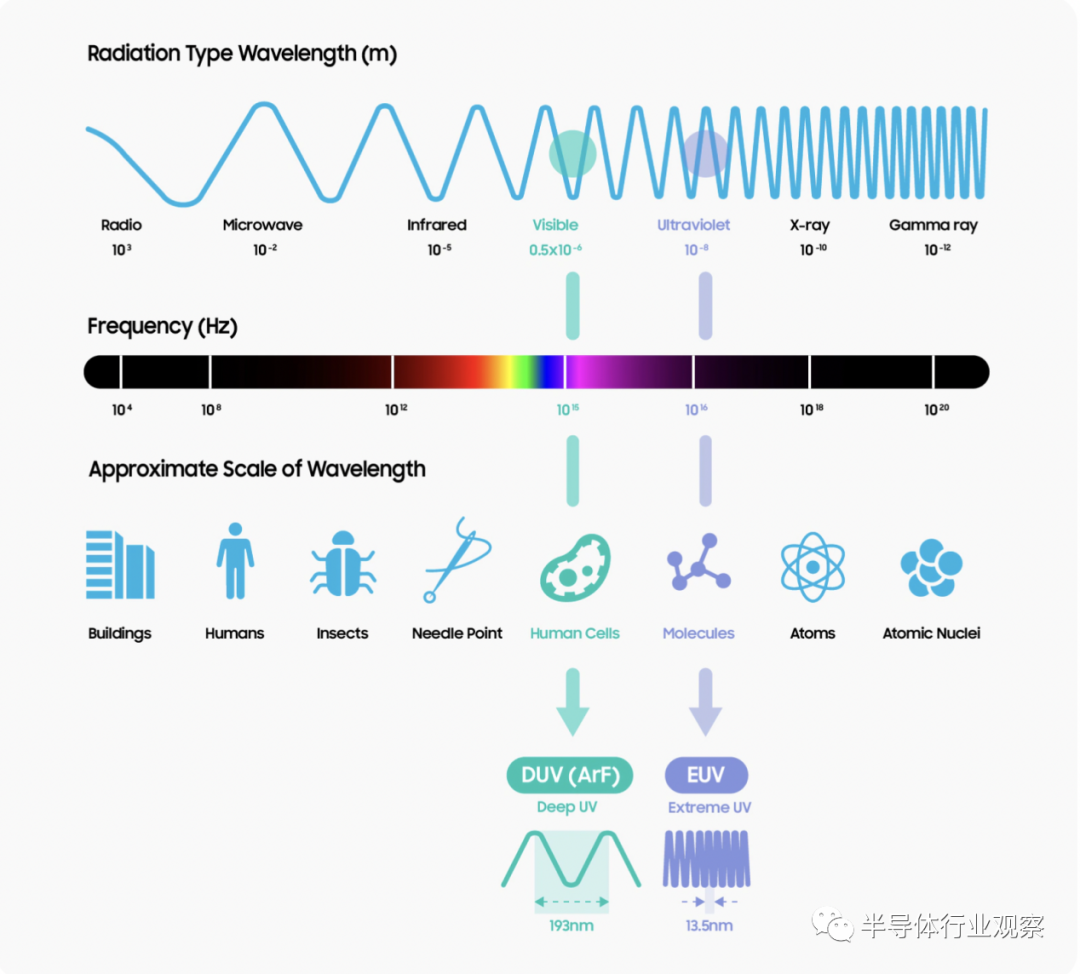

EUV 是我们一直在等待实现更短波长的解决方案。EUV 最值得注意的特点是它的短波长。精确的图案化需要短波长,而采用 EUV 的原因是为了实现更短的波长。我们使用具有 13.5nm 极短波长的 EUV,如图 [9] 所示。

图9

因此,从 193nm ArF 到 13.5nm EUV 的转变意味着一个巨大的飞跃。现在让我们仔细看看 EUV 实现的光刻工艺。

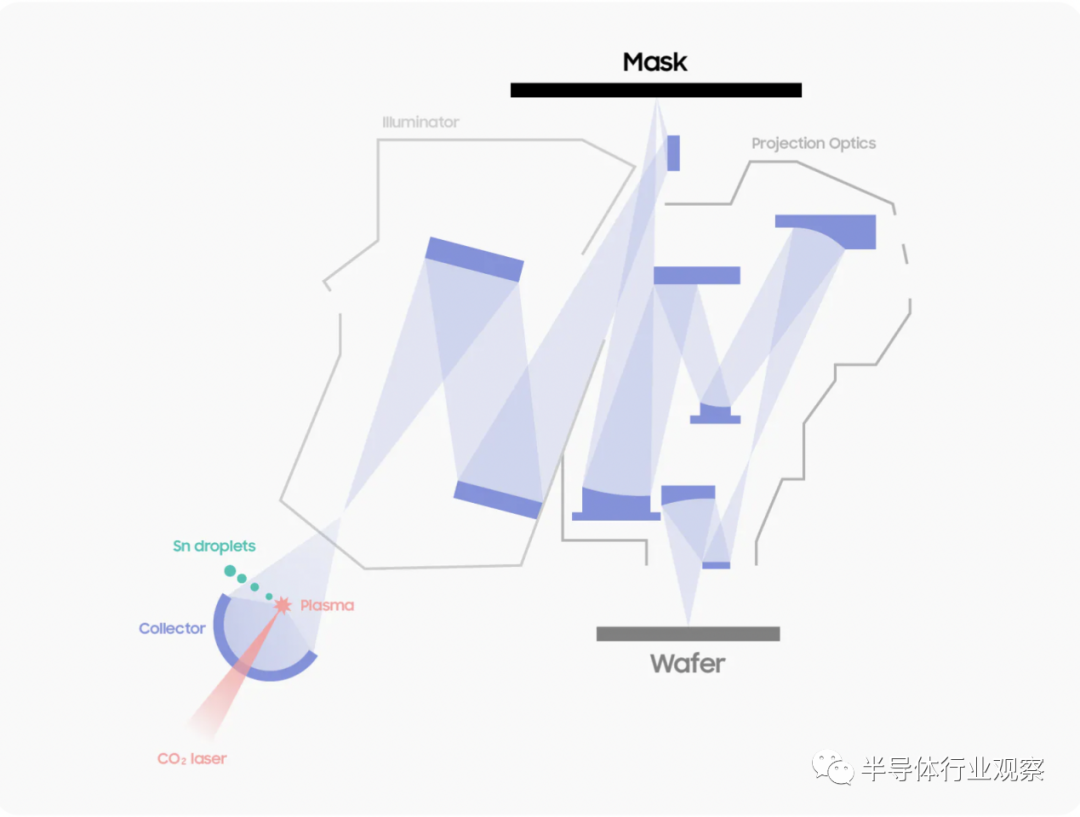

A. 高能等离子体产生的短波长

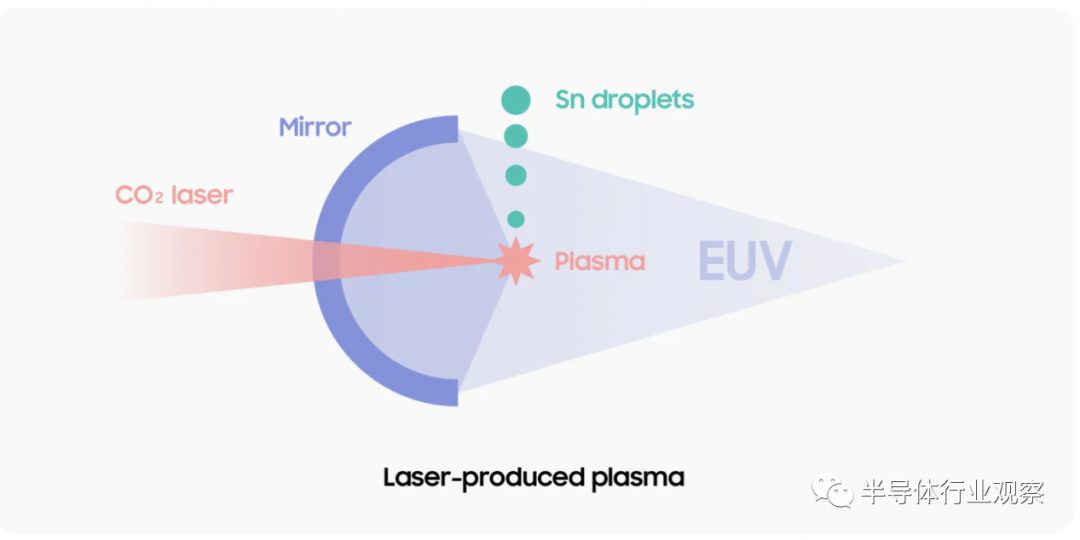

上面的图 [9] 显示了我们都熟悉的彩虹色光谱。当我们向更短的波长移动时,我们会得到紫外线,导致我们晒伤,然后是 X 射线,它可以直接穿过我们的肌肉,然后是伽马射线,它们的威力足以摧毁癌细胞。换句话说,光的波长越短,它的能量就越强。由于短波长光具有高能级,因此产生较短波长的光需要更多的能量。它类似于棒球。如果你想把球打得更远更快,那么你需要更用力地挥动球棒。但是用于产生传统 DUV 光的激光器的能量水平不足以产生我们需要的短波长。这就是为什么 EUV,如图 [10] 所示,使用等离子体(物质的第四态)。

图10

创建 EUV 的过程需要一个特殊的设备,如图 [410 所示。这个特殊的装置就是一个聚光镜。镜子不仅是创造 EUV 光的关键组件,而且在使用 EUV 光的所有过程中都是至关重要的组件。事实上,反射镜是 EUV 技术中的关键元素。下面,我们就来仔细看看镜子。

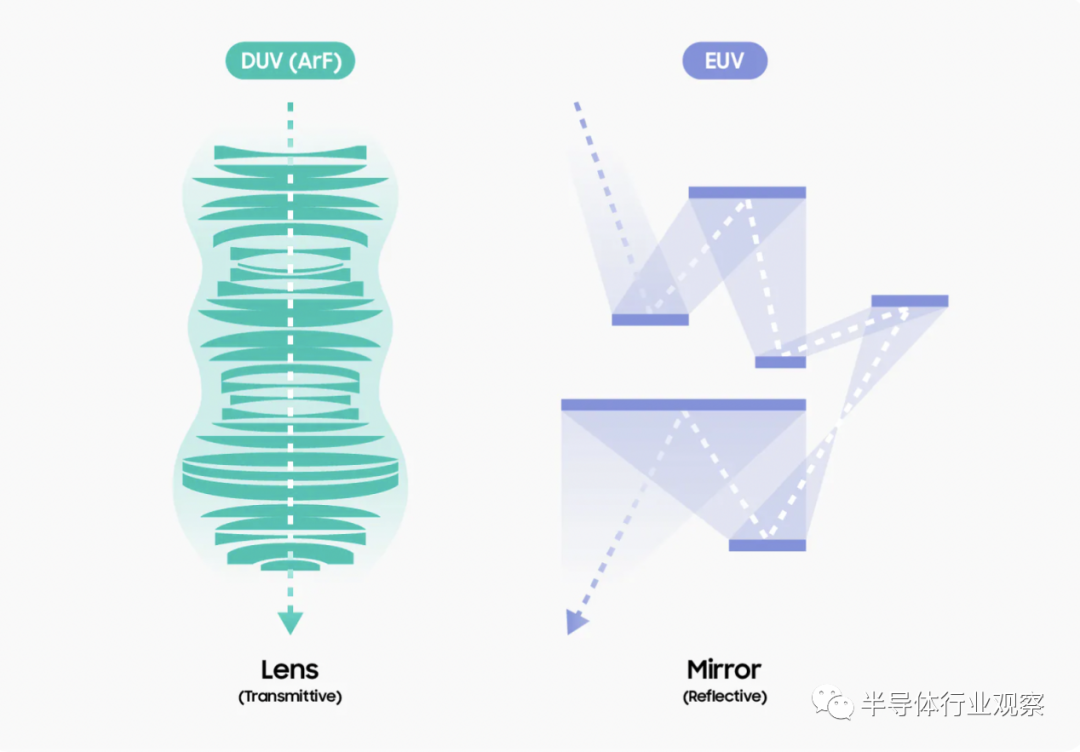

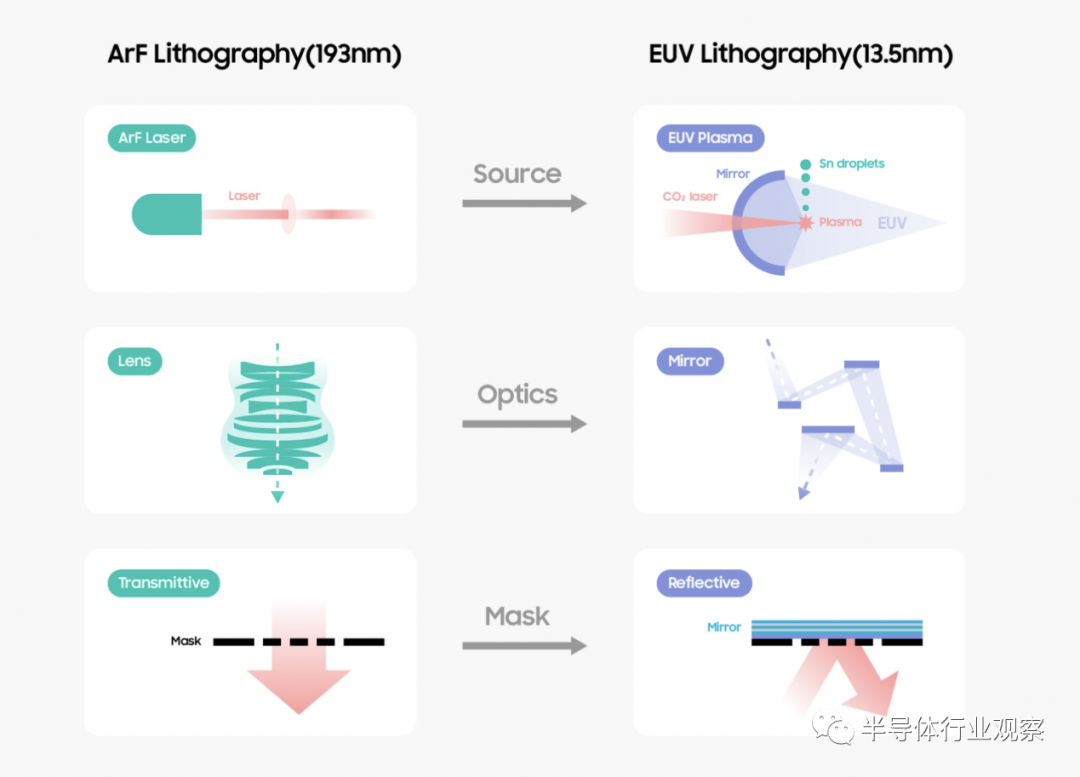

B. 反射光学系统 - 使用镜子代替透镜。

光的波长越短,就越容易被其他物质吸收。EUV 的极短波长意味着它即使在稀薄的空气中也很容易被吸收。为了避免这种情况发生,EUV 设备(使用 EUV 光的光刻设备)中的工艺在真空中进行。减少这种光吸收也是在 EUV 工艺中使用反射镜而不是透镜的原因。EUV 具有如此短的波长,以至于大部分光在通过时被透镜吸收。使用镜子反射而不是透射光可以减少 EUV 的吸收量。只有当吸收最小化并且有足够的 EUV 光到达光刻胶时,才能发生正确的图案化,如图 [11] 所示。

图11

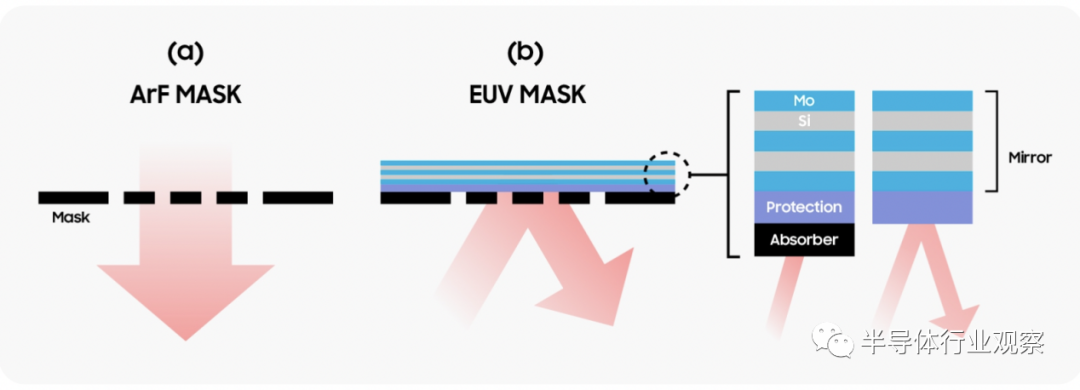

这就提出了一个问题。掩膜呢?光不应该穿过掩膜吗?这不会导致大部分 EUV 光被吸收吗?用于 EUV 工艺的掩模也可以反射光。图 [12] (a) 显示了具有透射或阻挡光的区域的传统掩模。在 EUV 工艺中,掩模由反射或吸收光的区域组成。

图12

图 [13] 一目了然地说明了迄今为止解释的 EUV 光刻工艺。

图 [14] 简要回顾了 EUV 和 ArF 之间的差异。

如图 [14] 所示,EUV 光刻工艺与传统方法完全不同。使用这个过程,我们能够以比以前小得多的比例绘制图案。但允许比以往更小的图案并不是 EUV 的唯一优势。

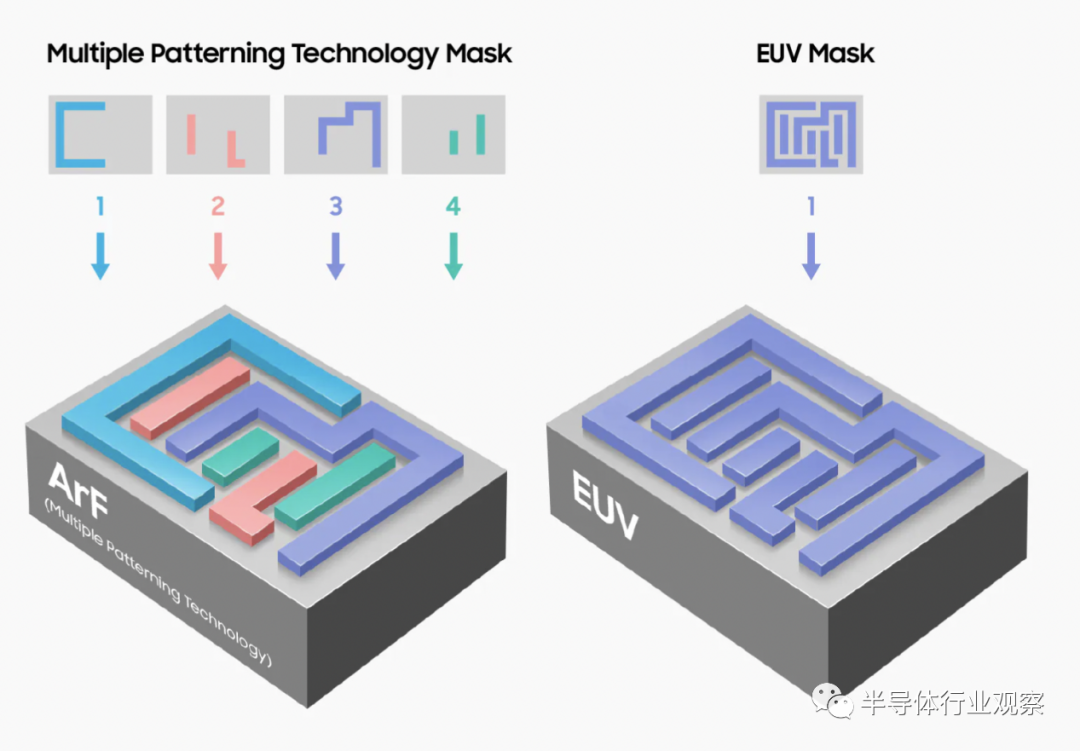

在钱文忠,我们讨论了一种使用多遍来创建图案的方法。这种方法旨在克服较长波长带来的限制,称为 MPT(多重图案化技术)。虽然 MPT 允许绘制小图案,但它也有其缺点。如图 [15] (a) 所示,该过程需要多个掩膜,并且还涉及多个通过(步骤)。但如图 [15] (b) 所示,EUV 的短波长允许仅使用单个掩模和单程光刻工艺来创建图案。

图15

这一优势转化为时间、产量和成本方面的优势。

A. 时间 - 减少过程时间要求

自然,获得结果所需的步骤越多,过程就越耗时。图 [15] 的一个简单比喻是面包店。在 (a) 中,面包店每四个小时制作一条面包。但在 (b) 中,面包店每小时生产一条面包。步骤要求的减少允许更快的处理速度。

B. 良率- 减少污染以提高良率

多次通过意味着增加污染的可能性。它就像橡皮泥——你玩得越多,它就会变得越脏。在半导体工艺中,污染会降低产量。减少通过次数有效地消除了多个影响良率的因素。

C. 成本 - 降低掩膜生产成本

掩膜生产也涉及成本。EUV 用单一掩模代替了先前技术的多个掩模,因此也实现了掩模生产成本的节省。

EUV 的出现带来了许多显着的优势。现在,我们需要探索和开发更有效地利用这一出色工具的方法。

编辑:黄飞

-

EUV光刻工艺可用到2030年的1.5nm节点2017-01-22 3812

-

光刻工艺的基本步骤2022-10-18 17680

-

EUV热潮不断 中国如何推进半导体设备产业发展?2017-11-14 6839

-

光刻机工艺的原理及设备2020-07-07 17525

-

光刻工艺步骤2021-01-12 4477

-

超细线蚀刻工艺技术介绍2010-03-30 2131

-

光刻胶与光刻工艺技术2011-03-09 1779

-

EUV光刻工艺终于商业化 新一代EUV光刻工艺正在筹备2018-10-30 4460

-

三星扩大部署EUV光刻工艺2020-12-04 2850

-

EUV照片源2022-06-13 539

-

euv光刻机可以干什么 光刻工艺原理2022-07-06 8530

-

半导体制造工艺之光刻工艺详解2023-08-24 3356

-

三星D1a nm LPDDR5X器件的EUV光刻工艺2023-11-23 2303

-

光刻工艺的基本知识2024-08-26 3860

-

光刻工艺中的显影技术2025-06-09 3342

全部0条评论

快来发表一下你的评论吧 !