详解80C51单片机的四种I/O口

控制/MCU

描述

在80C51单片机中有4个双向的8位I/O口P0~P3,在无片外存储器的系统中,这4个I/O口的每一位都可以作为准双向通用I/O使用。

在具有片外存储器的系统中,P0口作为地址线的低8位以及双向数据总线,P2口作为高8位的地址线。这4个I/O口除了可以按字节寻址外,还可以按位寻址。

P0口

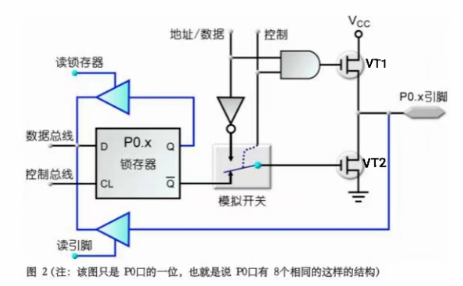

下图给出了P0口的逻辑结构,它由一个锁存器,两个三态输入缓冲器,一个多路复用开关,一个与门,一个非门以及控制电路和驱动电路组成。

“锁存器,是数字电路中的一种具有记忆功能的逻辑元件。锁存,就是把信号暂存以维持某种电平状态,在数字电路中则可以记录二进制数字信号"0"和"1"。

只有在有锁存信号时输入的状态被保存到输出,直到下一个锁存信号。通常只有0和1两个值。

三态缓冲器(Three-state buffer),又称为三态门、三态驱动器,其三态输出受到使能输出端的控制。

当使能输出有效时,器件实现正常逻辑状态输出(逻辑0、逻辑1),当使能输入无效时,输出处于高阻状态,即等效于与所连的电路断开。”

P0口可以作为输入或输出口,在实际应用中通常作为地址/数据复用总线。

在访问外部存储器时,P0口才是真正的双向口。

当P0口输出地址/数据信息时,此时控制信号线为高电平,模拟开关将地址/数据线与场效应管VT2接通,同时与门输出有效,输出结果由地址/数据线信号决定。

与门输出的地址/数据信息去驱动VT1,同时通过非门反相信号后驱动VT2。VT1与与VT2为推拉结构,同一时刻,只有一个管能导通。若地址/数据线为1,则VT1导通,VT2截止,P0口输出高电平;反之输出低电平。

当数据从P0口输入时,读引脚使三态缓冲器打开,端口上的数据经三态缓冲器后送到内部的数据总线,完成读引脚。

当P0口作为通用I/O时,CPU向端口输出数据,此时控制信号为低电平,模拟开关与锁存器的反相端连接,写信号与锁存器的控制总线(时钟线)相连,于是内部数据总线上的数据经反相后出现在VT2端,再经VT2反相后输出到P0端口,输出的数据经过两次反相后相位不变。

由于VT2位漏极开路输出,为了完成VT2反相功能,此时需要外接上拉电阻。

当P0口作为输入时,由于信号加载在VT2上被送入三态缓冲器,若该接口此前刚锁存过数据0,则VT2是导通的,VT2的输出被钳位在0,此时输入的1无法读入,所以当P0口作为通用I/O时,在输入数据之前,必须先向端口写1,使VT2截止。不过当在访问外部程序存储器时,CPU会自动向P0口写1。

有时需要先将端口的数据写入,经过修改后再输出到端口,若此时P0口的负载正好是晶体管的基极,并且其输出为1,这必然导致该引脚为低,若此时读取引脚信号,则会将刚输出的1误读为0,为了避免这类误读的错误,于是单片机还提供了读锁存器的功能。

例如执行INC P0时,CPU先读P0锁存器中的数据,然后再执行加1操作,最后将结果送回P0口,这样单片机从结构上满足了读改写这类操作的需要。

P1口

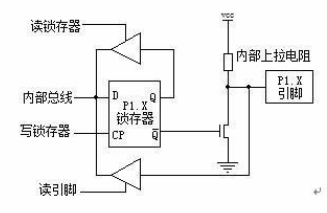

P1口是一个准双向口,通常作为通用I/O使用,结构图如下。

由于在其输出端接有上拉电阻,故可以直接输出而不需要外接上拉电阻。

同P0口一样,当做输出口时,必须先向端口写1,使场效应管截止。同时,它可以被任何数字逻辑电路驱动,包括TTL电路,MOS电路和OC电路。

P2口

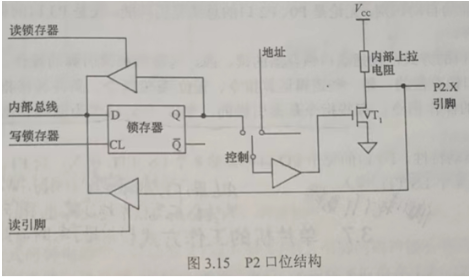

P2口位结构图如下。

P2口作为一个准双向口,其位结构与P0口相似,当系统外接片外存储器时,它输出高8位地址,此时开关在CPU的控制下接通地址信号。

同时它还可以作为通用I/O使用,此时开关接通锁存器的Q端。对于80C51单片机来说,P2口通常用作地址信号输出。

P3口

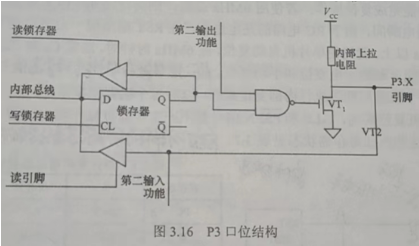

P3口位结构图如下。

P3口位双功能口,当P3口作为通用I/O口使用时,它为准双向口,且每位都可定义为输入或输出,其工作原理与P1口类似。

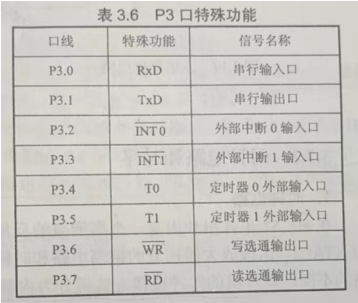

P3口还有第二功能,其引脚描述如下表:

对于输出而言,此时相应位的锁存器由CPU自动输出1,有效输出第二功能。

对于输入而言,无论该位是作为通用输入口还是第二功能输入口,相应的锁存器和选择输出功能端都应置1,该工作在开机或复位时CPU自动完成。

80C51系列单片机的并行I/O接口有以下应用特性:1)P0,P1,P2,P3作为通用双向I/O口使用时,输入操作是读引脚状态;输出操作是对口的锁存器的写入操作,锁存器状态立即反映到引脚上;

2)P1,P2,P3作为输出口时,由于电路内部带上拉电阻,因此无须外接上拉电阻。

3)P0,P1,P2,P3作为通用输入口时,必须使电路中的锁存器写入高电平1。

4)I/O口功能自动识别,无论是P0,P2的总线复用功能,还是P3口的第二功能复用,单片机会自动选择。

5)两种读端口的方式,包括端口锁存器的读、改,写操作和读引脚操作。在单片机中,有些指令是读端口锁存器的,如一些逻辑运算指令,置位/复位指令,条件转移指令以及将I/O口作为目的地址的操作指令;有些指令是读引脚的,如以I/O口作为源操作数的指令MOV A,P1。

6)I/O的驱动特性。由于P1,P2,P3口内部带上拉电阻,其引脚拉出电流能力弱,吸入电流能力强,也就是输出驱动能力弱,可驱动4个LS TTL输入;而P0口每个I/O可以驱动8个LS TTL输入。

-

80c51是几位单片机 80c51单片机有几个中断源2023-03-31 8117

-

80C51单片机的最小系统2021-11-11 2306

-

80C51单片机串行通信讲解2021-09-30 1566

-

80C51单片机与8051单片机的区别是什么2019-08-27 9962

-

80C51单片机的串行口结构和原理的程序免费下载2019-07-15 1375

-

51单片机教程之80C51单片机的串行口介绍及如何进行串行总线的扩展2018-12-05 3323

-

51单片机教程之80C51的结构与原理知识点概述课件免费下载2018-11-29 1434

-

单片机教程之80C51的中断系统及定时和计数器的详细资料概述2018-11-13 1739

-

51单片机教程之80C51单片机的指令系统2018-10-26 1849

-

80C51单片机的硬件结构是怎么样的?2018-09-20 1968

-

80C51单片机的内部结构2017-03-25 9578

-

80c51单片机和c8051单片机的区别2016-03-22 1681

-

基于HYM8563的80C51系列单片机低功耗系统设计2009-10-16 3418

全部0条评论

快来发表一下你的评论吧 !