什么是时钟缓冲器(Buffer)?时钟缓冲器(Buffer)参数解析

电子常识

描述

什么是时钟缓冲器(Buffer)?时钟缓冲器(Buffer)参数解析

什么是时钟缓冲器(Buffer)?我们先把这个概念搞清楚。

时钟缓冲器就是常说的Clock Buffer,通常是指基于非PLL的扇出型缓冲器,是一种将一路时钟源信号通过频率复制生成多路时钟信号的器件,通常时钟缓冲器还兼具有时钟分配,格式转换和电平转换的功能。

对于需要多路时钟信号的电子系统来说,时钟源加时钟缓冲器的方案可以有效降低系统成本,简化电路设计,为系统多个组件提供多路参考时钟。时钟缓冲器功能虽然简单,但使用中同样有挑战。下面从几个关键指标看时钟缓冲器对时钟系统的影响。

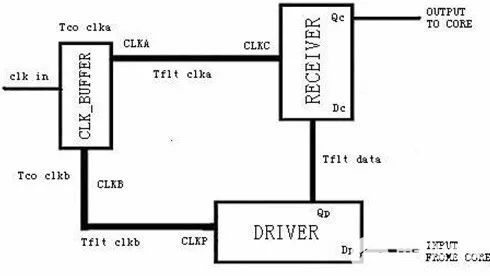

时钟缓冲器输出偏移

首先,如果多路时钟输出被分别用在通信的驱动端和接收端做参考时钟,那么输出之间的skew就变得十分重要。这个值会减小数据建立保持时间的裕量,特别是对高速数据接口来说,整个时间窗口(T)变小,每一部分的预算都很有限,这是就需要关注缓冲器的这个参数对系统的影响。

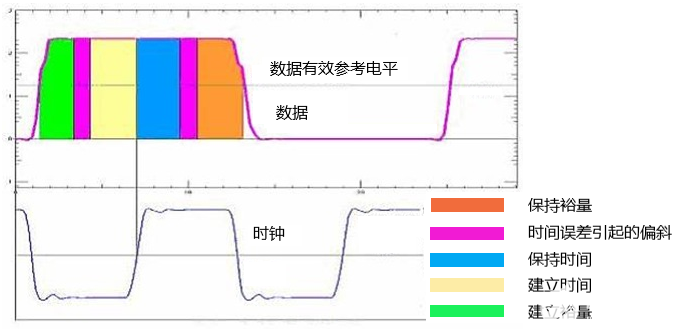

外同步时钟源建立保持时间

时钟缓冲器附加抖动

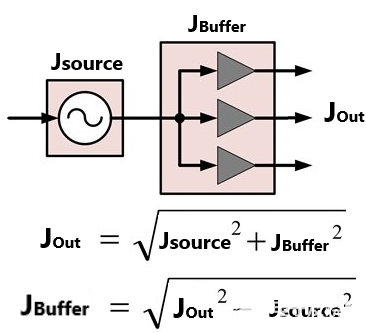

其次,时钟源经过缓冲器后,缓冲器本身的抖动会增加到时钟的内在抖动上,从而恶化整个系统时钟的相位噪声,这个参数定义为缓冲器的附加抖动或者在指定频带范围内的附加相位噪声。

时钟缓冲器本身不产生时钟信号,除非有输入信号,否则不能测量相位抖动。为了定性分析缓冲器对于相位抖动的影响,必须首先测量时钟源的相位抖动,然后是时钟源和缓冲器一起工作时的相位抖动,缓冲器的相位抖动可以通过公式计算出来。在计算相位抖动时通常做的假设是时钟源和缓冲器噪声不相关,而且由纯粹的随机抖动组成。

附加抖动计算方法

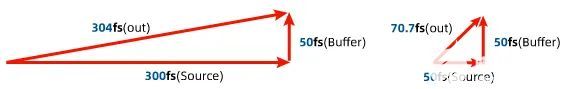

从以上公式可以推导出一个很有趣的现象,如果时钟源的抖动300fs,经过附加抖动为50fs的缓冲器后,理论上输出的总抖动为304fs,会发现实际恶化的程度并不高。如果时钟源抖动为50fs,经过同样的缓冲器后,输出总抖动为70.7fs,整体恶化了20多fs。由此可见当时钟源抖动很小时,缓冲器的附加抖动对整个系统的恶化程度就会非常显著。

我们再从测量误差的角度展开一下,假如系统测量有±1fs的误差,第一个测试系统中测得的总抖动是303fs-305fs的话,计算得出的缓冲器附加抖动是42.5fs-55fs,实际误差-7.5fs到5fs。对于第二个测试系统来说,69.7fs-71.7fs的总抖动,计算得出的缓冲器附加抖动是48.5fs-51.4fs,实际误差只有-1.5fs到1.4fs。从这个角度看,测试系统尽量选择抖动小的时钟源。

不同时钟源抖动测试系统对比

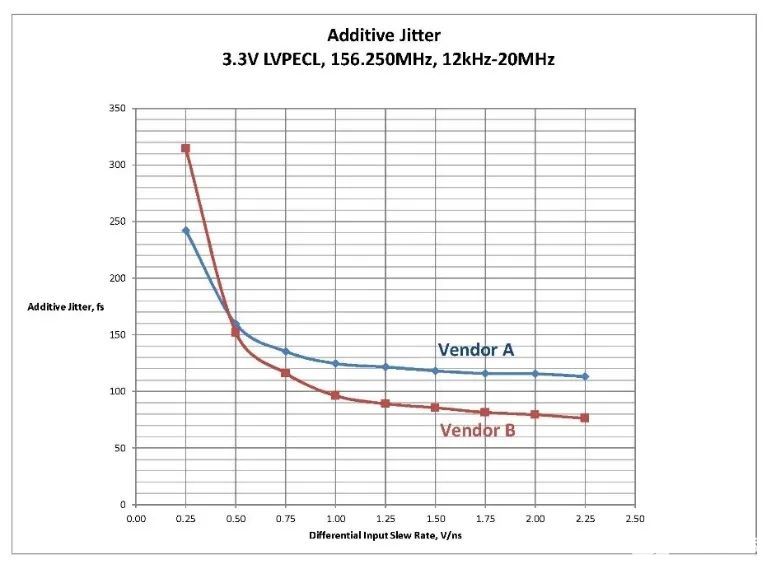

当然附加抖动性能还和输入时钟的信号转换率(slew rate)强相关,较低的slew rate通常导致较高的附加抖动。同时不同的缓冲器,对于不同的slew rate时钟源,其附加抖动的性能差异也很大,大家可以参考有关文献进一步深入理解。

两个不同时钟缓冲器的附加相位抖动对比输入时钟的信号转换率slew-rate

时钟缓冲器其它主要参数

● 可支持的输入时钟源的类型:单端,差分,晶体输入等

● 支持输出的时钟路数:5路,10路等

● 支持输出的时钟信号类型:LVPECL,LVDS,LVCMOS等

时钟缓冲器的选择

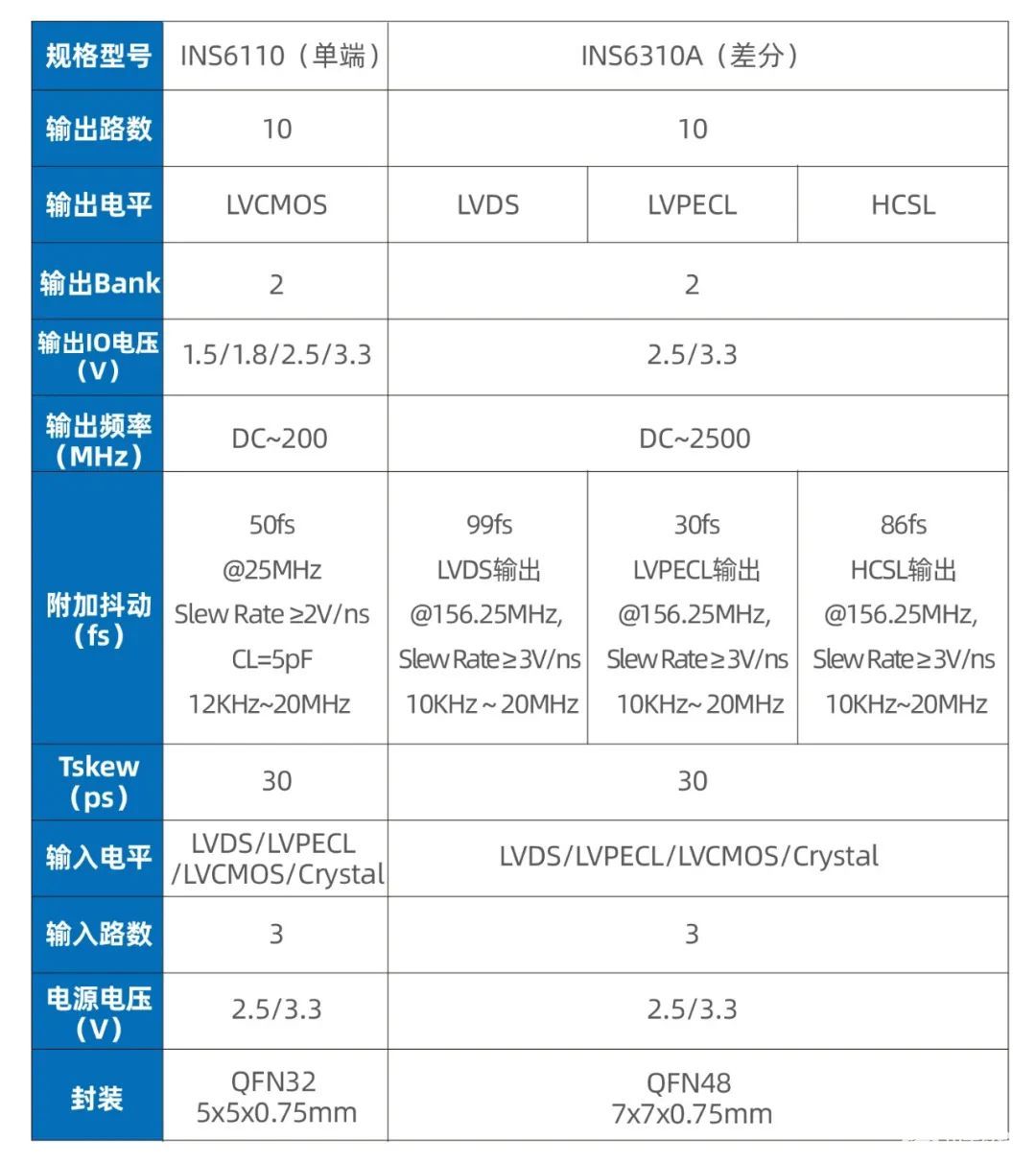

多年来,大普通信持续保持研发高投入,继1:10单端时钟缓冲器INS6110之后,又新推出了一款1:10差分输出缓冲器INS6310A,对标市场主流应用型号,为无线基站BBU&RRU、有线通信、数据存储、服务器和高速以太网等众多应用场景提供更多选择。

INS6110和INS6310A都是基于非PLL的扇出型缓冲器,时钟输出有两个独立的区,每个区都具备独立于内核电压的专用电源电压引脚,可启动简单的电压电平转换。器件的通用输入级可支持两个差分或单端输入和一路晶体输入,低噪声2:1输入复用器支持无差错切换,可消除输入时钟切换期间无效脉冲传输到器件输出端的风险。INS6310A差分输出可以按Bank分别配置为LVDS,LVPECL或HCSL输出格式。具体参数参考下表:

来源:大普通信

-

时钟缓冲器与时钟发生器各自优势介绍2026-03-12 458

-

高性能时钟缓冲器CDCVF310:特性、参数与应用解析2026-02-10 259

-

时钟缓冲器技术选型与设计要点2025-12-16 593

-

时钟缓冲器的应用场景及如何选择合适的时钟缓冲器?2025-10-30 641

-

浙江赛思电子时钟缓冲器的应用条件2025-09-04 1034

-

时钟缓冲器工作原理及常见时钟缓冲器的国产替代情况2025-02-17 2684

-

缓冲器是干嘛的2024-06-10 12206

-

buffer缓冲器电路图与buffer电路示意图2022-10-18 48020

-

使用IDT时钟缓冲器提升应用设计2022-05-05 3015

-

时钟缓冲器选型目录2021-11-19 2460

-

如何测量时钟扇出缓冲器的残余噪声?2018-08-13 4685

-

芯科实验室推出业界首款通用时钟缓冲器Si533xx2012-11-06 6500

-

缓冲器,缓冲器是什么?2010-03-08 2881

-

单位增益缓冲器:The Unity-Gain Buffer2009-05-16 18105

全部0条评论

快来发表一下你的评论吧 !