buffer缓冲器电路图与buffer电路示意图

信号处理电子电路图

描述

buffer缓冲器电路图与buffer电路示意图

buffer缓冲器的作用

buffer译名为: 缓冲,缓冲器,缓冲液;

buffer缓冲器的作用是什么?

比如在数据传输中,用来弥补不同数据处理速率速度差距的存储装置叫做缓冲器。把数据存放到缓冲器中的技术叫做缓冲。

比如缓冲寄存器又称缓冲器,它分输入缓冲器和输出缓冲器两种。前者的作用是将外设送来的数据暂时存放,以便处理器将它取走;后者的作用是用来暂时存放处理器送往外设的数据。有了数控缓冲器,就可以使高速工作的CPU与慢速工作的外设起协调和缓冲作用,实现数据传送的同步。由于缓冲器接在数据总线上,故必须具有三态输出功能。

buffer缓冲器电路图与buffer电路示意图

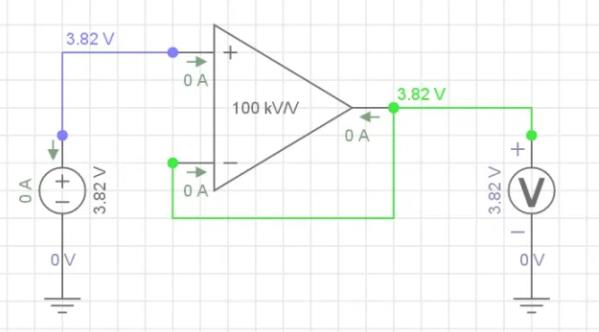

运放作为缓冲器的电路

对于缓冲器电路,由于输出直接连接了反相输入,根据上述两条原则,所以Vout = Vin+ = Vin-。在该电路中运放起阻抗变换的作用。

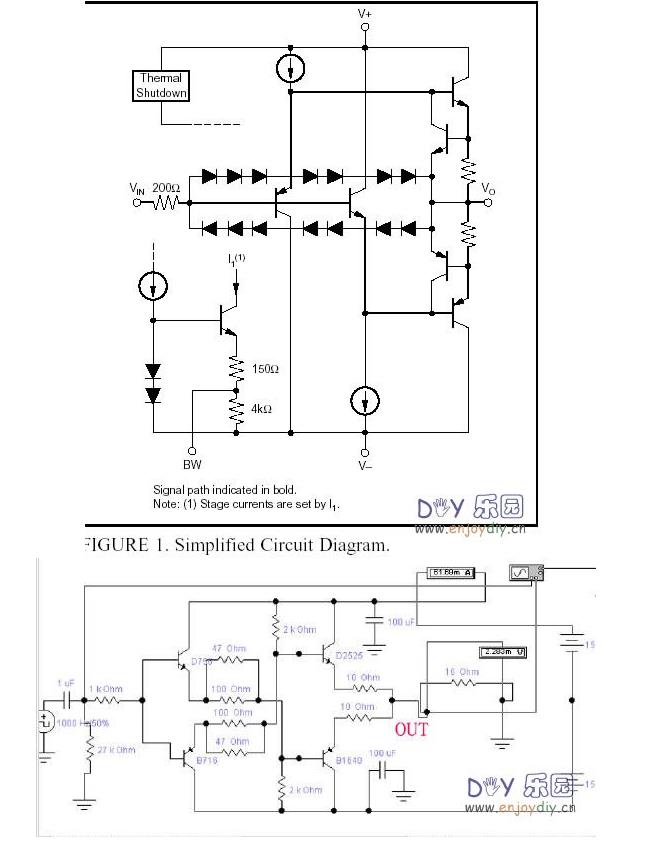

上图是Buffer在录音输入端的应用;设置在前置放大器内,可以使得信号不减弱。

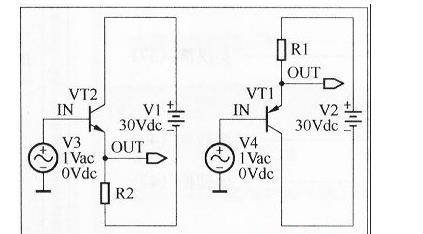

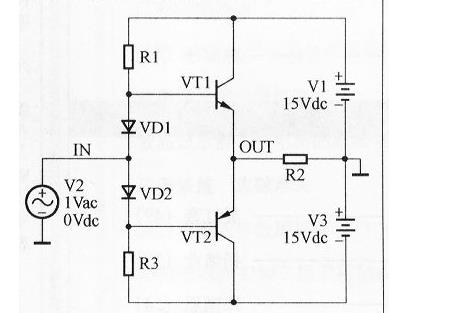

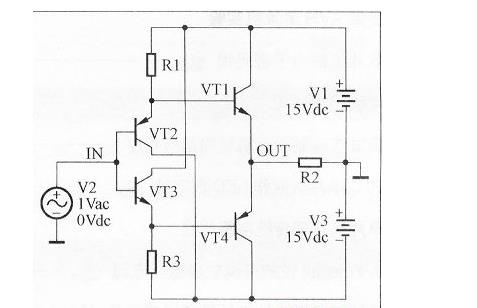

下图是3种菱形缓冲器电路;由4个互补晶体管组成的电流驱动电路,形成的菱形缓冲器(DiamondBuffer)。

最基本的缓冲器(Buffer)电路是图1所示的晶体管发射极跟随器。

这样的发射极跟随器电路输入与输出之间的直流电位相差了一个晶体管发射极PN结正向压降,因此将NPN型晶体管与PNP型晶体管接成单端互补推挽输出型式时,像图2的电路那样,加上VD1、VD2两个二极管作为输出晶体管的偏压,用来抵消晶体管发射极PN结正向压降,这样就可以让输入与输出之间的直流电位相同。图2的电路是以VD1、VD2两个二极管作为输出晶体管的偏压,如果用晶体管发射极PN结取代二极管作为输出晶体管的偏压,形成了图3的电路。由于二极管没有电流放大作用,而晶体管则具有电流放大作用,因此图3的电路比图2的电路输入阻抗更高,成为更理想的缓冲器电路。在图3电路中,由于不同晶体管之间发射圾PN结的正向压降会有相当大的误差;而且容易受温度影响,各个晶体管的工作电流难以把握,所以除了集成电路IC内部的电路之外,实际上用分立元件组成的菱形缓冲器电路是像图4这个样子,在4个晶体管的发射极加上发射极电阻,用来稳定各个晶体管的工作电流,这是最基本的菱形缓冲器电路。电路的工作电流设定为驱动两个晶体管工作的电流约4mA,输出级两个晶体管工作电流约l5mA。将图4基本菱形缓冲器电路中的VT2、VT5改成西克对管(SziklaiPair)就成为图5的电路。西克对管电路又称为互补达林顿电路。双极性晶体管的集电极电流与基极电流的比值称为p值,代表双极性晶体管的电流增益特性。将两个晶体管接成达林顿电路或西克对管电路,可以相当于一个p值超高的晶体管。达林顿电路或西克对管电路的p值约为两个晶体管β值的乘积,如果两个晶体管的β值相等,则达林顿电路或西克对管电路的总β值为两个晶体管各自β值的平方。达林顿电路或西克对管电路的缺点是晶体管的漏电电流也放大β倍,晶体管集电极与发射极间的阻抗减小到原来的1/β。

达林顿电路与西克对管电路比较:达林顿电路将两个双极性晶体管的发射结串联,使得发射结的正向压降加倍;西克对管电路的发射结的正向压降则没有加倍。达林顿电路的前一个晶体管是以晶体管三种基本放大电路中的共集电极方式驱动后一个晶体管,所以达林顿电路本身两个晶体管都是发射极跟随器的形式。西克对管电路的前一个晶体管则是以共发射极方式驱动后一个晶体管,而后一个晶体管又以共发射极方式输出至前一个晶体管的发射极,形成环路负反馈,西克对管电路本身两个晶体管都是共发射极方式。一般认为在晶体管三种基本放大电路方式中,共发射极方式的输出延迟最严重,因此西克对管电路的缺点为输出延迟较严重,高频工作较不稳定,容易发生自激振荡。将圆4基本菱形缓冲器电路中的R1、R9改成高阻抗的恒流源则成为图6的电路,这是最典型的菱形缓冲器电路。图7所示电路为使用结型场效应管驱动双极性晶体管的缓冲器,利用结型场效应管的G极与S极的PN结要反偏,双极性晶体管基极与发射极的PN结则要正偏,组合起来就成为一个既简单又性能优异的缓冲器电路。设计这种电路时必须注意选用的结型场效应管的Vgs(off)要大于输出晶体管发射极结的压降加上发射极电阻的压降,否则结型场效应管还不能驱动双极性晶体管就已经截止了。

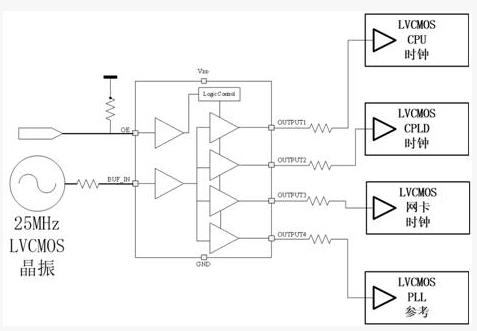

最后再分享几个大普通信的时钟缓冲器(Buffer)的典型应用。

时钟信号复制:

一个晶振加上一个时钟缓冲器(Buffer)芯片,这也是最常用的方案。通过Buffer的频率复制功能,可以做到点到点的拓扑结构,很好的解决信号完整性问题,做到最佳性价比。

晶振和Buffer解决方案

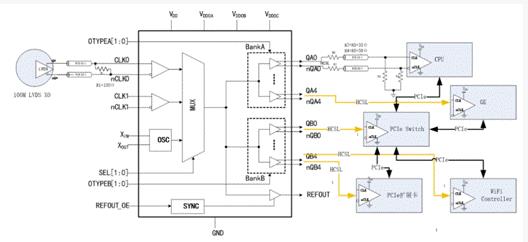

时钟信号格式转换:

在数据中心、服务器、网络监控设备等应用中,很多芯片之间都通过PCIe接口通信,比如CPU、 PCIe交换芯片、PCIe扩展卡、Wifi 控制器、GE口等,都是通过PCIe口来传输高速数据,系统中需要多个HCSL格式的100M的参考时钟,而市场上没有直接出HCSL信号的晶振,这时可以用100M LVDS或LVPECL输出的晶振,通过Buffer转换为100M HCSL时钟信号格式来满足应用。

图7:时钟信号格式转换

-

变频器直流母线电路示意图讲解2023-08-10 3516

-

变频器直流母线电路示意图分析2022-10-27 2569

-

什么是时钟缓冲器(Buffer)?时钟缓冲器(Buffer)参数解析2022-10-18 31180

-

变频器直流母线电路示意图相关资料分享2021-09-06 2508

-

人体检测传感器的管脚,电路示意图详细概述(免费下载)2018-06-01 3446

-

TIpmp3573 revc的电路示意图2018-04-11 1102

-

TIpmp3663 RevBPLC电路示意图2018-04-10 1166

-

什么是buffer2010-02-22 6599

-

宽带缓冲器电路图2009-07-13 1074

-

单位增益缓冲器:The Unity-Gain Buffer2009-05-16 18115

全部0条评论

快来发表一下你的评论吧 !