什么是功能ECO?为什么许多功能ECO解决方案无此效果?

描述

无论身处哪条赛道,为客户提供先进的、具有差异化的产品,是所有芯片设计团队的共同目标。突破先进工艺节点设计的功耗、性能和面积(PPA)极限正是开发者们努力的方向之一。

大多数芯片设计团队在这一环节使用新思科技的数字设计产品系列,即Design Compiler或Fusion Compiler解决方案。团队通常想要利用时序重定、多位寄存器合并、高级数据路径优化等所有可用的复杂功能,来实现更出色的结果质量(QoR)。对客户来说,能够快速建立一个可预测的芯片设计周期可以让他们更早地上市新产品,这将是他们跑赢市场的一个关键性竞争优势。

此外,RTL代码经常发生预期之外的功能性变更,甚至可能到最后一刻都还在变,对这些变更做出及时响应对开发者来说非常重要。此类变更通常使用功能工程变更命令(ECO)来实现,此时的RTL已冻结,且综合与布局布线都已经处于后期阶段。无论是为了修复功能验证漏洞,还是要增加重要新功能,ECO都必不可少。

相比把所有代码从头再跑一遍,ECO所需的时间和成本较少,因此成为首选方案。但ECO往往出现在设计流程后期,而且可能涉及到相当复杂的工作,这意味着ECO可能会对时序逻辑、状态机、时钟复位路径等产生影响。正因如此,开发者们对自动化工具的需求更加明确。

什么是功能ECO?

功能ECO是指将逻辑直接插入与RTL中变更相对应的门级网表的过程。提供此功能的自动化解决方案应该能够比较原有设计和经过ECO修改后设计中的受影响的逻辑锥,识别代表变更的最小逻辑门集合,然后对其生成补丁并确保补丁可在原布局布线网表中轻松应用。

ECO中包含多种实现方式,从在设计中添加或移除逻辑,到清理布线以确保信号完整性等细微变更。所有ECO都侧重于尽可能加快产品上市速度,并最大限度地降低修改和计划风险。处理ECO的工作不仅压力大、时间长,而且还充满不确定性。

考虑到ECO生成过程中的巨大时间压力,务必要做到以下几点:

缩短周转时间:尽快生成准确的补丁

尽量减少迭代:补丁应功能正确且兼顾时序,从而尽可能减少对已实现设计的干扰

为什么许多功能ECO解决方案 无此效果?

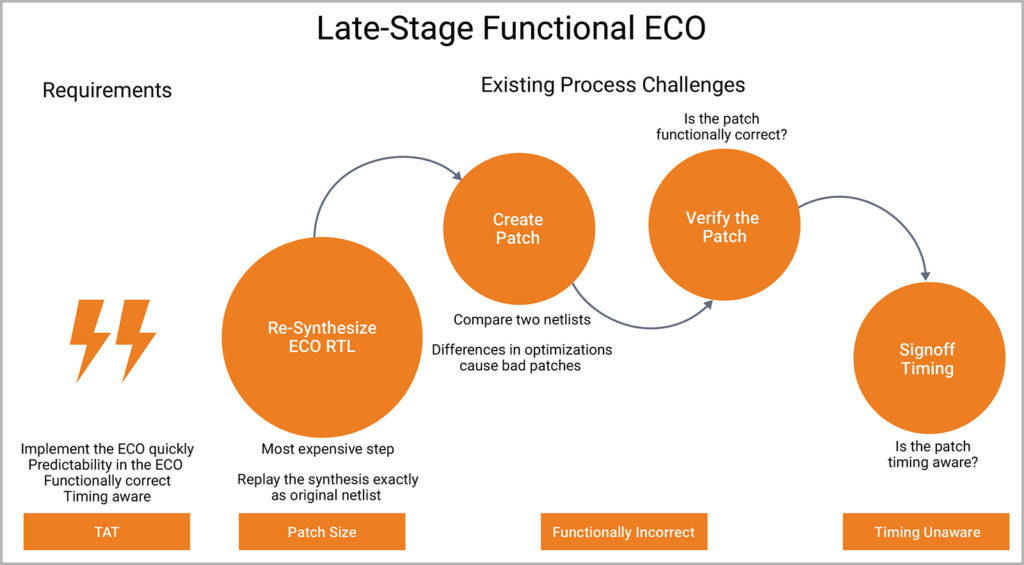

结合上述要求,我们来看一下市场上现有功能ECO解决方案的局限性(图1)。

▲图1:市场上许多现有的功能ECO解决方案都存在局限性,影响质量和周转时间。

第一代功能ECO解决方案受制于基本流程局限性:全部都要遵循网表驱动型流程。这意味着,ECO创建过程只能比较两个完全综合的网表,即原网表与新综合的ECO网表。在使用这些解决方案时,即使ECO实际上只涉及数行RTL代码或几个组合门,用户也需要对经过ECO的分区进行完整重新综合。如果该分区的完整综合需要数天时间,这一步可能成本极高,而由于ECO实现时间非常紧张,设计团队根本等不起。

第二个局限性在于,在ECO综合阶段,这些工具很多都严格要求重现综合优化。换言之,这些解决方案要求ECO网表实现与原网表完全相同的优化。这是因为,在ECO综合期间,ECO中包含的RTL变更可能会提示综合工具选择不同的优化路径。例如,一些寄存器以前可能是常值寄存器,但在ECO之后,变成了非常值寄存器。一些寄存器合并策略可能有所不同,可能导致存在寄存器合并或寄存器复制步骤的不同。

在比较这样两个优化路径不同的网表时,工具可能很难正确识别逻辑锥之间的真正差异,因而无法生成功能正确或最优的补丁。最终,这会给ECO综合步骤带来不必要的限制。此外,因为上述原因,开发者还需要完成大量手动或自定义设置来重现综合,以便ECO工具能够分析这两个网表并创建最小的补丁。

担心在ECO流程后期面临这些复杂因素,开发者通常会减少诸如打平层次、时序逻辑优化和反相驱动等综合优化操作,以便缩短ECO周期。ECO基本上决定了团队如何执行综合,而这种情况是可以避免的。

总的来说,在从ECO RTL就绪到ECO完成的过程中,许多现有的自动化解决方案存在以下局限性:

仅支持网表流程,因此用户必须先执行ECO综合步骤,才能开始创建补丁。而分区综合有时可能需要数天时间,这显著延长了周转时间(TAT)。

引入限制。ECO综合必须与原有综合完全相同,从而尽可能减少两个网表之间的优化差异。另外,重现综合需要完成大量自定义设置,这又进一步延长了周转时间。

上述两个步骤只要出现任何差错,工具生成的补丁就会错误低效,进而需要多次手动迭代来修正补丁。

最后,由于担心面对上述种种复杂因素,开发者会选择禁用综合优化,而牺牲结果质量。

能够一次成功的ECO解决方案

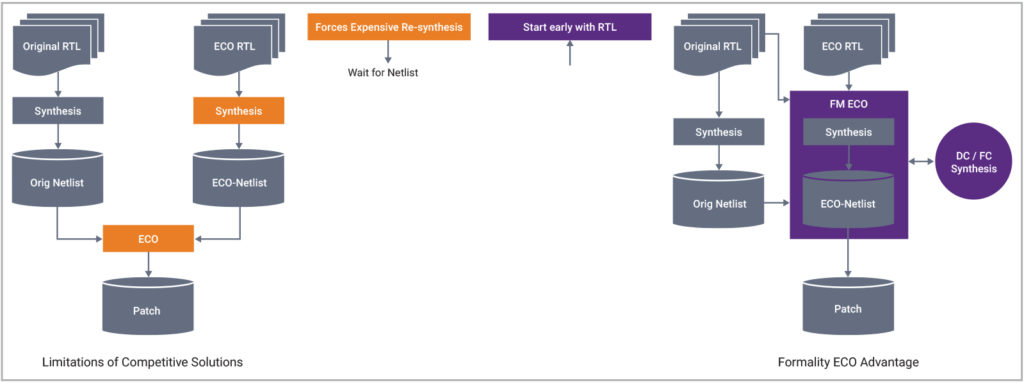

能够一次成功的ECO解决方案在市场上还是存在的,该解决方案用时更短,质量也更好,那就是新思科技Formality ECO解决方案。 新思科技的功能ECO解决方案,Formality ECO会在ECO RTL就绪后,立即开始ECO生成过程。在后期ECO过程中,这为开发者提供了有利的开端,并为他们节省了宝贵的时间(图2)。

▲图2:左图说明了市场上其他功能ECO解决方案的局限性,右图则凸显了新思科技Formality ECO解决方案如何以更优质量、更快周转时间让ECO一次成功。

该解决方案突破性地利用Formality等效性检查技术和Design Compiler或Fusion Compiler解决方案的内部编译技术。

首先,Formality ECO解决方案会比较原RTL和ECO RTL,利用结构分析功能来识别并分隔代表ECO的变更区域。“find_equivalent_net”功能可以越过模块和触发器边界并一直到网络边界进行遍历和局部分析。该方法有助于分隔在ECO RTL中捕捉变更所需的最小ECO区域集合。

然后,这些区域会发送至Design Compiler或Fusion Compiler解决方案,由后者根据指示执行“目标综合”。从本质上来说,这属于具有ECO意识的智能编译,它仅对变更区域进行综合,而无需执行完整的ECO综合。该解决方案会准确识别目标综合,并仅对模块内部受ECO影响的区域进行综合。此外,综合是在整体设计约束下执行的智能编译。该综合支持所有必要的优化,因而不会影响结果质量。这样一来,该ECO生成可确保功能正确。

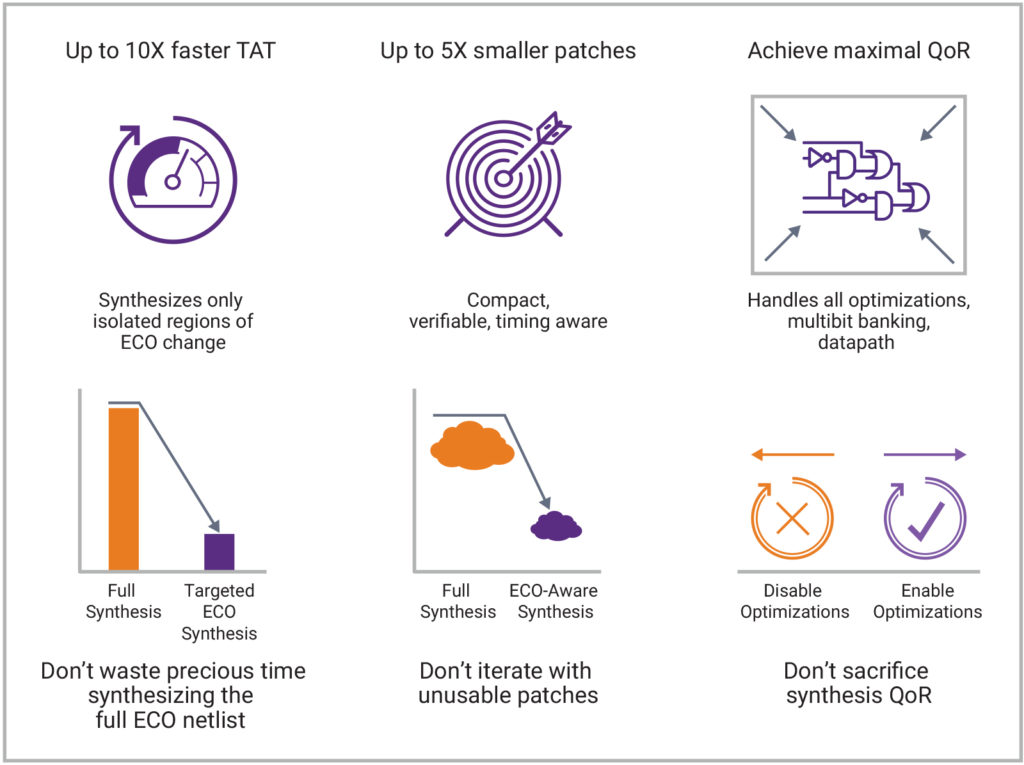

实践表明,Formality ECO技术可将周转时间缩短到原来的十分之一,使补丁最多缩小到原来的五分之一,并能够为广泛应用领域中的设计大幅提高结果质量(图3)。

▲图3:新思科技Formality ECO解决方案具有诸多优势,能够实现更高质量的ECO。

审核编辑:刘清

-

奇捷科技EasyAI ECO Suite即将发布2026-01-15 971

-

分享一种大型SOC设计中功能ECO加速的解决方案2024-03-11 1353

-

时序(Timing)对功能ECO有多重要2023-07-05 2875

-

解析什么是DFT友好的功能ECO?2023-05-05 3190

-

什么是ECO?ECO的应用场景和实现流程2023-04-23 8567

-

什么是DFT友好的功能ECO呢?2023-03-06 3795

-

新思科技推出突破性ECO解决方案PrimeClosure,助力设计效率提升10倍2022-10-14 847

-

详解Xilinx FPGA的ECO功能2022-08-02 5402

-

空调遥控器上的eco是什么意思2022-04-18 11358

-

一场关于自动化ECO解决方案的在线研讨会2022-04-12 1820

-

多功能步进电机驱动器为许多应用提供了经济高效的解决方案2019-06-27 3459

-

如何在Vivado中执行工程变更命令 (ECO)2018-11-21 5913

-

V6 FPGA可以ECO功能吗?2018-11-13 1970

-

汽车eco模式使用技巧_eco模式真能省油吗2017-12-14 30264

全部0条评论

快来发表一下你的评论吧 !