单片机的基本结构与工作原理

控制/MCU

描述

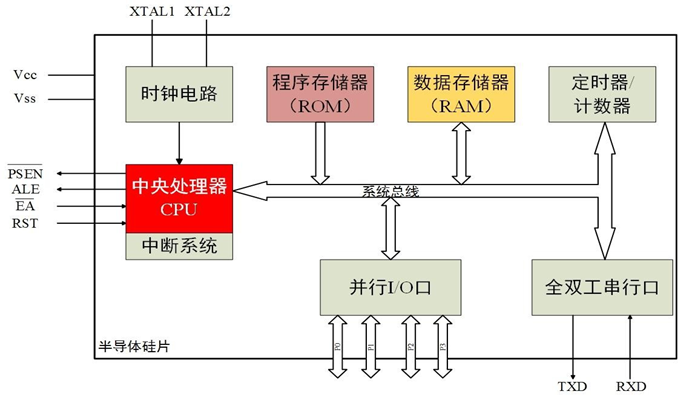

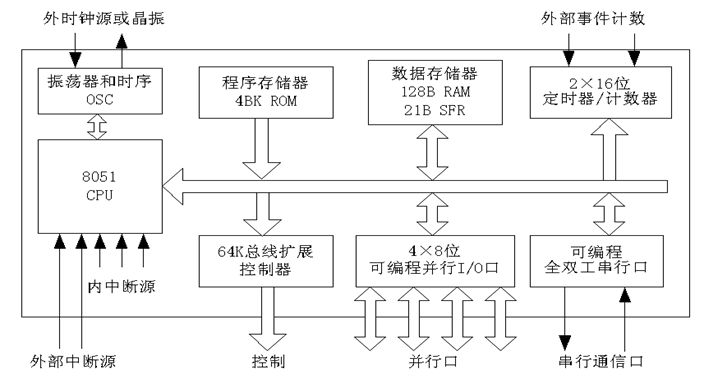

单片机的基本结构包括中央处理器(CPU) 、存储器、定时/计数器、输入输出接口、中断控制系统和时钟电路六部分。

一、基本组成

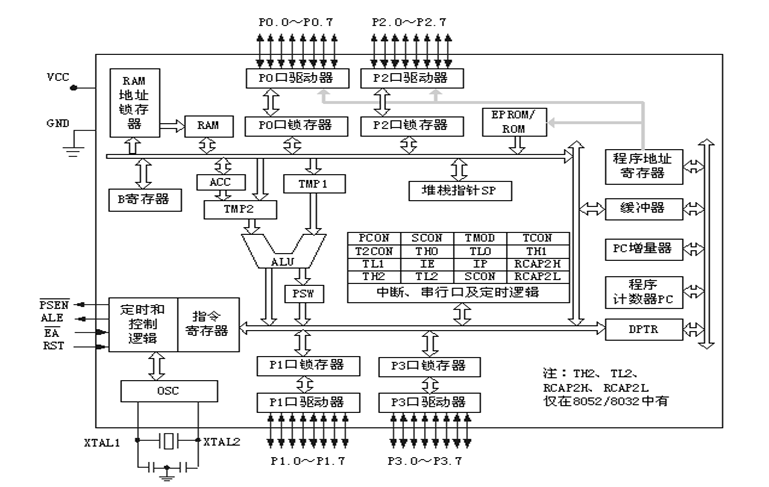

中央处理器(CPU)

包括运算器和控制器两部分,是单片机的核心。运算器可用于各种运算,控制器用于控制单片机各部分协调工作。

存储器

用于存放程序和原始数据。

时钟电路

时钟电路产生单片机运行的控制信号,控制单片机严格按时序执行指令。

定时/计数器:实现定时或计数功能。

输入输出接口(I/O)实现单片与其他设备之间的数据传送。

中断控制系统: 用于响应中断源的中断请求;

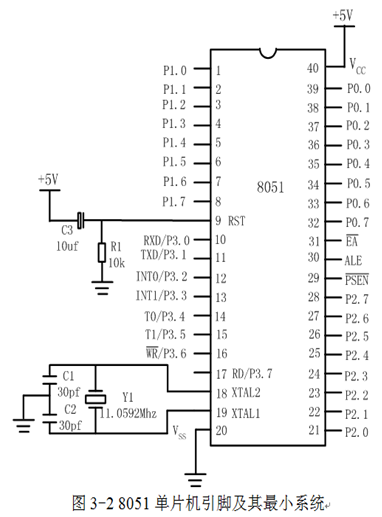

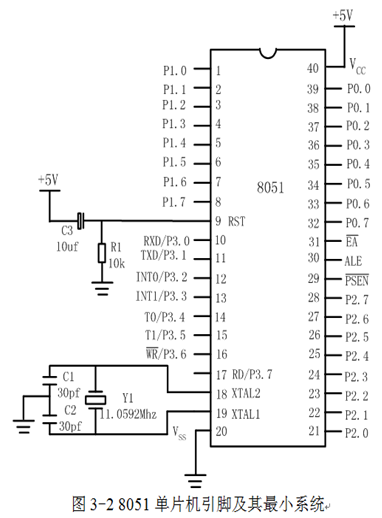

二、单片机引脚

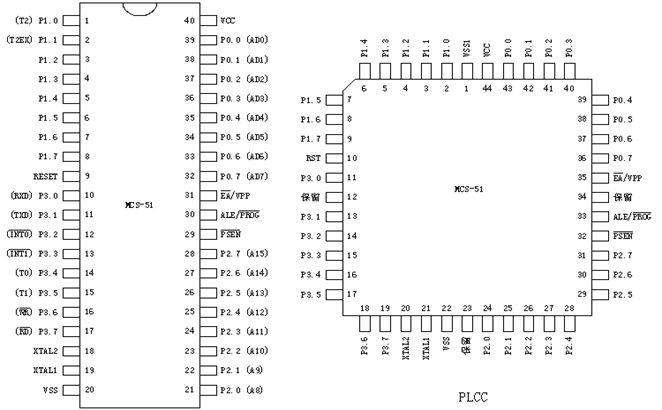

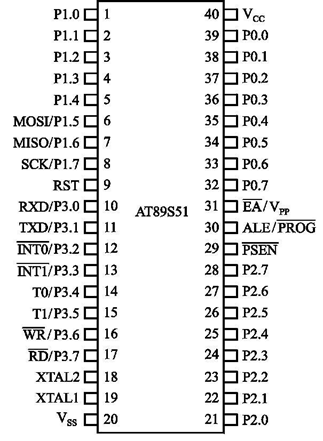

双列直插式封装(DIP,Dual Inline Package)

方形封装(PLCC,Plastic Leaded Chip Carrier)

电源引脚: VCC (40脚)和VSS(20脚)分别接供电电源正极和负极。

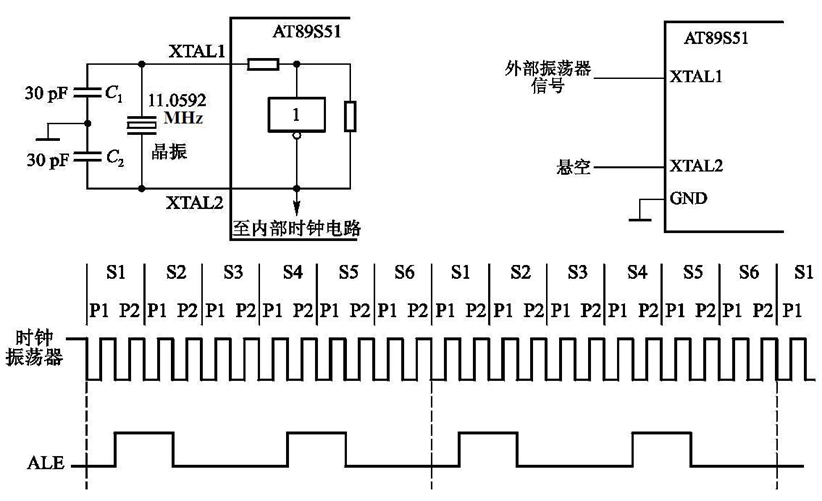

时钟电路引脚:单片机需要有时钟脉冲信号才能工作,经(18脚)和 (19脚)接振荡电路。

控制信号引脚包括以下4个:

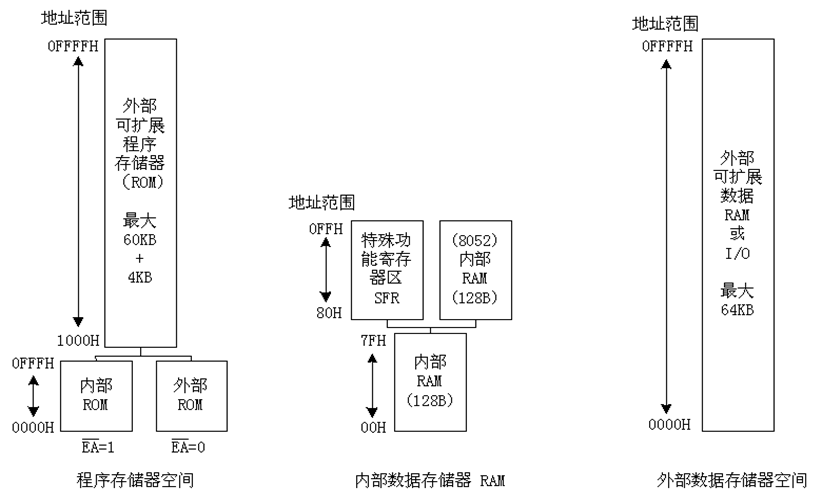

EA( 31脚):当EA接高电平时先内后外执行ROM程序。接低电平时只执行外部ROM程序。

RST (9脚):当输入两个机器周期以上的高电平时实现复位,使单片机初始化并重新执行程序。

ALE (30脚):访问外部存储器和其他外设时,ALE控制低8位地址和数据的分时传送。

PSEN (29脚):外部程序存储器读选通信号。

并行输入/输出引脚共32个:

PO口(39-32脚):可作地址/数据总线端口用,也可作普通I/O口用。

P1口(1-8脚):一般只用作I/O端口。

P2口(21-28脚):当访问外部存储器时可输出高8位地址,也可作普通I/O端口使用。

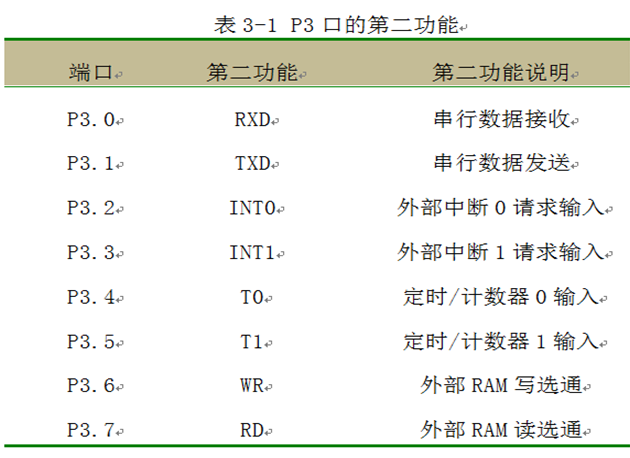

P3口(10-17脚):主要用其第二功能,也可作普通I/O口用。

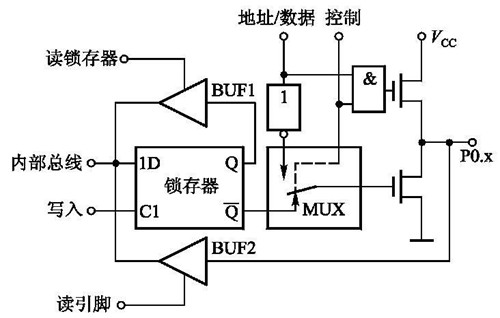

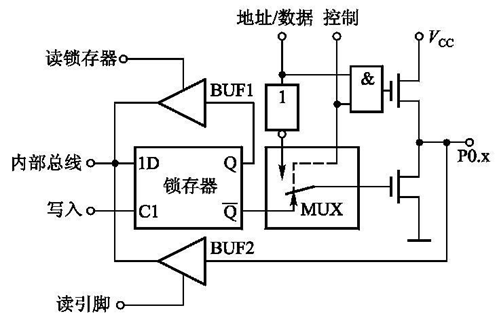

三、并行输入/输出

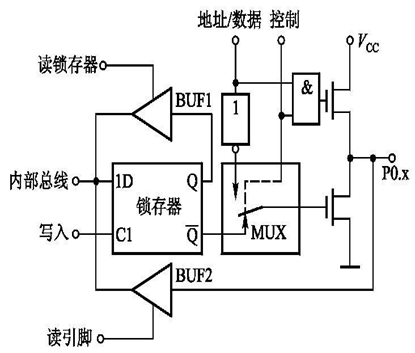

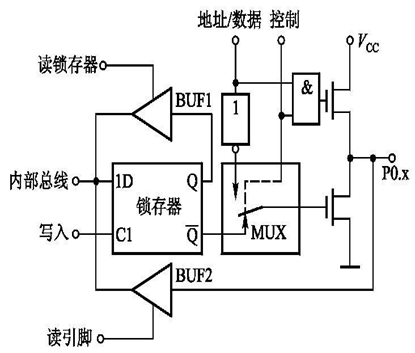

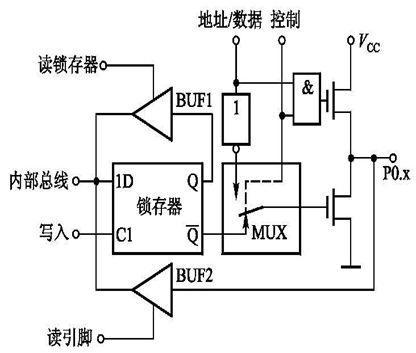

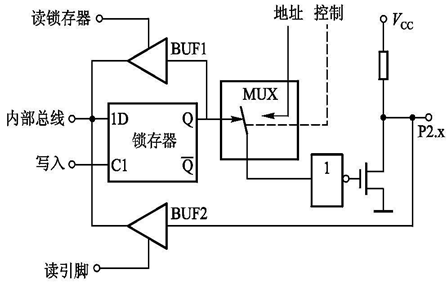

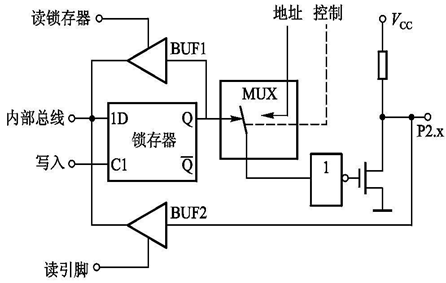

P0口位电路结构

1个数据输出锁存器。

2个三态的数据输入缓冲器BUF1和BUF2。

2个场效应管(FET)。

多路开关、反相器、与门各1个。

P0口工作原理——用作复用的地址/数据总线

输出:“控制”信号为1,硬件自动使转接开关MUX打向上面,接通反相器的输出,同时使“与门”开启。

①当输出的地址/数据信息=1,“与门”输出为1,上方场效应管导通,下方场效应管截止,P0.x引脚输出为1。

②当输出的地址/数据信息=0,上方场效应管截止,下方场效应管导通,P0.x引脚输出为0。

P0口工作原理——用作复用的地址/数据总线

输入:当P0口作为数据输入时,仅从外部引脚读入信息,“控制”信号为0,MUX接通锁存器Q端。

P0口作为地址/数据复用方式访问外部存储器时,CPU自动向P0口写入FFH,使下方场效应管截止,上方场效应管由于控制信号为0也截止,从而保证数据信息的高阻抗输入,从外部输入的数据直接由P0.x引脚通过输入缓冲器BUF2进入内部总线。

①当D锁存器为1时, 端为0,下方场效应管截止,输出为漏极开路,此时,必须外接上拉电阻才能有高电平输出;

②当D锁存器为0时,下方场效应管导通,P0口输出为低电平。

P0口工作原理——用作通用I/O口

输入:两种读入方式:“读锁存器”和“读引脚”。

①当CPU发出“读锁存器”指令时,锁存器的状态由Q端经上方的三态缓冲器BUF1进入内部总线。

②当CPU发出“读引脚”指令时,锁存器的输出状态Q=1(Q端为0),而使下方场效应管截止,引脚的状态经下方的三态缓冲器BUF2进入内部总线。

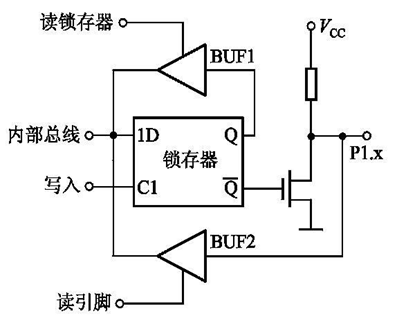

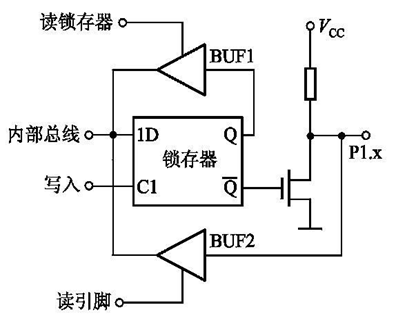

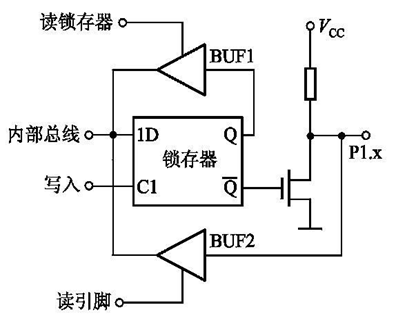

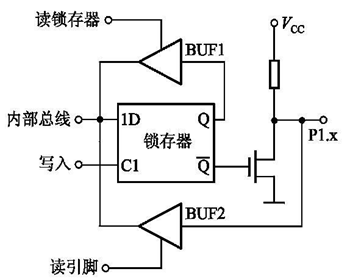

P1口位电路结构

1个数据输出锁存器。

2个三态的数据输入缓冲器BUF1和BUF2。

1个场效应管(FET)和1个片内上拉电阻组成。

P1口工作原理——只用作通用I/O口

①若CPU输出1,Q=1,Q-=0,场效应管截止,P1.x脚输出为1;

②若CPU输出0,Q=0,Q- =1,场效应管导通,P1.x脚输出为0。

P1口工作原理——只用作通用I/O口

输入:分为“读锁存器”和“读引脚”

①读“锁存器”,输出Q状态经输入缓冲器BUF1进入内部总线;

②“读引脚”,先向锁存器写1,使场效应管截止,P1.x引脚上的电平经输入缓冲器BUF2进入内部总线。

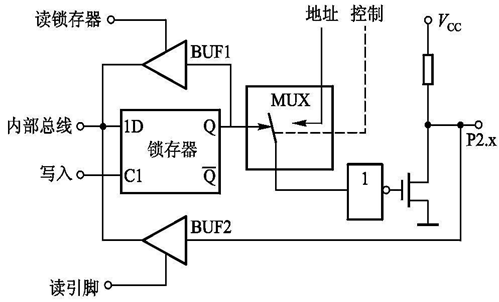

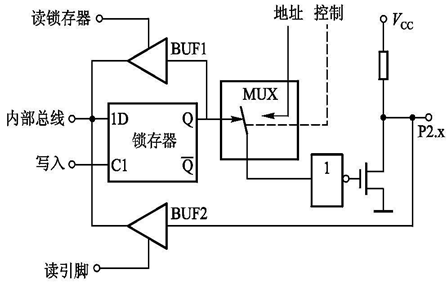

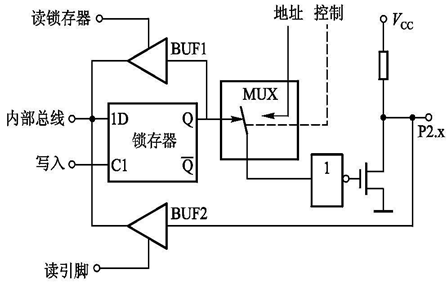

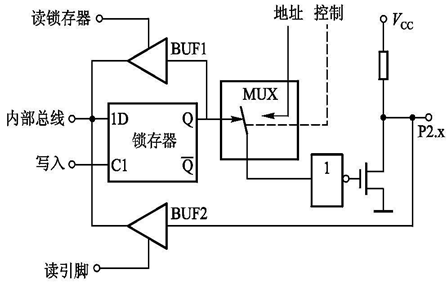

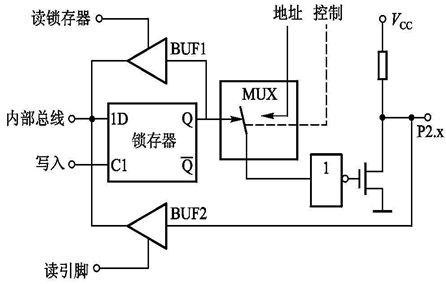

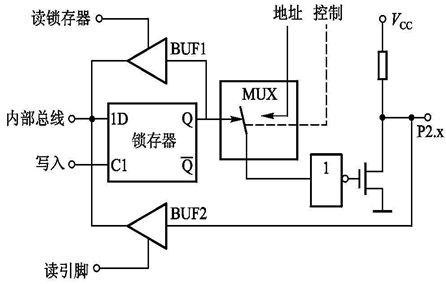

P2口位电路结构

1个数据输出锁存器。

2个三态的数据输入缓冲器BUF1和BUF2。

1个场效应管(FET)和1个片内上拉电阻组成。

1个多路转接开关MUX

P2口工作原理——用作地址总线

在控制信号作用下,MUX与“地址”接通。

①当“地址”为0时,场效应管导通,P2口引脚输出0;

②当“地址”线为1时,场效应管截止,P2口引脚输出1。

P2口工作原理——用作通用I/O口

输出:在内部控制信号作用下,MUX与锁存器Q端接通。

①CPU输出1时,Q=1,场效应管截止,P2.x引脚输出1;

②CPU输出0时,Q=0,场效应管导通,P2.x引脚输出0。

P2口工作原理——用作通用I/O口

输入:分“读锁存器”和“读引脚”两种方式。

①“读锁存器”时,Q端信号经输入缓冲器BUF1进入内部总线;

②“读引脚”时,先向锁存器写1,使场效应管截止,P2.x引脚上的电平经输入缓冲器BUF2进入内部总线。

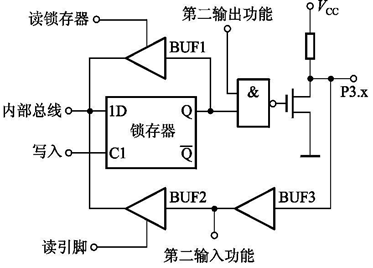

P3口位电路结构

1个数据输出锁存器。

3个三态的数据输入缓冲器BUF1和BUF2。

1个场效应管(FET)和1个片内上拉电阻组成。

1个多路转接开关MUX和1个与非门

P3口工作原理——用作第二功能

输出:该位的锁存器需要置“1”,使“与非门”为开启状态。

当第二输出为1时,场效应管截止,P3.x引脚输出为1;

当第二输出为0时,场效应管导通,P3.x引脚输出为0。

P3口工作原理——用作第二功能

输入:该位的锁存器和第二输出功能端均应置1,保证场效应管截止,P3.x引脚的信息由输入缓冲器BUF3的输出获得。

P3口工作原理——用作通用I/O口

输出:第二输出功能端应保持“1”,“与非门”开启。

CPU输出1时,Q=1,场效应管截止,P3.x引脚输出为1;

CPU输出0时,Q=0,场效应管导通,P3.x引脚输出为0。

P3口工作原理——用作通用I/O口

输入:P3.x位的输出锁存器和第二输出功能均应置1,场效应管截止。

P3.x引脚信息通过输入BUF3和BUF2进入内部总线,完成“读引脚”操作;

也可执行“读锁存器”操作,此时Q端信息经过缓冲器BUF1进入内部总线。

四个并口(P0-P3)在读引脚之前,都需要将锁存器置“1”,使场效应管截止,避免锁存器内数据的干扰。

由于在输入操作前还必须附加一个置“1”的准备动作,因此称为“准双向口”。

四个并口(P0-P3)都是准双向口

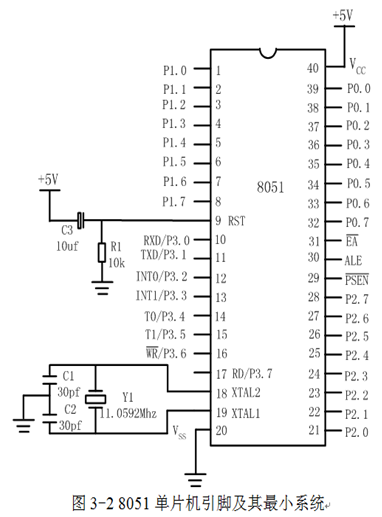

四、8051单片机的最小系统板

8051单片机内部有4KB闪烁存储器,本身就是一个数字量输入/输出的最小应用系统。

在构建8051单片机最小应用系统时,8051单片机需要外接时钟电路和复位电路即可,如下图所示。

注意:本最小应用系统只能作为小型的数字量的测控单元。

审核编辑:汤梓红

-

嵌入式单片机开发学习路径2026-02-09 1001

-

单片机原理及应用2025-06-16 416

-

51单片机CPU的内部结构及工作原理是什么2021-11-18 3223

-

STC51从入门到精通(汇编)~~~ 第三讲:MCS-51单片机的结构和工作原理2021-11-11 845

-

单片机结构及工作原理2021-11-10 710

-

采用软件模拟SPI总线实现双单片机数据通信模块的设计2020-02-04 3894

-

MCS-51单片机的硬件结构与工作原理2017-06-21 2263

-

MS-51系列单片机结构及工作原理大全2017-01-02 14263

-

51单片机端口的结构及工作原理2016-08-29 1266

-

【AVR单片机学习入门之前】 如何快速高效学习AVR单片机2011-12-07 8168

-

单片机系统的工作原理设计2010-04-14 620

全部0条评论

快来发表一下你的评论吧 !