不改平面不加层,微调走线抬电平

不改平面不加层,微调走线抬电平

电子说

描述

设计组有个小伙子叫小博,入职刚满一年,今天收到了公司发来的暖心邮件。

他却高兴不起来,因为昨晚收到了一封电源仿真结果的邮件:自己独立接手的第一个设计任务,到了投板的节骨眼,直流压降有问题。

正可谓:

曾因压降夜难寐,犹为阻抗困愁城。

世间无限丹青手,一片忧心画不成。

小博一夜难眠,一大早就来求助高速先生。

看着小博急切又期待的眼神,高速先生认真查了下板,最后给出的建议是,问题不大,不改平面不加层,动动走线就能行。小博半信半疑……

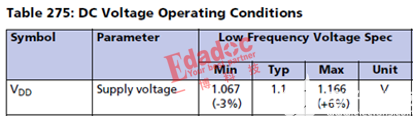

电源的直流压降,作为衡量电源性能的一个重要指标,用电芯片端的要求通常会以电压百分比的方式给出,例如下表的DDR5的VDD,直流压降要求为-3%~+6%

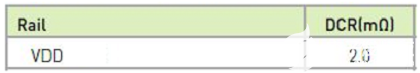

不过,越来越多的芯片手册直接对电源路径的直流电阻提出要求,以DCR(Direct Current Resistance)阻值的形式给出。

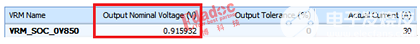

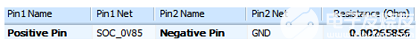

再来看看小博遇到的这个电源,电源电压0.85V,用电芯片端的压降要求:-1%~-+1%.

原设计文件的仿真结果如下:VRM输出916mV,到达用电芯片的电压为833mV,不满足压降要求。

此时,电源DCR为2.66mΩ。

按照高速先生的建议,微调走线后,用电芯片的电压增加至846mV。

结果竟然达标了!小博惊掉了下巴,这……

电源DCR却保持不变,仍然是2.66mΩ

修改前后的电源通道完全没有变化,电源DCR均为2.66mΩ,可是用电芯片端的电压怎么就神奇的抬起来了呢?玄机就在电源输出的变化。

修改前,VRM输出916 mV。

修改后,VRM输出增加至929mV。

VRM输出电平抬高,电源路径压降不变,用电芯片端的电压可不就水涨船高嘛。

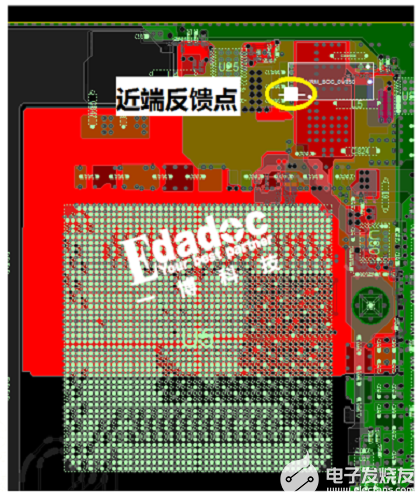

有经验的Layout攻城狮应该已经猜到了小博的问题出在哪了。

没错,由于经验不足,小博原设计的电压反馈点设置在了近端,太靠近VRM。

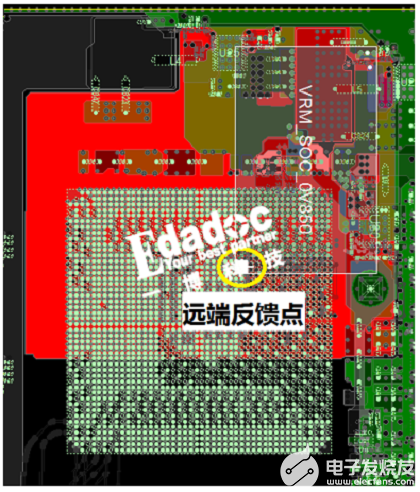

为了抬高VRM的输出电平,高速先生建议将反馈点调整至远端,修改后的版本如下,靠近了用电芯片:

仅通过调整VRM的电压反馈走线,不涉及电源平面和层叠的修改,就能让用电芯片的电压满足要求,简直是懒人福音,不过,前提是VRM有电压反馈的功能,而且,电压输出调整幅度也有一定的范围,不能任性。

与电压百分比的方式相比,有些芯片手册对电源DCR提出要求也有它的道理,它可以更加直接的反映电源通道本身的参数。作为电源通道的重要组成部分,电源平面可以视为方块电阻,而方块电阻的阻值与面积和厚度有关,因此,DCR的大小也与铜皮的有效面积和厚度有关系。

这里可以再做个仿真对比,说明DCR的变化对电源的影响。还是使用上面的仿真文件,为了简化问题,删除了电压反馈线,VRM输出电压将保持为0.85V,对比不同铜厚带来的变化。按照当前的电源平面和层叠设置,直流压降仿真结果如下:

因为通道没有变化,电源路径直流压降仍然是83mV,电源DCR也保持不变,2.66mΩ。

我们把电源平面的铜厚由1oz增加到2oz,其它不变,再来看看仿真结果:

由于电源平面的铜厚增加,电源DCR由2.66mΩ减小到2.48mΩ,直流压降也从83mV降低至76mV。由此可见,电源通道本身的优化确实可以减小DCR,进而改善压降。

经验丰富的攻城狮都知道,在单板设计后期改动电源通道耗时费力,因此根据压降和通流要求提前规划电源就显得格外重要。当然了,走弯路也是学习的一种方式,虽然效率不是最高的,但是,一定是记忆最深刻的,小博应该深有感触。

审核编辑:汤梓红

-

第二层是地平面 ,top层跨平面走,该信号走在第三层?2015-02-10 0

-

关于四层板差分的参考层是电源平面的问题2019-08-06 0

-

什么是弱电平面?CAD中弱电平面有哪些功能?2021-04-02 0

-

allegro的电源层平面分割2021-12-27 0

-

不改平面不加层,微调走线抬电平2022-10-20 0

-

内层的电源平面、地平面如何设计?2022-12-08 0

-

单圈微调线绕电位器2009-08-21 978

-

多圈微调线绕电位器2009-08-21 1591

-

PCB走线的参考平面怎么判断2018-03-08 10053

-

PCB走线的参考平面在哪2019-08-20 6880

-

cadence allegro电源层平面分割2022-01-05 1458

-

PCB走线的参考平面2022-09-09 4666

-

是否可以把电源平面上面的信号线使用微带线模型计算特性阻抗?2023-11-24 502

全部0条评论

快来发表一下你的评论吧 !