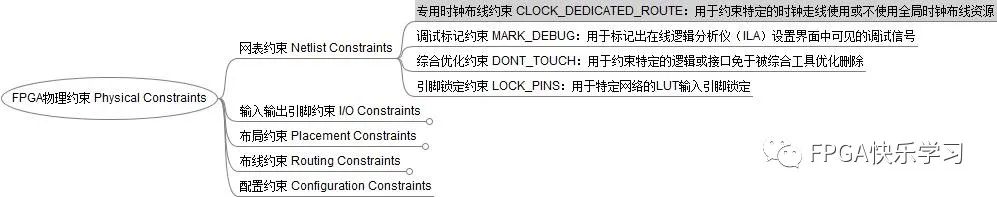

FPGA物理约束-网表约束CLOCK_DEDICATED_ROUTE

接口/时钟/PLL

49人已加入

描述

概述

Vivado工具在编译时通常会自动识别设计中的时钟网络,并将其分配到专用的时钟布局布线资源中。通过对某些时钟网络设置CLOCK_DEDICATED_ROUTE值为FALSE,可以将被识别为时钟网络并按照时钟网络进行布局布线的时钟信号安排到通用的布线资源中。比如,某些时钟信号由于设计疏忽或其它原因,没有被安排到FPGA器件的时钟专用引脚上,在编译的时候就会报错,此时就可以使用CLOCK_DEDICATED_ROUTE约束来忽略这个错误。

工程实践

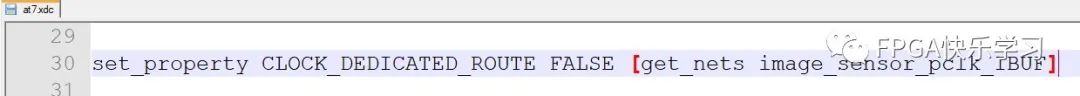

笔者曾经有一个设计,输入到FPGA的图像数据同步时钟image_sensor_pclk信号,由于没有分配到FPGA内部的MRCC或SRCC引脚上(这是一个无意为之的错误设计,请勿模仿),在编译时,Vivado通常可能会报错。

此时,笔者就是通过在工程的.xdc约束文件中添加如下CLOCK_DEDICATED_ROUTE命令,来忽略这个报错,让编译继续进行。

当然,这个约束通常不建议乱用,被施加了CLOCK_DEDICATED_ROUTE FALSE的时钟网络,它将被分配到通用布局布线资源中,若这是一个时序关键路径上时钟,这样的行为很可能会带来一些不期望的设计问题。

审核编辑:彭静

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Xilinx FPGA管脚物理约束介绍2022-07-25 6179

-

FPGA时序约束之衍生时钟约束和时钟分组约束2023-06-12 4511

-

FPGA物理约束之布线约束2023-12-16 2474

-

怎么生成一个时钟来驱动FPGA逻辑和使用DCM的OPAD2019-07-03 10782

-

在Spartan 6 - LX9上测试FPGA-Design错误问题2019-07-15 2830

-

我的verilog代码和约束文件出错该怎么办?2019-08-01 2646

-

似乎没有检测到“CLOCK_DEDICATED_ROUTE = FALSE”约束是怎么回事2020-06-16 6905

-

CLOCK_DEDICATED_ROUTE约束应用2020-09-15 4721

-

关于 DDR时序约束常见的ERROR问题2020-09-21 5138

-

赛灵思(Xilinx)FPGA用户约束文件的分类和语法说明2017-02-11 2102

-

XDC约束及物理约束的介绍2019-01-07 7415

-

简述Xilinx FPGA管脚物理约束解析2021-04-27 6484

-

物理约束实践:网表约束LOCK_PINS2022-11-28 2445

-

Xilinx FPGA的约束设置基础2024-04-26 2676

全部0条评论

快来发表一下你的评论吧 !