组合逻辑电路的FPGA设计

可编程逻辑

描述

第5章 从组合逻辑电路学起

组合逻辑电路的特点是输入的变化直接反映了输出的变化,其输出的状态仅取决于输入的当前状态,与输入、输出的原始状态无关。如果从电路结构上来讲,组合逻辑电路是没有触发器组件的电路。组合逻辑电路的输入输出关系比较简单,在“数字电路技术”课程中也首先讨论的是组合逻辑电路。由于数字电路只有0、1两种状态,基本的逻辑门电路为与、或、非等,输入输出关系很容易理解。正因为如此,不少同学初次接触到数字电路技术时,都感觉理解起来毫不困难。本章讨论组合逻辑电路的FPGA设计,开始逐渐体验Verilog HDL设计的魅力。

5.1 从最简单的与非门电路开始

5.1.1 调用门级结构描述与非门

实例5-1:与非门电路设计

采用云源软件提供的硬件原语(Primitives)实现与非门电路设计。 打开云源软件,新建FPGA工程E5_1_nand,新建“Verilog File”类型的资源文件 E5_1_nand.v,在空白文件编辑区中编写Verilog HDL代码,实现与非门电路功能,与非门电路代码如下所示。 module E5_1_nand( //第1行:模块名为E5_1_nand input a, //第2行:定义1bit位宽的输入信号a input b, //第3行:定义1bit位宽的输入信号b output dout //第4行:定义1bit位宽的输出信号dout ); //第5行: nand u1(dout,a,b); //第6行:调用与非门结构模块“nand” endmodule //第7行: 完成代码编辑后,保存文件。双击云源软件主界面工具栏中的“Run Synthesis”工具图标完成代码综合。单击工具栏中的“Schematic Viewer”工具图标,查看程序综合后的RTL(Register Transfer Level,寄存器传输级)原理图,如图5-1所示。

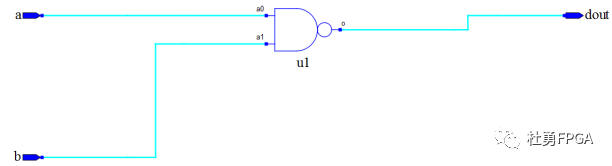

图5-1 与非门的RTL原理图

对照RTL原理图来理解Verilog HDL代码,对于初学者来讲往往可以起到事半功倍的效果。与非门电路模块E5_1_nand描述的电路有2个输入信号“a、b”且均为1比特位宽,以及1个1比特位宽的输出信号“dout”。信号a、b为与非门的输入,dout为a、b信号的与非门输出。实现与非门功能的代码为第6行:nand u1 (dout,a,b)。这行代码的功能是调用了FPGA中的与非门电路模块nand,“u1”是nand模块在E5_1_nand这个文件中的名称,是由用户设定的名称。nand模块有3个接口,第1个接口为输出信号,第2、3个接口为输入信号。程序中第1个接口信号设置为dout时,表示名为u1的与非门的输出与dout信号相连;第2、3个接口信号设置为a、b时,表示名为u1的与非门的输入分别与a、b信号相连。

除与非门外,其它几个常用的门电路分别为:与门(and)、或非门(nor)、或门(or)、异或门(xor)、异或非门(xnor)、非门(not)。在调用门电路时,所有电路的第1个信号均为输出信号,其后的信号为输入信号。

一些著作中将“信号”称为“变量”、“数据”,由于Verilog HD描述的是硬件电路,而在电路中的端口或内部连线实际上都是某种形式的信号,因此本书统一称为“信号”。

5.1.2 二合一的命名原则

在继续讨论组合逻辑电路的代码设计之前,先讨论一下FPGA软件对Verilog HDL的文件及模块名命名规则。对于绝大多数程序设计来讲,对于程序名称、文件名称、模块名称、变量名称,一般要求名称由英文字符、数字、下划线组成,且不能由数字打头,尤其命名时注意不要使用中文字符、空格字符。

在FPGA程序设计中,不同开发环境对Verilog HDL文件名和文件中的模块(module)名命名规则稍有差异。如采用Intel公司的Quartus II 软件设计Verilog HDL程序时,要求文件名和文件中的模块名要保持一致。对于云源软件来讲,Verilog HDL文件名与模块名可以不一致,虽然如此,仍强烈建议遵循Verilog HDL文件名和文件中的模块名保持一致的原则,以利于程序的阅读、维护,和不同开发环境中的代码移植。

对于前文设计的与非门电路来讲,Verilog HDL文件名为E5_1_nand.v,文件中的模块名为E5_1_nand。

5.1.3 用门级电路搭建一个投票电路

实例5-2:3人投票电路设计

利用门电路组件,完成3个评委的投票电路设计。

门电路只是基本的组件,FPGA设计的过程是使用这些组件实现一些具体的电路功能。比如要实现一个简单的三人投票电路,即有3名评委投票,当有2个或3个评委投赞成票后,则表示通过,否则表示不通过。评委只能投赞成票及不赞成票2种,结果只有通过及不通过2种状态。

将评委投票电路用电路来实现,设置评委信号名称分别为key1、key2、key3,当信号为“1”(高电平)时表示赞成,为“0”(低电平)表示不赞成。输出信号为led,为“1”(高电平)时表示通过,为“0”(低电平)时表示不通过。

如果采用CGD100电路板来模拟投票过程,可将3个按键信号分别做为3个评委的投票输入信号,按下时表示投赞成票,不按下时表示投不赞成票。led作为投票结果的输出信号,通过时LED灯点亮,否则不点亮。

根据评委投票规则,得到输入输出信号的逻辑表达式为:

led=(key1 key2)+(key1 key3 )+(key2 key3)

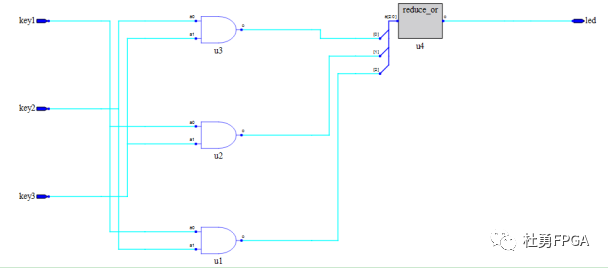

因此,完成投票电路需要使用3个双输入与门电路和1个3输入或门电路。为便于理解,先给出投票电路的RTL原理图,如图5-2所示。

图5-2 投票电路的RTL原理图

新建FPGA工程E5_2_vote,并在工程中新建“Verilog File”类型的资源文件E5_2_vote.v,在文件中编辑如下代码,实现投票电路。

根据图5-2所示的电路结构,程序需要调用3个与门(and)和一个3输入或门(or)。设置3个与门的输出信号分别为d1、d2、d3,程序代码如下所示。

module E5_2_vote( input key1,key2,key3, //第2行 output led ); wire d1,d2,d3; //第5行 and u1(d1,key1,key2); //第6行 and u2(d2,key1,key3); //第7行 and u3(d3,key2,key3); //第8行 or u4(led ,d1,d2,d3);//第9行 endmodule

代码中,第2行定义模块的输入端口时,将3个均为1比特位宽的输入信号 key1、key2、key3写在了一行,且信号之间用逗号“,”隔开。当端口的位宽和类型(输入或输出)相同时,可以采用这种简化写法。

第5行声明了3个wire类型的变量d1、d2、d3。“wire”表示线网类型,是Verilog HDL中最常用的2种信号类型之一,另一种类型为“reg”类型,后面我们再讨论两种类型的区别。Verilog HDL中的信号均有类型,一般为“wire”和“reg”中的一种。vote模块端口中的输入输出信号均为wire类型,当程序中不对信号采用“wire、reg”关键词进行声明时,默认为“wire”类型。

第6~8行依次调用了3个与门(and)电路,且在E5_2_vote.v文件中取名为u1、u2、u3。与门电路的第一个信号为输出,第2、3个为输入信号。因此,对于u1来讲,描述的是key1与key2的与门电路;对于u2来讲,描述的是key1与key3的与门电路;对于u3来讲,描述的是key2与key3的与门电路。第9行描述的是3输入的或门(or)电路,输出信号为led,输入信号为3个与门电路的输出。

对照图5-2,很容易理解E5_2_vote.v的程序代码编写方法。需要说明的是,虽然Verilog HDL中“wire”类型的信号可以不进行声明即使用(后续讨论“reg”类型信号时会说明,“reg”类型信号必须先声明后才能使用),仍强烈建议程序中的所有信号均先进行声明后再进行赋值等其它操作。程序中的端口信号说明相当于对信号的声明。

编辑:黄飞

-

组合逻辑电路之与或逻辑2024-02-04 3724

-

为什么FPGA可以用来实现组合逻辑电路和时序逻辑电路呢?2023-04-23 2983

-

组合逻辑电路和时序逻辑电路的区别和联系2023-03-14 9265

-

组合逻辑电路的分析和设计2023-03-06 6348

-

什么是组合逻辑电路 如何使用verilog描述组合逻辑电路2020-08-08 6617

-

什么是组合逻辑电路_组合逻辑的分类2019-06-22 51333

-

组合逻辑电路实验原理2018-01-30 67925

-

什么是组合逻辑电路,组合逻辑电路的基本特点和种类详解2017-05-22 77190

-

组合逻辑电路电子教案2009-09-01 811

-

组合逻辑电路的分析与设计-逻辑代数2009-04-07 4109

-

基本组合逻辑电路2008-09-24 2961

全部0条评论

快来发表一下你的评论吧 !