PTPX功耗分析之Average Power Analysis

电子说

描述

PTPX,是基于PT,对全芯片进行power静态和动态功耗分析的工具。包括门级的平均功耗和峰值功耗。可以说PTPX就是PT工具的一个附加工具。

PT如果report_power需要额外的PTPX的licence,可以通过以下变量打开:

set_app_var power_enable_analysis true (默认是false)

PrimeTime PX支持两种功耗分析模式:averaged mode和time-based mode。

Average Power Analysis

用PTPX做平均功耗分析,利用后仿产生的VCD/SAIF文件,通过read_vcd/read_saif将真实的翻转率反标到上,然后通过report_switching_activity检查反标率,最后report_power报告功耗值。

平均功耗,是基于翻转率toggle rate来分析的。翻转率的标注,可以是默认翻转率、用户定义switching activity、SAIF文件或者VCD文件。功耗结果期望准确的话,首先要保证翻转率的标注要准确。这意味着需要后端布局布线、时钟树等已经完全稳定了。

前期做功耗分析,可能只是一个评估作用。

工具支持基于仿真的switching activity文件类型,包括:

VCD

FSDB

VPD

SAIF

波形转saif命令

vcd2saif: vcd2saif -i dump.vcd -o vcd2saif.saif fsdb2saif: fsdb2saif dump.fsdb -o fsdb2saif.saif

如果没有上述文件,那可以使用user-define switching activity commands,来提供一个现实的activity去精确power结果。

所需基本文件:

logic库文件,必须是.db格式;

网表文件,支持verilog、vhdl网表,db、ddc、Milkyway格式的网表;

sdc文件,计算平均功耗;

spef文件,寄生参数信息。

VCD/saif文件,记录翻转率(若没有,则需要人为设置翻转率)。

基本流程

Step1: 设置功耗分析模式

set power_enable_analysis TRUE set power_analysis_mode averaged

Step2: read设计,对网表工艺库link

set search_path "../src/hdl/gate ../src/lib/snps . " set link_library " * core_typ.db" read_verilog mac.vg current_design mac link

Step3: 读sdc,反标寄生参数

sdc指定了设计的驱动单元,用以计算输入的transitiontime。

寄生参数是影响动态功耗的因素之一,反标寄生参数文件能够提高功耗分析的准确性。

read_sdc ../src/hdl/gate/mac.sdc set_disable_timing [get_lib_pins ssc_core_typ/*/G] read_parasitics ../src/annotate/mac.spef.gz

Step4: timing报告:

满足时序要求,功耗分析才有意义

check_timing update_timing report_timing

tep5: 读入switching_activity文件

读后仿产生的VCD/SAIF文件将真实的翻转率反标到Net上,在read_vcd或者read_saif时要注意通过-stripe_path选项指定合适的hierarchical层次,否则activity反标不上;

-list_not_annotated列出没有被反标的对象;

读入saif文件:

read_saif "../sim/mac.saif" -strip_path "tb/Dut" report_switching_activity -list_not_annotated

读入vcd文件:

read_vcd "../sim/vcd.dump.gz"-strip_path "tb/Dut" report_switching_activity -list_not_annotated

tep6: 执行功耗分析

在得到switching activity之后,使用update_power来将其反标,使用report_power来报告power值。

check_power update_power report_power

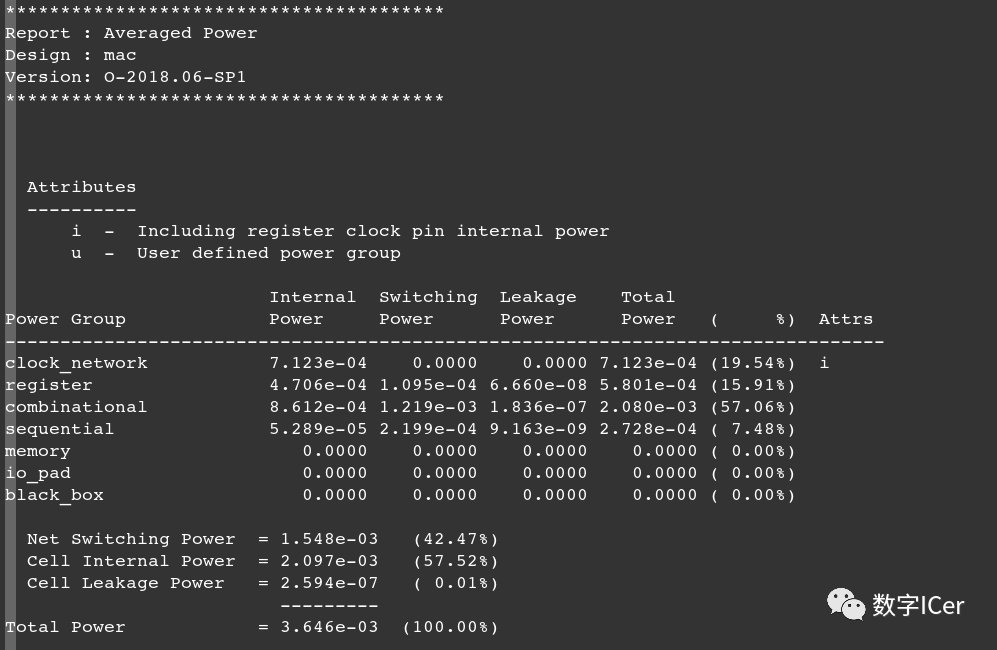

读入saif文件的功耗报告

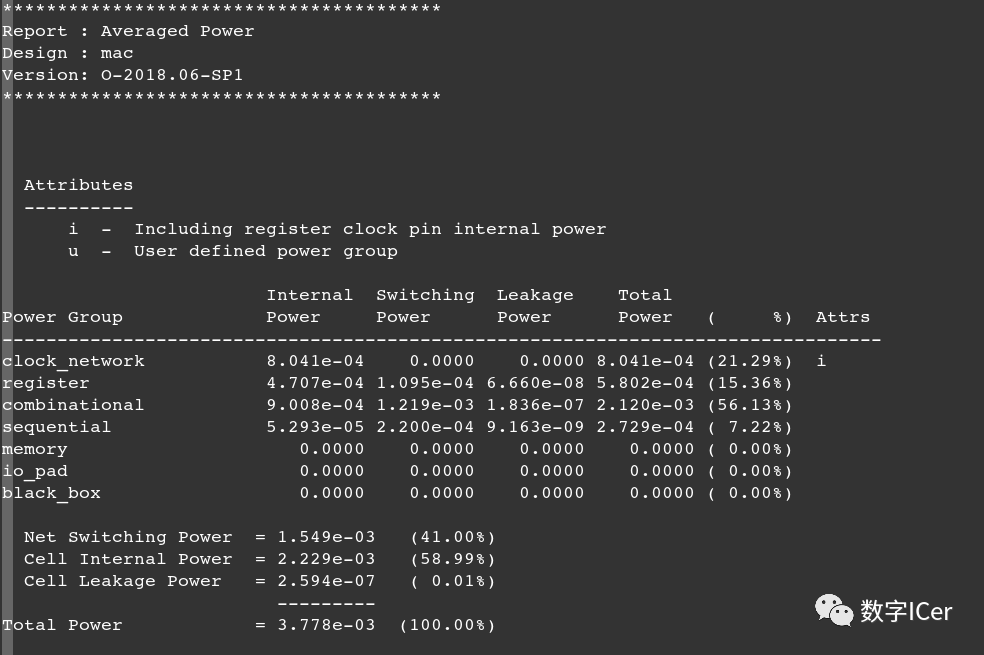

读入vcd文件的功耗报告

可以看出saif/vcd文件的功耗略有差异。

附

Averaged Power Analysis Mode Script脚本:

set power_enable_analysis TRUE set power_analysis_mode averaged ##################################################################### # link design ##################################################################### set search_path "../src/hdl/gate ../src/lib/snps . " set link_library " * core_typ.db" read_verilog mac.vg current_design mac link ##################################################################### # read SDC ##################################################################### read_sdc ../src/hdl/gate/mac.sdc set_disable_timing [get_lib_pins ssc_core_typ/*/G] ##################################################################### # set transition time / annotate parasitics ##################################################################### read_parasitics ../src/annotate/mac.spef.gz ##################################################################### # check/update/report timing ##################################################################### check_timing update_timing report_timing ##################################################################### # read switching activity file ##################################################################### ##read_vcd "../sim/vcd.dump.gz"-strip_path "tb/Dut" read_saif "../sim/mac.saif" -strip_path "tb/Dut" report_switching_activity -list_not_annotated ##################################################################### # check/update/report power ##################################################################### check_power update_power report_power quit

审核编辑:汤梓红

-

Cadence功耗分析步骤2023-09-06 2964

-

【智能控制】时间序列分析(Time Series Analysis)2017-09-24 1986

-

RF微波USB功率计或传感器和Power Analysis Manager软件的创新应用2019-10-24 1432

-

PTPX的常用流程有哪些? 为何从这个入手2022-06-10 4428

-

Analysis of dv/dt Induced Spur2009-11-26 643

-

THERMAL DESIGN OF POWER MOSFET2009-11-29 612

-

Circuit Analysis II with MATLA2010-02-10 718

-

中国电源产业的发展与分析2009-07-10 573

-

Proteus程序之AMP应用POWER2016-01-18 651

-

FPGA程序之logic_analysis2016-01-20 453

-

Moving_Average2016-02-22 291

-

详细介绍如何使用Analysis Studio进行数据的多维分析2021-10-14 4728

-

PTPX功耗分析之Peak Power Analysis2022-10-24 9017

-

基于UPF的低功耗数字后端设计实训课2023-02-26 3431

-

浅谈半导体芯片失效分析Analysis of Semiconductor Chip Failure2024-07-17 2244

全部0条评论

快来发表一下你的评论吧 !