PLL为什么是这么一个结构呢?

描述

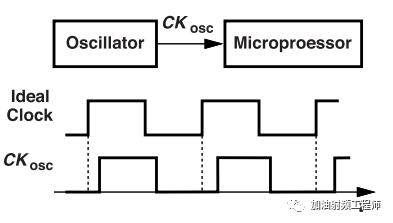

如果用一个自由振荡的振荡器,给MCU提供时钟。会咋样呢?

首先,得说一下,简单的LC自由振荡的振荡器的频率很脆弱。

哪哪都会影响到它。

供电大小变化,它会变;环境温度变化,它会变;工艺角变化,它也会变。

所以,如果用MCU提供时钟的话,假设环境温度缓慢变化,则振荡器的输出频率也会缓慢变化,这样就会引起随机相位累积。

单独看,可能看不太出来,如果把它和标准时钟输出放在一起,就能感受到变化。

你会发现,CKosc的上升沿离标准时钟的上升沿越来越远。

而MCU的运行是靠时钟的上升沿或者下降沿来判别的,你上升沿和下降沿变那么多,MCU可能就运行不正常了啊。

为了避免这个事情发生,就需要对振荡器的相位进行控制。

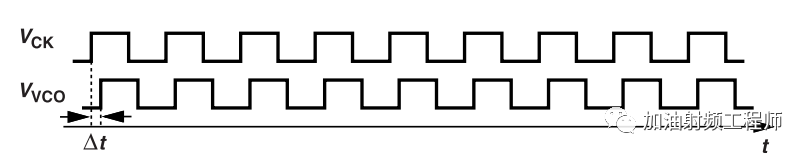

控制的目的,是希望VCO的相位与参考时钟的相位对齐。

如下图所示,这边VCO的上升沿相对于VCK有Δt 秒的偏移,那怎么消除这个Δt的偏移呢。

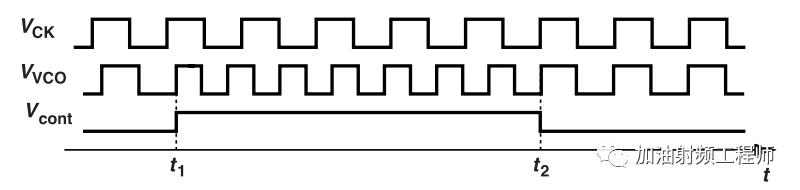

具体过程如下:

假设在t=t1时,VCO的频率突然变大,然后电路开始累积相位差,相位误差逐渐减小。在t=t2时,VCK和VVCO之间的相位差变为0,两信号的相位对齐。

此过程,即是将VCO的输出相位与参考相位对齐的过程,称为“锁相”。

从上面的过程中,可以看出,要使得VCO的相位和参考信号的相位对齐,需要做到以下两点:

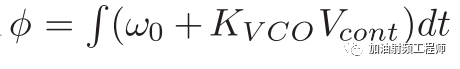

(1) VCO的频率瞬间改变,并且能够发生下面的积分运算。

(2) 用鉴相器来比对两个信号的相位差,以确定VCO和参考信号对齐的时间点。

将VCO的输出相位与参考相位对齐的过程,称为“锁相”。

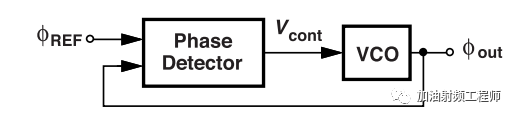

那怎么实时控制振荡器的输出相位呢,答案就是采用负反馈,如下图所示。

将输出信号的相位与参考信号的相位进行比对,用鉴相器输出的Vcont去调节VCO的频率和相位。

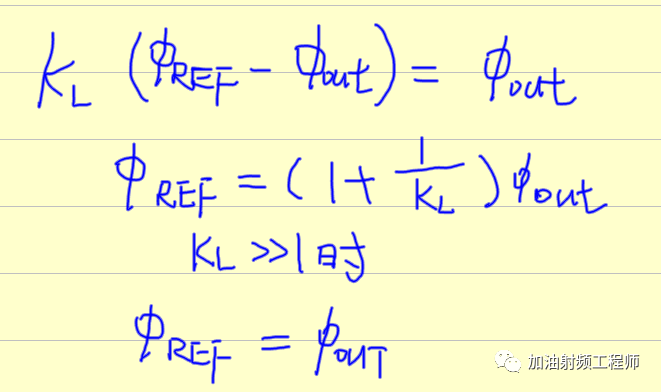

如果环路增益足够大,则

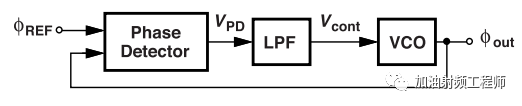

鉴相器的输出是周期性脉冲,这会对VCO的性能产生影响。

为了解决这个问题,可以在鉴相器和VCO之间加一个低通滤波器,抑制鉴相器输出的高频分量。

这种负反馈电路,即称为锁相环(PLL)。当φin − φout不随时间变化(或者变化很小时),即称环路锁定。也就是说,这个环路的目的,是使得φin = φout,那如果是这个目的的话,为什么不直接用一根线连接呢。

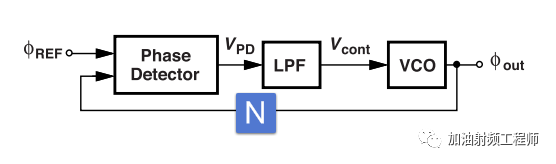

这是因为,如果在反馈回路上,加上一个分频器,那锁相环就可以产生和参考信号差不多稳定,但是频率更高的信号。

审核编辑:汤梓红

-

如何测量PLL的频率呢?2024-02-19 425

-

LMX2820 PLL_NUM / PLL_DEN减到最低项是什么意思呢?2024-11-11 473

-

为什么ARM这么流行呢?2013-03-28 2300

-

请问AD9361的一个PLL对应几个VCO分频器呢?2018-12-18 2754

-

SAC内部是个什么结构呢2021-10-09 2664

-

怎样去定义一个结构体数组呢2021-10-14 1764

-

为什么实际距离与理论值之间会有这么大的差距呢?2009-09-02 2827

-

模拟PLL,模拟PLL是什么意思2010-03-23 2854

-

PLL锁定过程的两个步骤2018-05-11 12537

-

PLL芯片接口方面最常见的11个问题2021-10-20 4403

-

DDS与PLL的区别解析2023-06-28 4774

-

如何建立一个简单的PLL电路2023-07-10 2243

-

怎么用pll电路把一个12M的频率倍频到2.4g的?2023-09-02 2043

-

PLL用法2025-06-07 1641

全部0条评论

快来发表一下你的评论吧 !