浅谈IC验证设计通用流程

EDA/IC设计

描述

数字验证处于数字IC设计流程的前端,属于数字IC设计类岗位的一种。主要是对数字前端的设计做验证。

随着芯片规模不断加大,在IC设计过程中验证的复杂度也进一步加到,需要的用到的岗位人数也越来越多;很多大公司,数字前端设计工程师与验证工程师的比例已经达到1:3。

正因为芯片的高风险,才凸显了验证的重要性。在流片之前,通过验证人员的验证活动,发现所有的设计bug,这就显得特别重要。

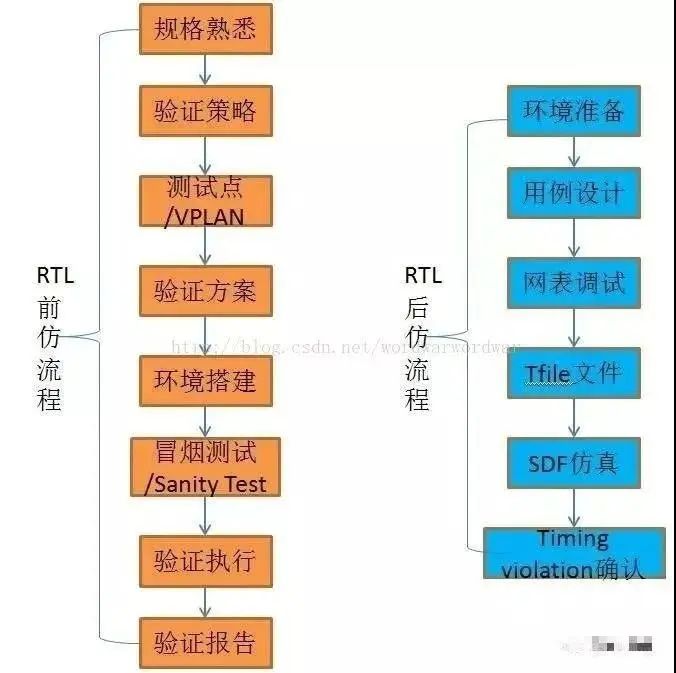

下图是一副比较完整的芯片端到验证端流程图,大多数公司的验证流程是大同小异的,差异点在于各个流程中具体做的事情。

验证做任何事情都需要按照一定的流程来走,否则很容易陷入混乱之中,对刚入门的新手来说,更是如此。通用流程大致如下:

1)提取测试点,明确验什么

分析FS/浮点平台,提取芯片的规格及测试点;

分析AS/定点平台,提取测试点;

分析DS,提取测试点并识别asic与算法的不一致点。

2)制定验证方案,明确怎么验

刷新测试点列表,明确测试点的覆盖方式:功能覆盖率、代码覆盖率、直接用例;

验证环境的搭建策略,这个步骤是可以做成自动化工具的;

验证的重点难点,提前识别重难点,并制定相应的对策;

刷新用例列表,明确测试用例的方法及步骤。

3)用例执行,随机测试,发现bug

执行直接用例,发现大部分的bug;

带随机的大量测试,试图撞出bug。

4)完备性分析,确保无漏验

FA/AS完备性确认,确认FS/AS中的所有点都已纳入测试点,并确保已被覆盖,包括应用场景;

接口完备性确认,保证所有的接口时序都已覆盖,包括正常时序及异常时序;

覆盖率确认,分析所有的代码覆盖率、功能覆盖率,保证全部覆盖;

代码分析,熟练掌握电路的实现逻辑,保证所有的电路corner都已覆盖。

上述这几个步骤是一个比较规范的流程,只要每个步骤都做好,基本就能做到无漏测、零漏验。

编辑:黄飞

- 相关推荐

- 热点推荐

- IC设计

-

浅谈PCB设计七大流程2010-04-16 2924

-

【「数字IC设计入门」阅读体验】+ 数字IC设计流程2024-09-25 1257

-

浅谈PCB的制作流程2009-10-20 7122

-

IC设计流程2012-01-11 10727

-

我对IC设计流程的一些理解2013-01-07 5177

-

IC验证在现代IC设计流程中的位置和作用2020-12-01 2540

-

浅谈UWB与WMAN无线电系统的验证2021-06-02 1880

-

浅谈检测/校准用软件的可靠性验证2017-02-07 680

-

浅谈当代安全验证问题2017-09-07 1283

-

华大九天宣布IC设计解决方案已进入TowerJazz公司参考流程 通过iPDK验证2018-08-30 2516

-

数字IC设计流程2020-12-09 8285

-

数字IC前端后端的区别,数字IC设计流程与设计工具2021-11-06 2450

-

IC验证的主要工作流程和验证工具是什么?2023-05-31 3064

-

低功耗技术在IC设计中的应用 IC设计流程解析2023-06-27 1268

-

ic验证是做什么的 ic验证用什么语言2023-07-24 6541

全部0条评论

快来发表一下你的评论吧 !