不同的电源环路布局

电源/新能源

描述

本文分析了不同的电源环路布局,同时考虑了热管理和电气寄生效应。

结果表明,改进的布局可以显著降低工作温升,同时保持电气性能优势。

氮化镓 (GaN) 等宽带隙 (WBG) 功率半导体已显示出更好的开关性能、高可靠性和耐温能力,品质因数 (FOM) 是同类硅器件的 3 到 10 倍 。具有小芯片尺寸和导通电阻(RDS,on)降低寄生电容和电感,提高开关速度,减少开关损耗,从而实现更高的功率密度和效率。更高的频率需要一些设计注意布局改进,以最大限度地减少增加的热阻和电感。

现有的印刷电路板布局方法

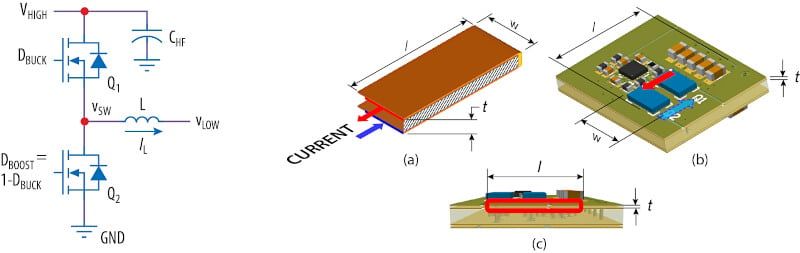

本文考虑的电源环路布局是大多数电源转换布局所围绕的半桥配置,包括两个功率半导体开关和一个旁路电容,如图1所示。电感器(l)平均开关节点v的输出电压电平西 南部= V低和电容器 C高频,而理论上不是必需的,因为它与V并行高,在实践中需要为高频电流提供低阻抗路径。

图 1.典型的半桥构建块。平行板短路传输线(a)。采用低阻抗传输线作为功率回路结构的半桥布局,具有相应的尺寸(b)和相同的(c)边缘视图。图片由博多的电力系统提供 [PDF]

将电源环路电感降至最低的 PCB 设计,由下式估算L圈 = µ0·无吨/瓦,之前已经讨论过 。图1(b、c、d)显示了电源环路的PCB实现。总之,PCB布局应尽量减少长度和厚度,同时增加宽度w。这可以通过图1(c)布局中使用的放置来实现,l和w由组件的物理尺寸决定,t由电压要求或PCB可制造性约束设置。

现有布局下的降压转换器散热挑战

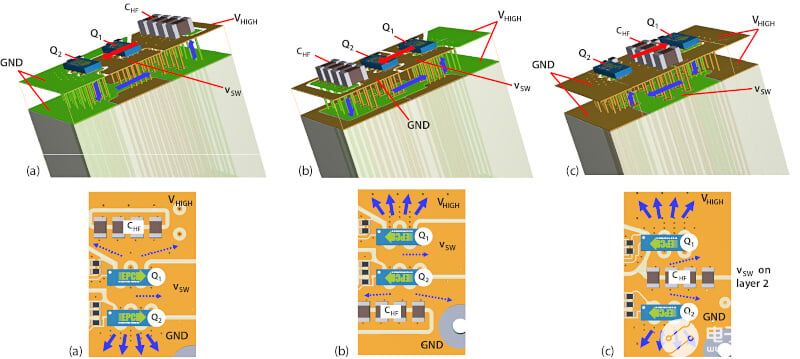

随着开关器件的温度在许多应用中成为电激活水平的限制因素,改善散热也成为主要的设计考虑因素,特别是在PCB级别,这在去除FET中的热量方面起着重要作用。在图1的降压转换器中,Q1在较大的热负载下,因为它同时表现出开关损耗和传导损耗,而Q2仅表现出传导损耗。图 2(布局 A)显示了图 1 (c) 的标准布局的分解图。在热方面,顶层具有更高的电阻路径,用于Q1,因为铜平面被中断C高频.Q2,另一方面,具有透明的铜平面,用于热量有效地扩散到PCB中并最终消散到环境中。此外,可用的过孔更少Q1以避免严重穿孔GND返回路径。因此,布局A对于降压转换器应用来说不是热优化的,需要改进布局以适应没有Q的更高损耗1过热。

图 2.电源环路布局的分解视图,其中参考节点和返回路径 (GND) 以绿色突出显示(顶部)。与箭头表示的热流路径相同的俯视图(底部)。图片由博多的电力系统提供 [PDF]

另一方面,考虑到升压转换器应用,其作用Q1和Q2反转,用Q2具有较高的损耗,在这种情况下,布局 A 表现良好,因为Q2具有较低的热阻。

优化降压转换器的布局

作为重新排列以热改进布局A以进行降压操作,C高频可以移动到侧面Q2因为两者都连接到GND(图2中的布局B)。这将需要使用第2层作为V高平面,它仍充当 AC 参考平面,并且尺寸 l、w 和 t 保持不变。热Q1现在有一条通往环境的良好路径,因此布局B在降压操作下应该表现得更好,但在升压操作下表现更差,因为Q2现在被阻碍C高频。

通过以电容器为中心的布局消除权衡

对于需要宽转换器工作范围或双向转换(降压和升压)的情况,布局A或B在热上仅限于一个FET或另一个FET。此外,在这两种布局中,Q1 和Q2紧密放置,因此产生的热量集中在较小的区域。这些问题可以在布局C中通过以下方式解决:C高频介于两者之间Q1和 Q2.在布局 C 中,Q1和 Q2通过图 2 中所示的第 2 层中的交换机节点 (SW) 进行连接。布局C遵循规则以最小化环路电感,虽然传统上将开关和信号节点放置在外层,但对于低阻抗来说并不是必需的。两个节点V高和 V低由于以下原因,处于相同的交流电位C高频因此共同形成交流参考平面,并且不影响环路电感。

热优势在于布局C增加了两者之间的间距,并为两者提供了畅通无阻的铜平面。Q1 和Q2.此外,相邻过孔的空间更大,返回平面穿孔更少,开关节点可以被具有潜在EMI优势的直流平面屏蔽。

一些可能的缺点,在实践中并不重要,因为当使用单个封装栅极驱动IC时,间隔较远的FET可能需要更长的栅极驱动路径,并且在某些情况下,电容器可能比FET更高,而FET在安装散热器时必须容纳FET。

分析与验证

为了测试上述设计方案,使用了硬开关转换器,因为它们易于设计和易于理解的行为。在降压和升压操作中比较了三种布局设计的热性能。设计和制造具有每个电源环路布局的相同电路板。电压V高选择在 150 V 时,这是用于Q1 和Q2.转换比率固定为V低/五高= 0.25,这意味着Q1工作在占空比为 0.25 和Q2在0.75。直流电感电流固定在IL= 15 A,因为这接近电感的饱和值,而所选FET的适中值。因此,转换器在所有测试用例中处理562W。开关频率F西 南部= 选择100 kHz以提供真实的FET功耗值。以上测试参数是所进行测试的基线。Q1在降压模式下具有热过载,并且Q2在提升模式下。

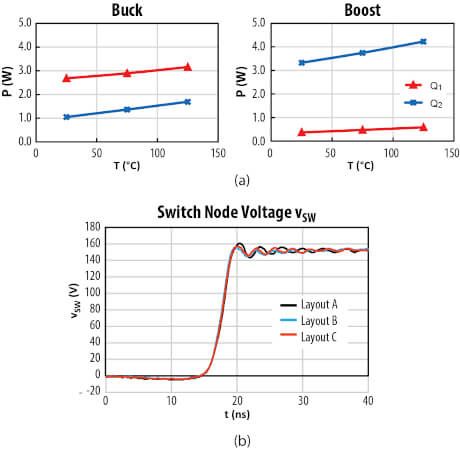

图 3.a) 损耗模拟结果,b) 开关节点电压 v西 南部用于降压转换器 Q1打开过渡。图片由博多的电力系统提供 [PDF]

电气仿真和测量

为了估计FET中的散热,在LTspice™中进行了电气仿真,其中包括估计的PCB寄生效应。对FET损耗进行了仿真,作为设定频率、占空比和温度的函数。结果如图3a所示。

测量开关性能以显示不同布局之间的电感差异。图3b所示的开关波形显示了接通Q1在降压操作期间。可以看出,这三种布局在振铃方面显示出微小的差异,表明对寄生电感的影响很小。

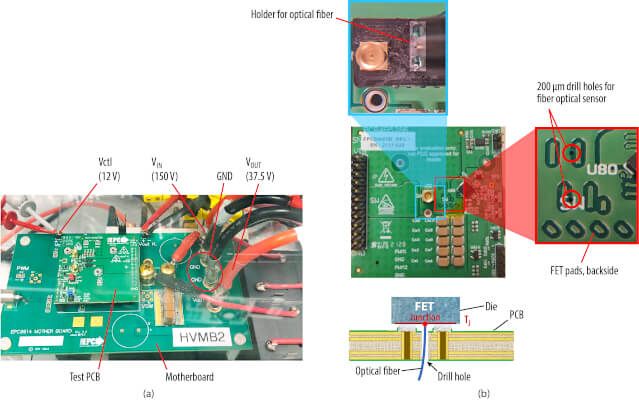

散热测试设置

热测试在具有受控气流的强制风冷测试箱中进行。图4显示了测试连接和实验设置。对于热测量,在焊盘之间的PCB上钻一个200μm宽的孔,以提供光学热传感器(OPSense® OTG-F传感器)的访问。该传感器具有抗EMI性能,并且具有极小的热质量。

图 4.a) 与主板和测试 PCB 的电气连接,用于散热测试。b) 光学传感器测量设置,显示光纤传感器的 PCB 钻孔。图片由博多的电力系统提供 [PDF]

热仿真模型

使用6SigmaET [4](一种商用热和CFD软件)进行热仿真,以验证测量的观测结果。PCB布局与所需的所有细节(铜导体,过孔,设备)一起导入软件。代表性数据点用于通过测量进行验证。

强制空气对流结果

第一组测量是在 400 LFM 气流下对三种布局执行的。从图3所示的降压和升压配置的热仿真结果来看,高端FET上的最高温度表明布局A在升压方面具有热优势,而布局B在降压模式下更有效地散热。

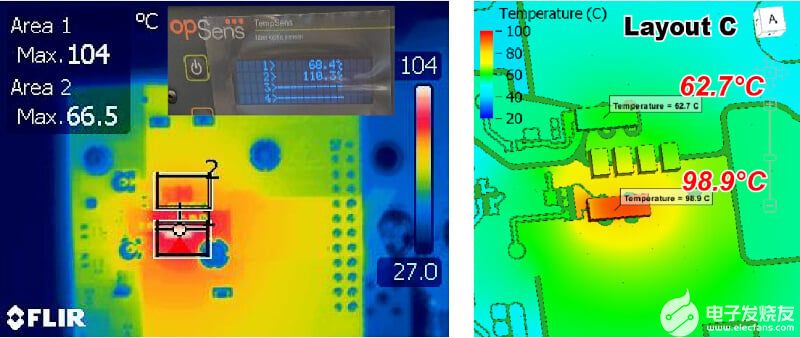

图 5.在升压下,布局C的测量(红外和光纤温度传感器)和模拟结果(表面温度)。图片由博多的电力系统提供 [PDF]

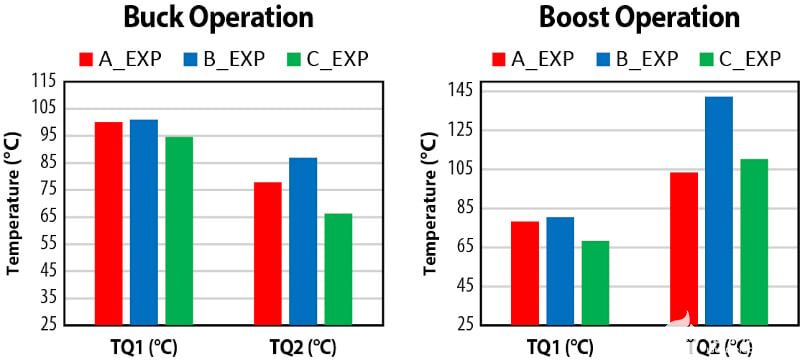

与A和B相比,布局C在最佳操作模式(A在升压模式下,B在降压模式下)具有与A和B相似(5%以内)或更好的热性能,并且在次优操作模式下(A在降压模式下,B在升压模式下)比布局A和B有显着改进。图6显示了降压和升压操作的三种布局的测量Q1和Q2温度。结果表明,布局C在双向操作中没有热损失,而布局A在降压(温度提高10%)和B在升压(温度升高25%)时的热性能显着降低。使用散热器进行的其他测试也得出了类似的结论,由于布局C中更好的冷却效果和更大的Q1和Q2间距,温度较低[5]。

图 6.三种布局的测量结果和温升比较摘要。图片由博多的电力系统提供 [PDF]

结论

三种布局 A (C高频 与 Q1 相邻),B (C高频 邻近Q2)和 C(介于Q1和 Q2)显示出可比的电气性能,在振铃频率上观察到的微小差异。实验支持这样的假设,即在典型设计条件下,布局A针对升压转换器操作进行了热优化,布局B针对降压操作进行了优化。布局 A 在降压操作下受到热挑战,布局 B 在升压操作下受到热挑战,如果不在最佳模式下运行,则会出现较大的热损失(高峰值温度)。

布局 C 提供大而无遮挡的铜平面和更大的间距Q1 和Q2布局C被证明在任何工作条件下都是热可行的,特别适用于各种应用,如逆变器、D类放大器和太阳能优化器,以及双向应用,如电池接口,在测试中观察到的缺点最小。

-

电源环路响应测试:伯德图实测指南#伯德图 #示波器 #电源环路响应 #电源稳定性测试安泰小课堂 2025-10-28

-

环路补偿原理及为什么要环路补偿2024-11-19 9237

-

AC-DC环路布局设计原则2024-10-24 1915

-

氮化镓晶体管电路的布局需要考虑哪些因素?2023-02-24 13048

-

利用PCB布局技术优化电源模块性能2022-01-06 611

-

介绍优化SIMPLE SWITCHER电源模块性能的最佳PCB布局方法、实例及技术2021-12-28 1319

-

开关电源环路补偿.2021-09-18 1687

-

【电源篇】PCB布线布局2021-07-27 4641

-

电源环路增益:电源环路增益的基本工作原理概述2019-04-30 7204

-

电源设计布局的热循环2018-10-22 1818

-

电源哪些部分影响电源的环路?好的环路有哪些指标决定?2018-10-03 13015

-

开关电源环路设计2016-05-03 1048

-

开关电源布局和布线2015-07-21 17857

全部0条评论

快来发表一下你的评论吧 !