在设计中使用 IP 的方法

描述

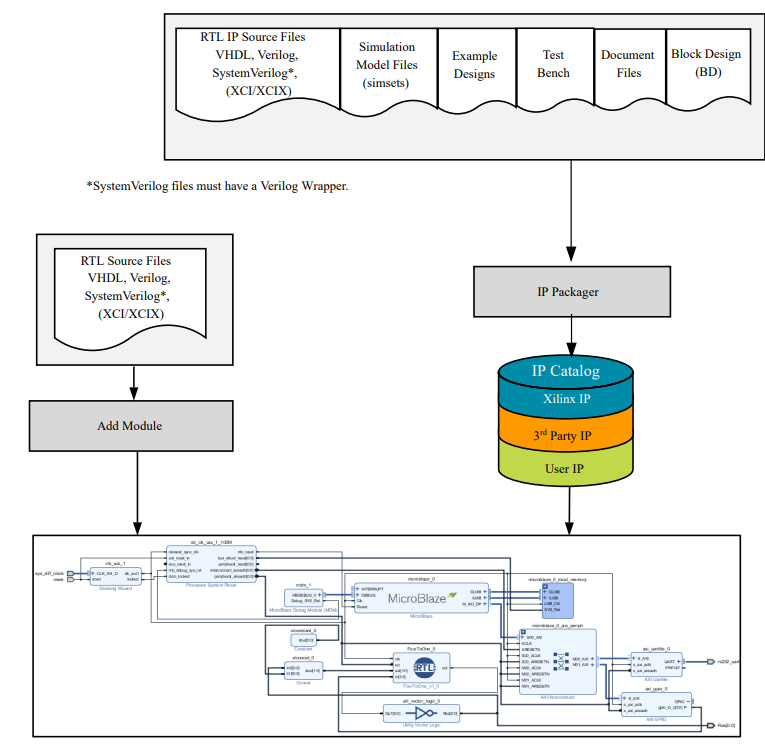

Vivado Design Suite 可提供围绕 IP 的设计流程,支持您将来自各种设计的 IP 模块添加到自己的设计中。此环境的核心是可扩展的 IP 目录,其中包含 AMD 赛灵思提供的即插即用 IP。IP 目录可通过添加以下内容来加以扩展:

来自 System Generator for DSP 设计的模块(源自 Simulink 算法的 MATLAB)

Vivado 高层次综合 (HLS) 设计(C/C++ 算法)

第三方 IP

使用 Vivado IP 封装器工具封装为 IP 的设计

下图显示了围绕 IP 的设计流程:

在设计中使用 IP 的方法包括:

使用“Managed IP”(托管 IP)流程来自定义 IP 并生成输出文件(包括综合后的设计检查点 (DCP)),这样即可

保留自定义设置以供在当前和未来版本中使用。如需了解更多信息,请参阅第 3 章:使用“Manage IP”工程。

从工程访问 IP 目录,以自定义 IP 并将其添加到设计中。IP 文件可存储在工程本地,或者对于小型团队规模的工程,建议将其存储在工程外部。

源文件的添加方法是右键单击 IP integrator 画布并将 RTL 模块添加到设计图中,这样即可提供“RTL on Canvas”(画布上的 RTL)。

在非工程脚本流程中创建并自定义 IP,并生成输出文件(包括生成 DCP)。

在工程模式或非工程模式下使用 IP 的方法是引用已创建的赛灵思核实例 (XCI) 文件,推荐在处理由多名团队成员协作完成的大型工程时采用此方法。

按设计进程浏览内容

硬件、IP 和平台开发

为硬件平台创建 PL IP 块、创建 PL 内核、子系统功能仿真以及评估 Vivado 时序收敛、资源使用情况和功耗收敛。还涉及为系统集成开发硬件平台。本文档中适用于此设计进程的主题包括:

第 2 章:IP 基础知识

第 3 章:使用“Manage IP”工程

系统集成与确认

通过板级原理图和开发板布局来设计 PCB。还包含功耗、散热以及信号完整性注意事项。本文档中适用于此设计进程的主题包括:

处理调试 IP

IP 术语

Vivado IDE 使用下列术语来描述 IP、其存储位置及其表述方式。

-

如何在易e语言代码中使用HTTP代理IP2022-08-05 7915

-

如何在java代码中使用HTTP代理IP2022-08-04 3013

-

如何导出IP以供在 Vivado Design Suite 中使用2022-07-08 4535

-

在Keil Arm中使用malloc函数的方法是什么?2021-07-01 1354

-

在Vivado中使用SRIO高速串行协议的IP演示官方例程2021-04-15 7862

-

请问如何在设计中使用IP?2020-08-14 1139

-

可以在EDK中使用ISE的IP核吗?2020-03-24 1705

-

如何在IP Intergrator中使用vhd文件?2019-03-07 3265

-

破解ip的方法2016-11-20 4500

全部0条评论

快来发表一下你的评论吧 !