如何使用3DIC Compiler实现芯片堆叠设计

制造/封装

描述

前言

先进封装从MCM发展到2.5D/3D堆叠封装,目前发展最快的制造商是TSMC。TSMC从Foundry端延伸入2.5D/3D先进封装,称为3D Fabric。近十年来TSMC的2.5D先进封装技术经历了5代更新,硅载板的面积已经达到3倍光罩尺寸,最新技术可以集成8个HBM,支持eDTC,同时改进了TSV和TIM材料,以及厚铜互连,对于3D堆叠的PI、SI、Thermal和Stress等方面都有了很好的的改善。与此同时NVIDIA的A100单芯片面积为826mm2,逼近光罩尺寸极限,而大芯片面临低良率、成本增加的问题,这直接导致了Chiplet技术成为炙手可热的话题。TSMC在SoIC的未来十年的计划中描述每两个相邻工艺节点的bump pitch缩小70% ,从而达到每工艺节点2倍带宽密度的扩展,以及EEP(Energy Efficiency Performance)提升。

3D堆叠的设计流程

3DIC先进封装之前并没有统一的EDA设计流程和设计平台,Fabless只能通过使用传统的脱节的点工具链和流程来进行3DIC的设计。由于数据切换的不连贯性和不一致性,以及不同点工具间的设计环境的改变,这些都对3DIC先进封装的设计收敛带来巨大的挑战。芯和半导体为了应对这些挑战,提出了自主可控的3DIC先进封装设计和仿真平台。其中3D IC Compiler(以下简称“3DICC”)作为设计平台,涵盖HBM堆叠、异构逻辑芯片堆叠以及logic芯片上的memory堆叠流程,涉及TSV互连、basic logic die、中介层、局部硅桥等信息定义。3DICC堆叠设计流程主要包含如下七个步骤:

Prepare design library

Create die designs

Create floorplan/bumps/TSVs

Routing TSVs to backside bumps

Create top-level design

Assign nets, bumps, and TSVs

Perform 3D check

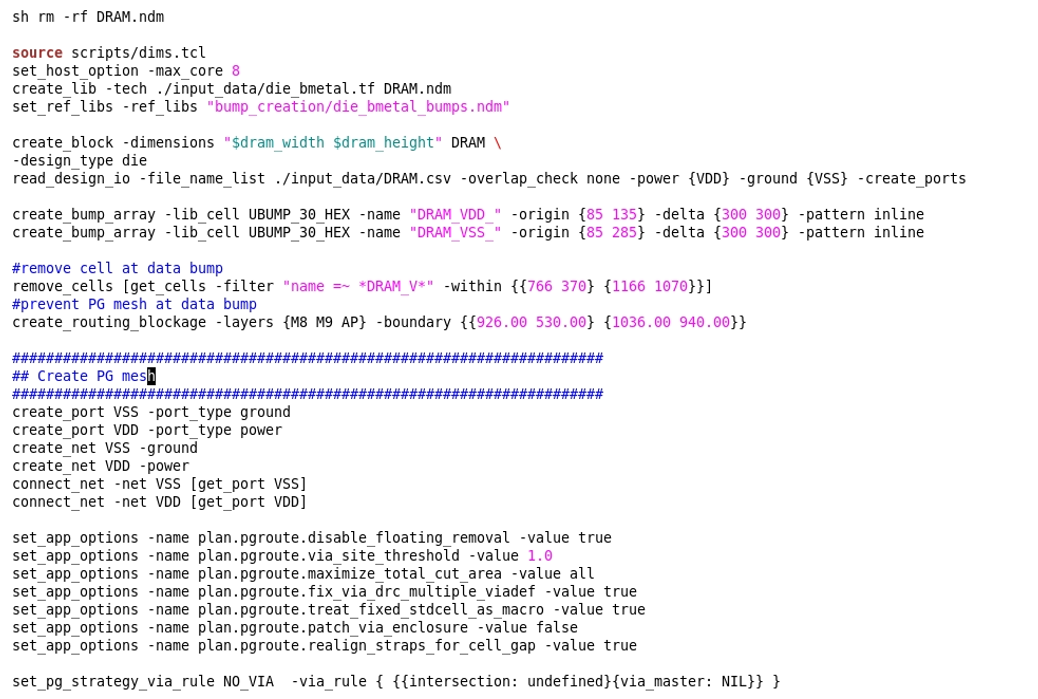

1.设计文件导入(DRAM NDM创建)

首先将3DIC设计所需的tf,ref_libs,csv等文件设置到tcl脚本中,创建所需ndm 数据。

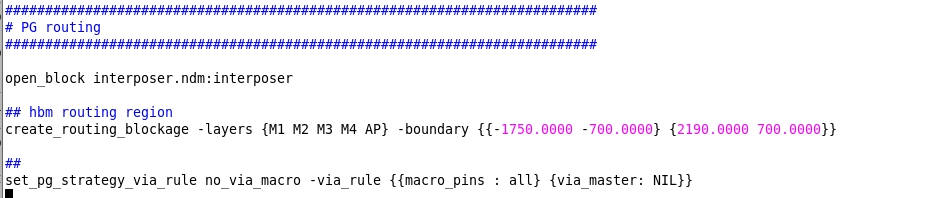

图1. 设置package int bdie tdie dram 的高度宽度,

block的创建,blockage的创建

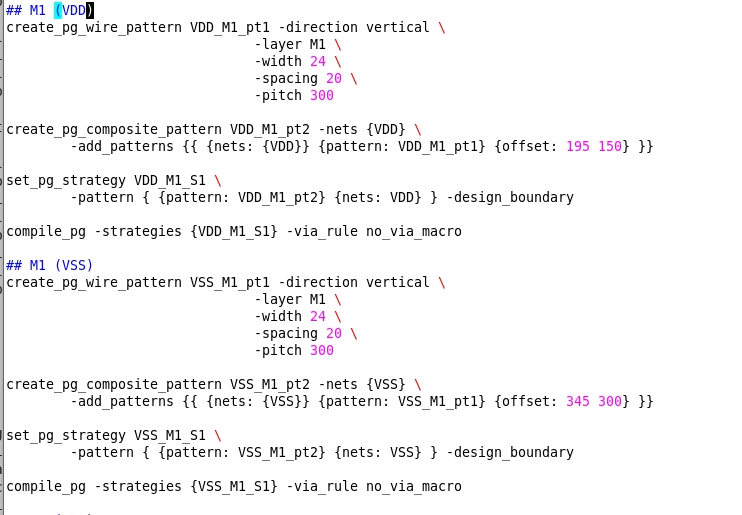

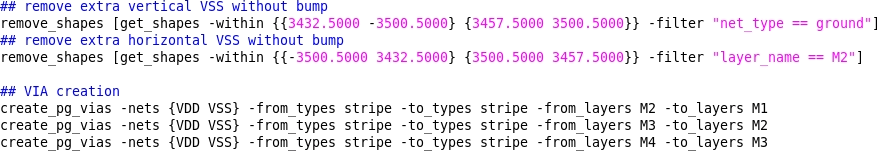

图2. create PG mesh设计定义,pg_mesh_pattern定义,

options设置,Create PG bump via array设置

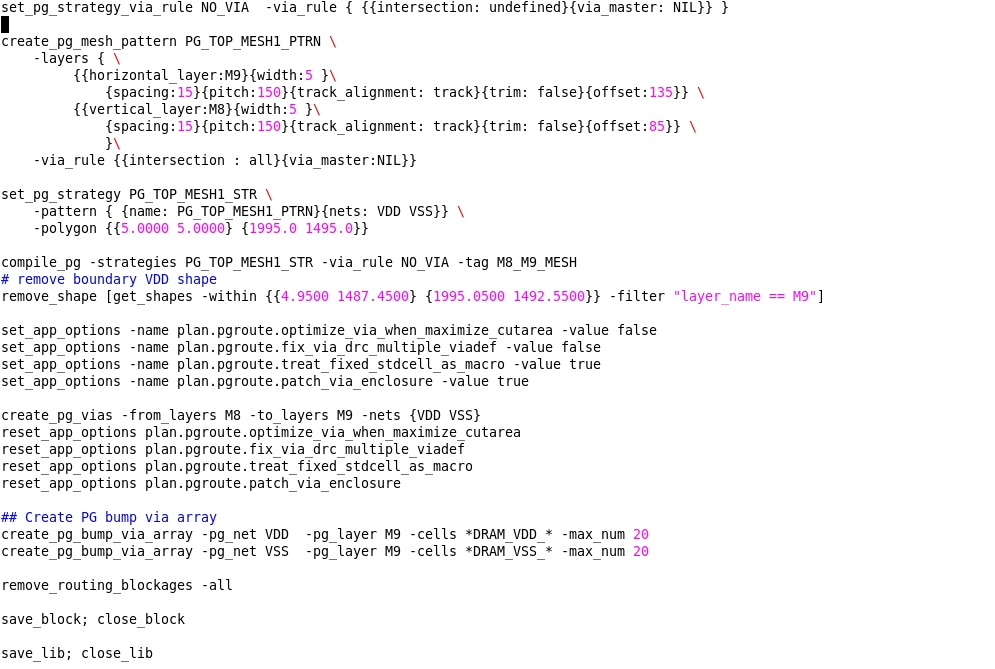

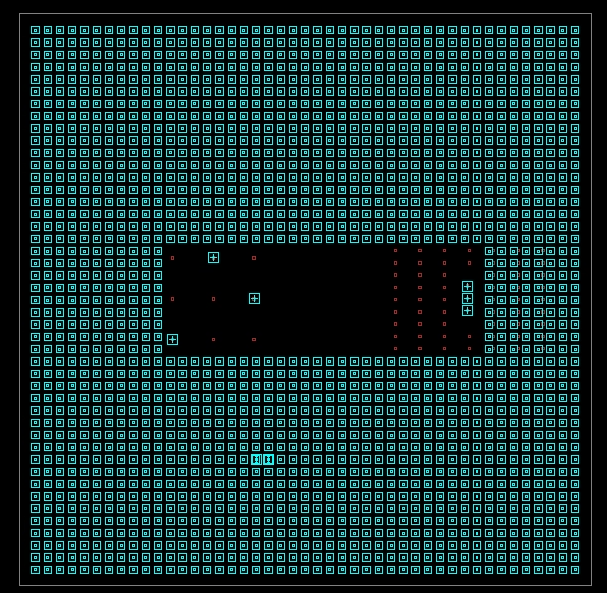

图3. DRAM 2D视图

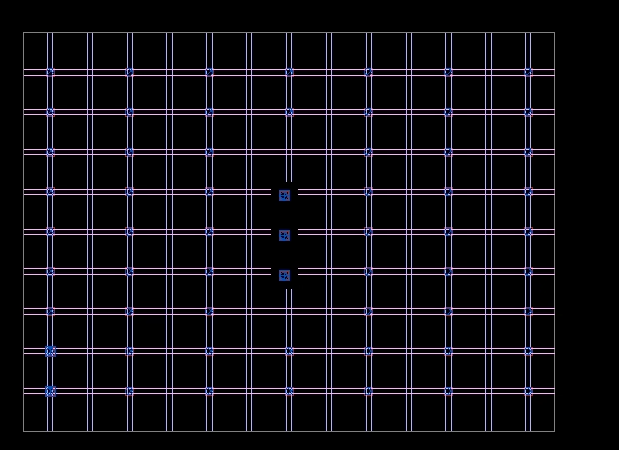

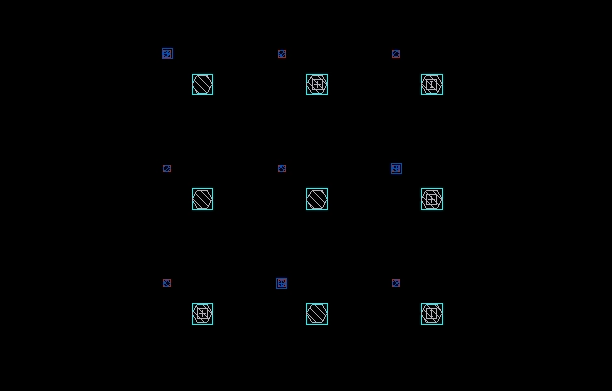

2. Die_Stack interposer package

以及top的创建类似DRAM设置

Die_Stack包含base_die 和 top_die。

图4. base_die.ndm

图5. top_die.ndm

Interposer 和package top 的ndm类似以上操作思路

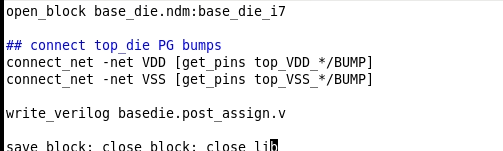

3. Base_inst_pg和interposer_pg

连接的设置

下面介绍下电源线连接的设置,在3dic_shell中打开base 和interposerdie database,接着连接DRAM和Base die的电源。

图6. connect_base_inst_pg的设置

图7. connect_interposer_pg的设置

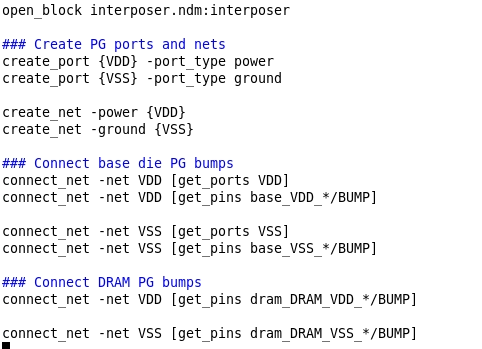

4.Create_interposer_c4bump的创建

下图是设置interposer中c4的创建的定义,包含name,lib_cell ,pattern,delta,origin 在3dic_shell窗口下打开interposer database进行操作。

图8. create_interposer_c4bump的设置定义

5.Create_pg_routes的创建

在3dic_shell中输入脚本中的设置。

图9. pg_routes的设置界面

图10. interposer 2D视图界面

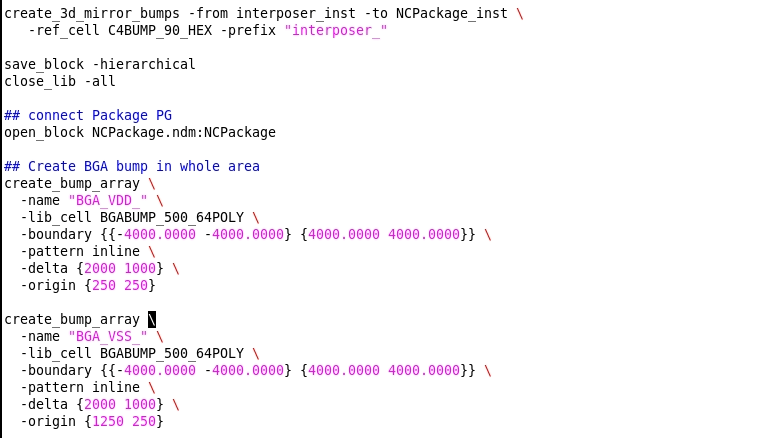

6.Mirror_bump_to_package

在3dic_shell里面打开之前创建的top. ndm, Mirror_bump 从interposer to NCPackage。

图11. mirror bump

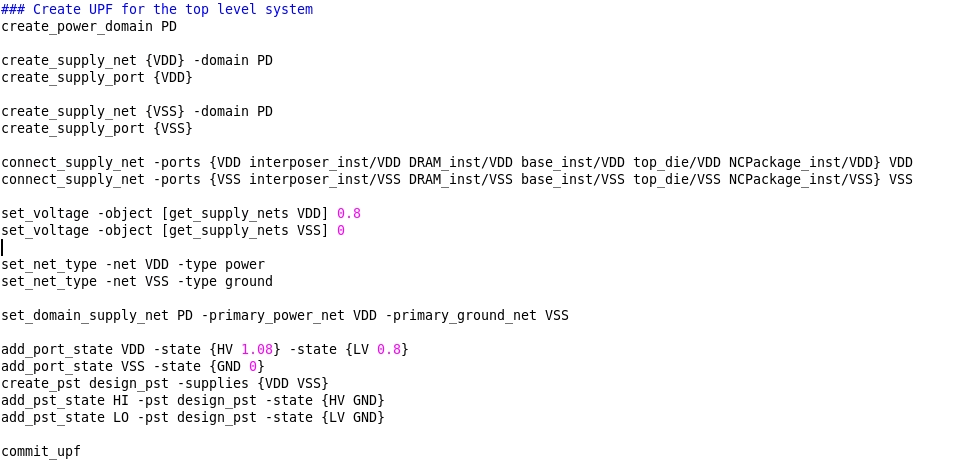

7. Commit_upf_connect_top_pg

在3dic_shell里面打开之前所建立的ndm database,比如:Interposer.ndm、DRAM.ndm、base_die.ndm、top_die.ndm、NCPackage.ndm;读入各自的upf文件,再连接各自的电源;创建top-level VDD/VSS ports and connect to interposer/die/package;创建 UPF for the top-level。

图12. upf的power连接

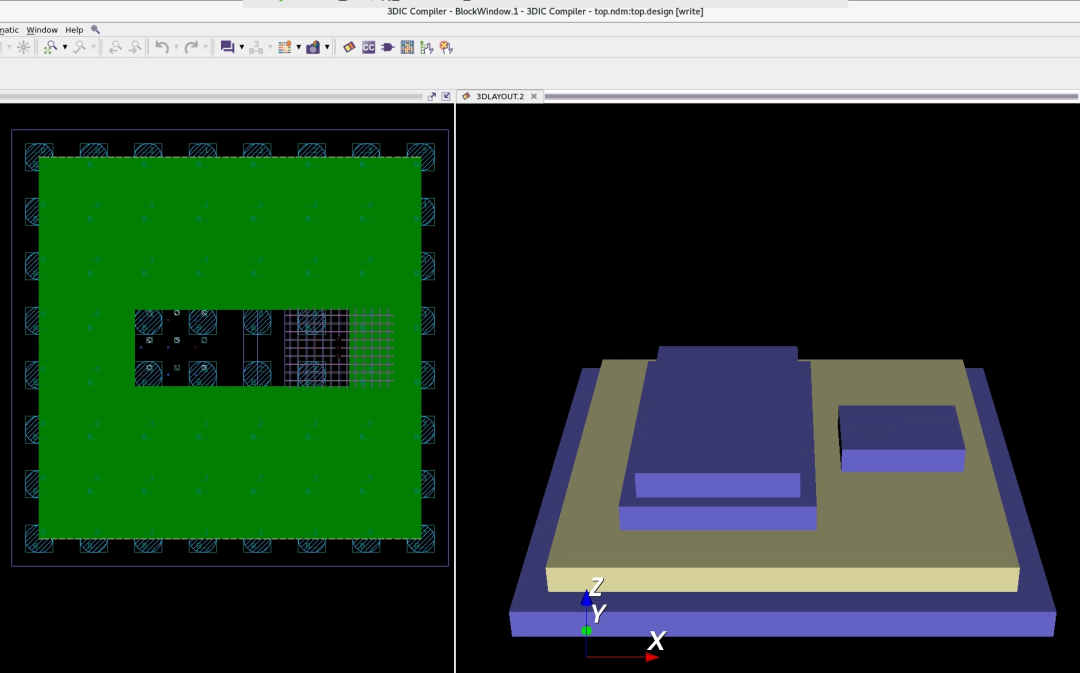

8.整体3D堆叠设计2D和3D效果示例图

在3DIC中设计的二维设计和三维立体视图的对比。

图13. 2D和3D堆叠设计界面

总结本文介绍了使用3DICC工具进行芯片堆叠设计的步骤。3DICC设计平台覆盖从架构规划、设计创建、设计实现到分析验证等全流程。能够支持多芯片系统集成,工作环境灵活高效,自动化布线支持。

审核编辑:汤梓红

-

如何打破安徽3DIC设计与大时代电源完整性之间的僵局2017-09-25 2154

-

如何去拯救3DIC集成技术?2021-04-07 1651

-

Altera藉助TSMC技术采用全球首颗3DIC测试芯片2012-03-23 1481

-

碳纳米管+RRAM+ILV 3DIC缘起!会否改变半导体行业?2019-08-05 3902

-

新思科技推出3DIC Compiler平台,转变了复杂的2.5和3D多裸晶芯片系统的设计与集成2020-08-28 4068

-

现在3DIC设计面临哪些挑战?2021-06-09 3226

-

芯和半导体联合新思科技业界首发,前所未有的“3DIC先进封装设计分析全流程”EDA平台2021-08-30 2035

-

芯和设计诀窍概述 如何使用3DIC Compiler实现Bump Planning2022-11-24 2380

-

谁说3DIC系统设计难?最佳PPAC目标轻松实现2023-04-21 1022

-

新思科技携手力积电,以3DIC解决方案将AI推向新高2023-06-27 2482

-

新思科技3DIC Compiler获得三星多裸晶芯集成工艺流程的认证2023-09-14 2256

-

行芯科技揭示先进工艺3DIC Signoff破局之道2025-06-12 1454

-

台积电日月光主导,3DIC先进封装联盟正式成立2025-09-15 1309

-

3DIC集成技术的种类介绍2026-03-09 812

全部0条评论

快来发表一下你的评论吧 !