Chiplet的IP新理念与设计工具

描述

随着半导体制程节点的持续演进,短沟道效应以及量子隧穿效应带来的发热、漏电等问题愈发严重,追求经济效能的摩尔定律日趋放缓。

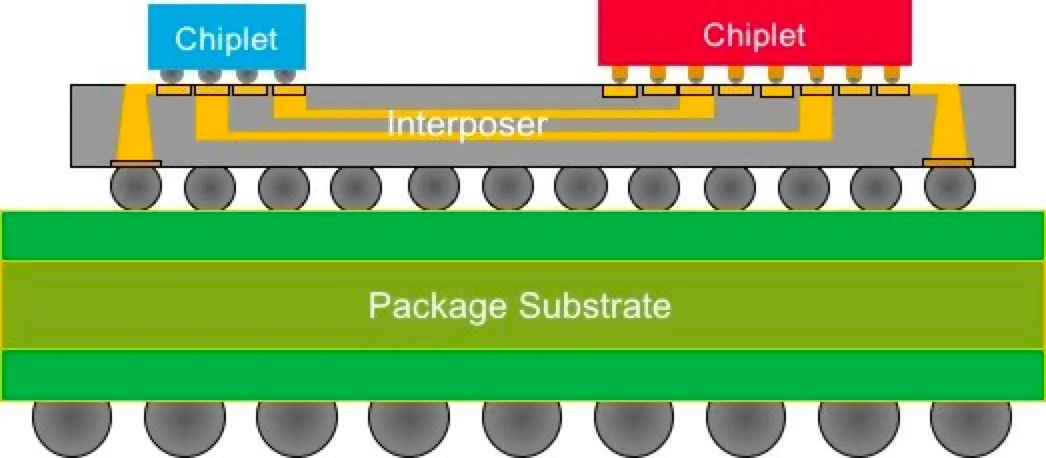

在此背景下,产业开始转向以先进封装为代表的新赛道,伴随着先进封装而出现的第一个新概念就是Chiplet:

这些类似乐高积木一样的功能模块通过中介层(interposer)连接在一起,然后附着在封装基底上。

英特尔的Foveros封装技术就是采用这种思路,通过2.5D堆叠而实现不同chiplets的累加堆叠的集成。

Foveros将会在传统无源中介层之上扩展裸片堆叠模式,可以在CPU、图像处理器和AI加速器等高性能逻辑器件之上叠加存储器。

这种技术可以将系统级芯片产品细分为许多不同的chiplets,其中I/O、SRAM和电源电路都可以在一个基础裸片上制造,然后在其上叠加高性能chiplets。

与传统SoC相比,Chiplet的思想是将不同的小芯粒通过先进封装形成系统芯片;这也意味着,更为专业的设计工具对Chiplet未来生态的发展至关重要:

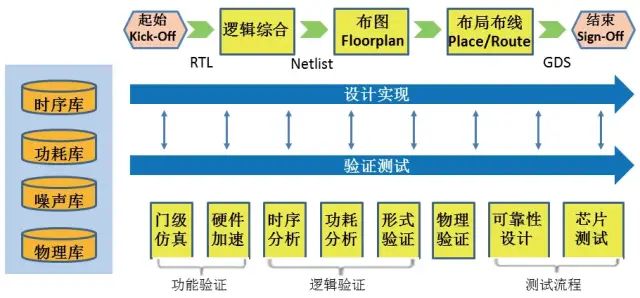

EDA设计流程图

Chiplet因为需要更多异构芯片和各类总线的加入,将会使得整个芯片的设计过程变得更加复杂:

相关半导体行业从业者就指出:在一个封装只有几百个I/O的时代,封装设计者还有可能用试算表(Spreadsheet)来规划I/O,但在动辄数千甚至上万个I/O互连的先进封装设计中,这种方法不仅太耗时,而且出错的机率很高。

基于资料库的互连设计,还有设计规则检查(DRC),都将成为先进封装设计的标准工具。

此外,以往封装业界习惯使用的Gerber档格式,在先进封装时代或许将改成GDSII档格式;整体来说,封装业界所使用的工具,都会变得越来越像Fab跟IC设计者所使用的工具。

特别是,在芯片的整体设计之前:为了把SoC拆解成Chiplet,相关的EDA工具需要芯片设计人员更多协同。

不仅是RDL Netlist、线路布局(Place & Route)的工具需要更新,设计人员还需要更多设计模拟工具来解决多晶片所衍生的电源一致性(PI)、讯号一致性(SI)、电磁相容(EMC)、散热(Thermal)等问题。

首先EDA工具需要在芯片互联接口的标准化方面进行改进;其次是可扩展性,Chiplet下芯片设计工程师需要同时对多个chiplets进行布局和验证。

由于其需要采用堆叠方式进行设计,那么将十分考验散热能力;对于EDA工具的要求就在于,如何保障不同chiplets间堆叠后产生的热度不会损坏芯片。

相比之下,头部EDA公司可能会略早发现这些挑战,不过由于行业都还在对此探索,因此不会有太大差距。

从当下Chiplet的角度来看:在相关标准还没完全确定,相关厂商提出的基础能力和标准各不相同的前提下;相关头部EDA公司在Chiplet领域是与国内和海外公司共同推进生态、制定标准的发展进程,因此对于中国厂商来说是一个机会。

就如作为全球排名第一的EDA解决方案供应商,新思科技也在致力于与国内的众多芯片设计公司一同探索相关Chiplet解决方案:

新思科技中国区副总经理朱勇强调:要使Chiplet做到通用化,不仅需要类似于UCIe等协议的定义,还需要国内外更多设计厂商的一同探索与发展;

新思科技对其保持一个欢迎的态度,如果将来标准能够普及开来,对国内的厂商更快地推出自己的Chiplet产品也是有益的。

当然,相较于设计工具,Chiplet的IP新理念也至关重要。

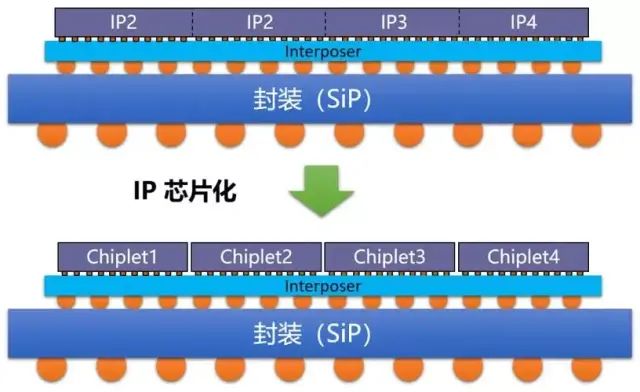

一些半导体IP核以硅片的形式提供,IP即是chiplets,旨在以芯粒形式实现IP的“即插即用”和“重复利用”。

以解决原有先进制程工艺芯片面临的性能与成本的矛盾,并降低较大规模芯片的设计时间和风险,实现从传统SoC封装的IP到先进封装中以独立的chiplets形式呈现的IP。

Chiplet的IP新理念

Chiplet的IP新理念在为芯片降低成本及加速产品迭代上至关重要:

如果在芯片设计阶段,就将大规模的SoC按照不同的功能模块分解为一个个的chiplets,那么部分chiplets则可以做到类似模块化的设计,而且可以重复运用在不同的芯片产品当中。

这样可以极大降低芯片设计的难度和设计成本,同时也有利于后续产品的迭代,加速产品的上市周期。

Chiplet的IP新理念在为降低芯片设计难度及提升灵活性上至关重要:

对于很多SoC厂商来说,原来设计一款大型的SoC芯片时,需要将大量第三方IP与自己的IP整合到一起,形成一个统一的SoC,然后采用同一个制程工艺进行制造:

而如果采用Chiplet模式,芯片设计厂商可以直接选择第三方的基于适合的工艺制程的以chiplets形式提供的IP,然后再通过先进封装技术将chiplets封装在一起即可;这样可以极大的降低芯片设计难度,提升灵活性和效率。

审核编辑:刘清

-

Chiplet技术给EDA带来了哪些挑战?2023-04-03 970

-

LT5400设计工具2021-05-30 775

-

芯原股份:正积极推进对Chiplet的布局2021-01-08 3617

-

利用FPGA设计工具减少设计周期时间和降低风险2019-02-13 5023

-

介绍 TI+WEBENCH+设计工具2018-06-13 7117

-

求求志同道合之人开发全新理念的可穿戴设备2017-07-04 2667

-

寻求志同道合之人开发全新理念的可穿戴2017-07-02 5794

-

找志同道合之人开发全新理念的可穿戴设备2017-07-01 4410

-

找志同道合的人开发全新理念的可穿戴设备2017-06-29 4508

-

笔记本+投影仪 职场报告新理念2010-01-25 734

-

面向芯片设计的测试新理念2009-12-17 687

-

全新WEBENCH Visualizer设计工具2009-11-11 1310

-

usb设计工具2006-03-25 985

全部0条评论

快来发表一下你的评论吧 !