Xilinx推出了新一代功耗评估工具:PDM

描述

在发布Vivado 2022.2的同时,Xilinx推出了新一代功耗评估工具:PDM(Power Designer Manager)。这里我们首先介绍一下它与XPE(Xilinx Power Estimator)的主要差异。

XPE可支持Xilinx所有芯片型号,而PDM目前仅支持Versal和Kria SOM产品。

XPE是一个Excel文件,而PDM是一个独立软件,需要单独下载单独安装。

(注:PDM并非集成在Vivado中)

因此,对于UltraScale或UltraScale+芯片,仍然需要采用XPE进行功耗评估。

PDM既提供Windows版也提供Linux版,下载链接如下:

https://www.xilinx.com/products/design-tools/power-design-manager.html

接下来我们再来看看PDM的一些特色:

针对Versal ACAP中的硬核如DDR控制器等提供设置界面,以实现更为精确的功耗评估。

提供输入时钟(来自内部或外部)设置界面。

提供BRAM/URAM/DSP工作模式设置。

PDM使用流程:

PDM支持两种使用流程:手工流程和导入流程。手工流程要求工程师手动输入各种参数,如时钟频率、翻转率、各类资源使用量以及使用模式等。导入模式可直接导入.xpe文件用于功耗评估。

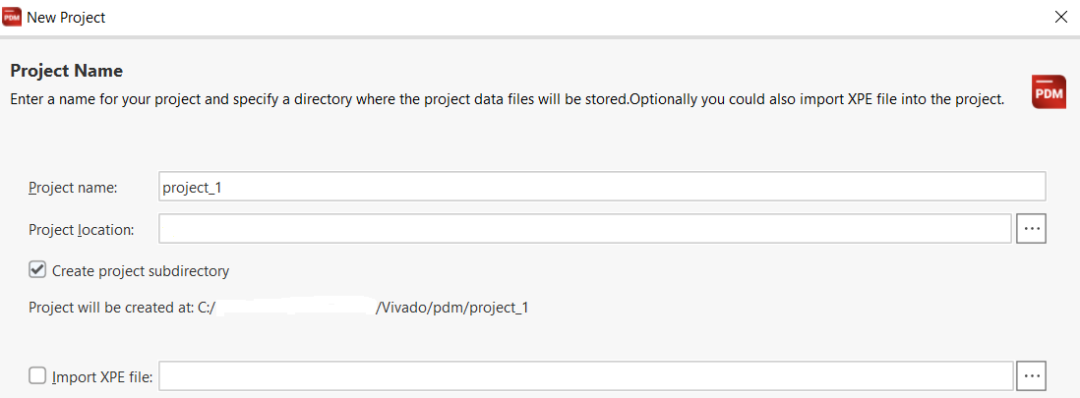

手工流程需要先创建PDM工程,然后填入具体芯片型号,如下图所示。

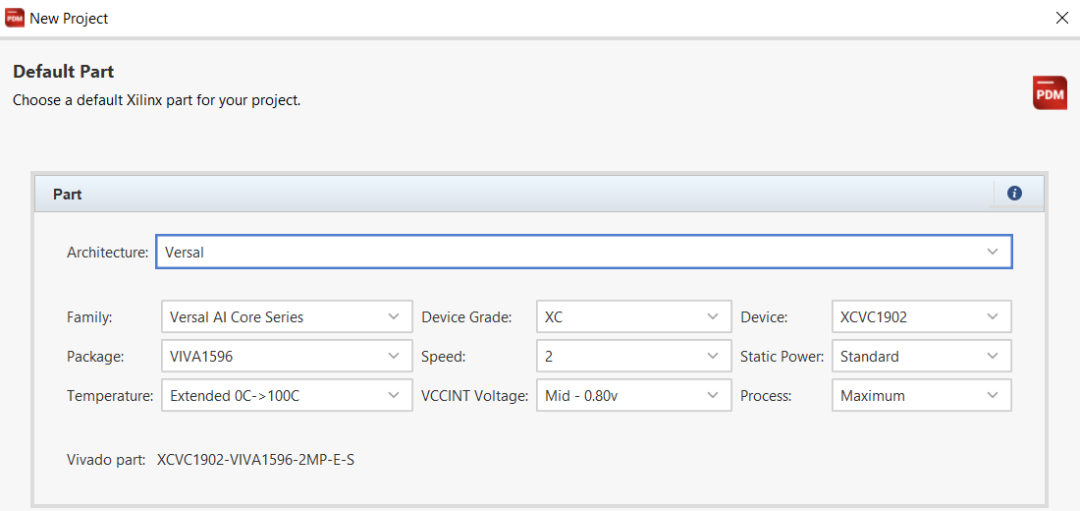

创建好PDM工程之后会显示如下界面。总体而言,这个界面由4部分构成:各类资源评估栏、整体功耗显示界面、环境参数设置界面和各类资源功耗显示界面。

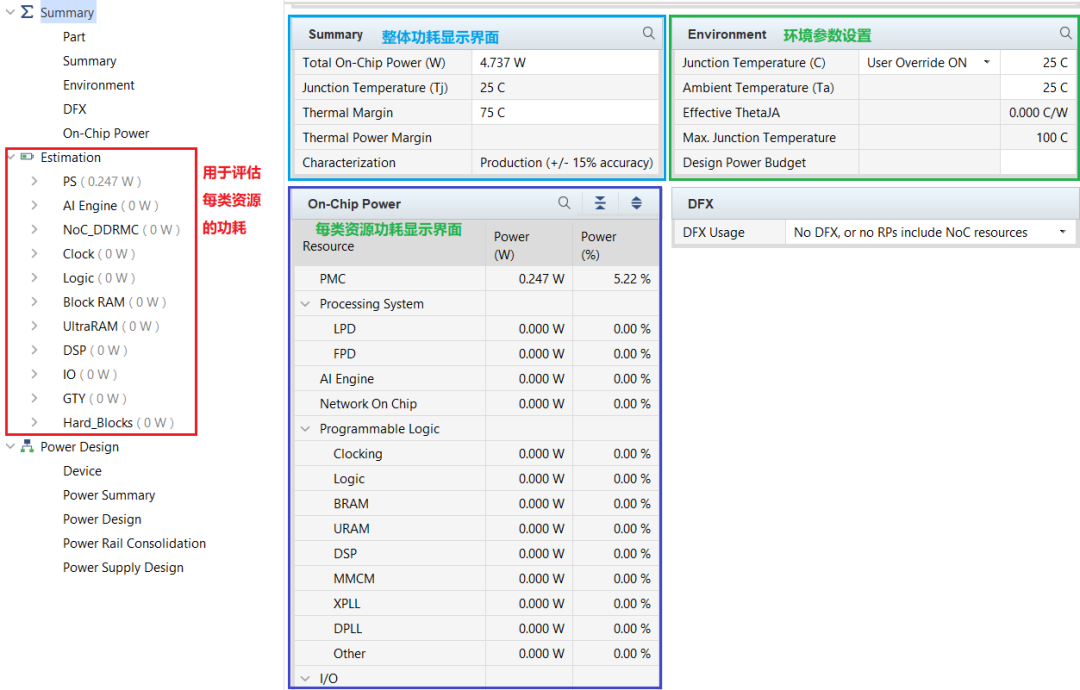

如果要评估PL部分的功耗,可先进行时钟设置。PDM提供了时钟设置功能,如下图所示,点击Estimation下的Clock,右侧界面随之出现Create Clock选项。

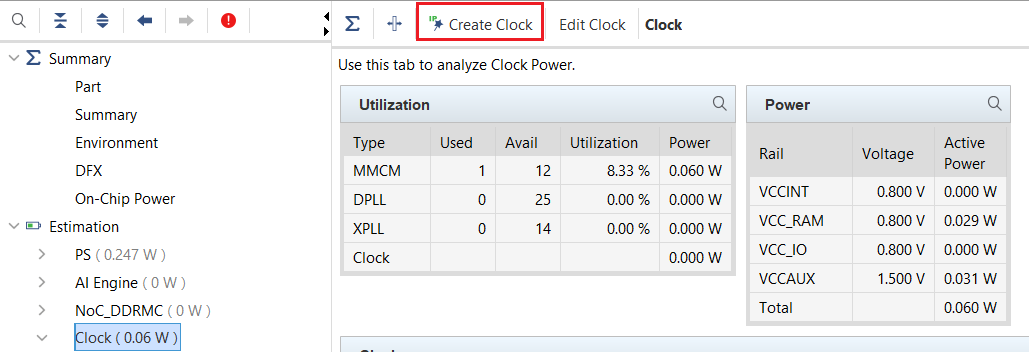

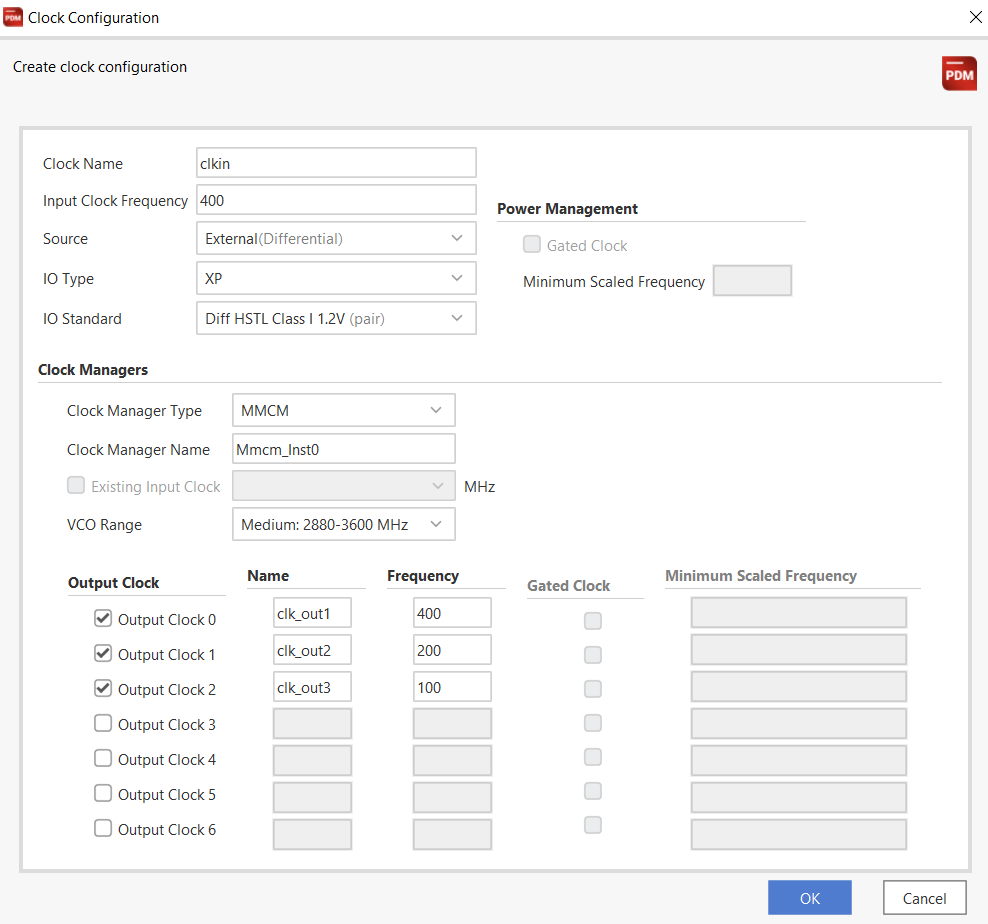

点击Create Clock,会弹出如下界面。在这个界面我们可以设置源时钟、时钟生成模块(MMCM还是PLL)以及生成时钟。

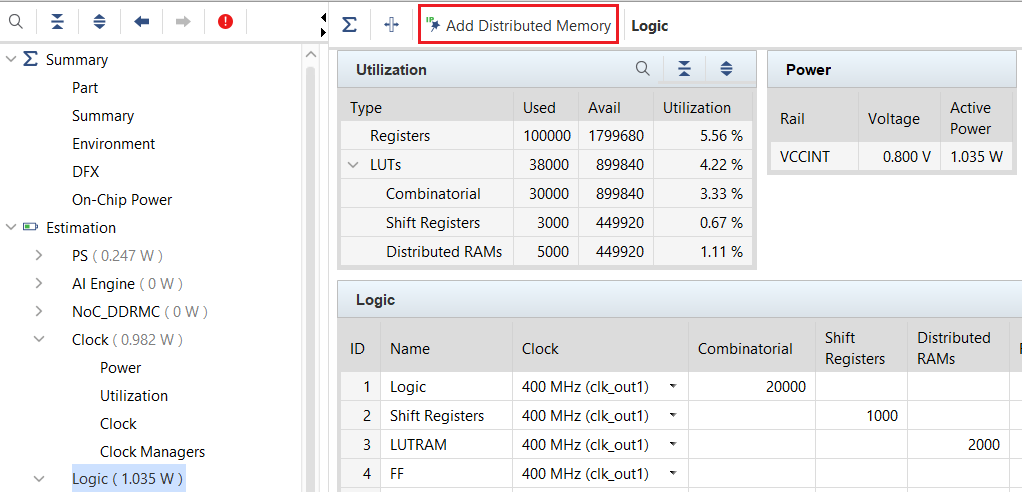

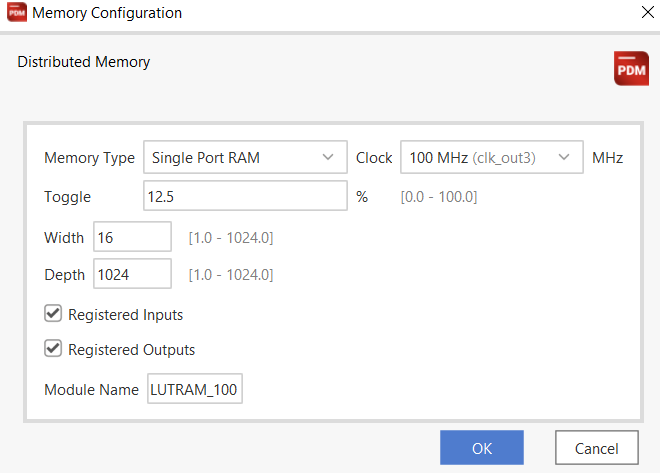

Logic部分用于评估CLB内资源的功耗,包括LUT(查找表)和FF(触发器)。对于LUT,PDM分为三类处理:组合逻辑、移位寄存器和分布式RAM(后两者针对SLICEM中的LUT)。如果仅仅知道分布式RAM的大小(深度和宽度),可借助下图中的红色方框准确得出所消耗LUTRAM的个数。

具体使用时,建议将这三种LUT分开填写,这样可以清楚地看到每类LUT的功耗,同时对于不同时钟域下的LUT也要分开写,如下图所示。

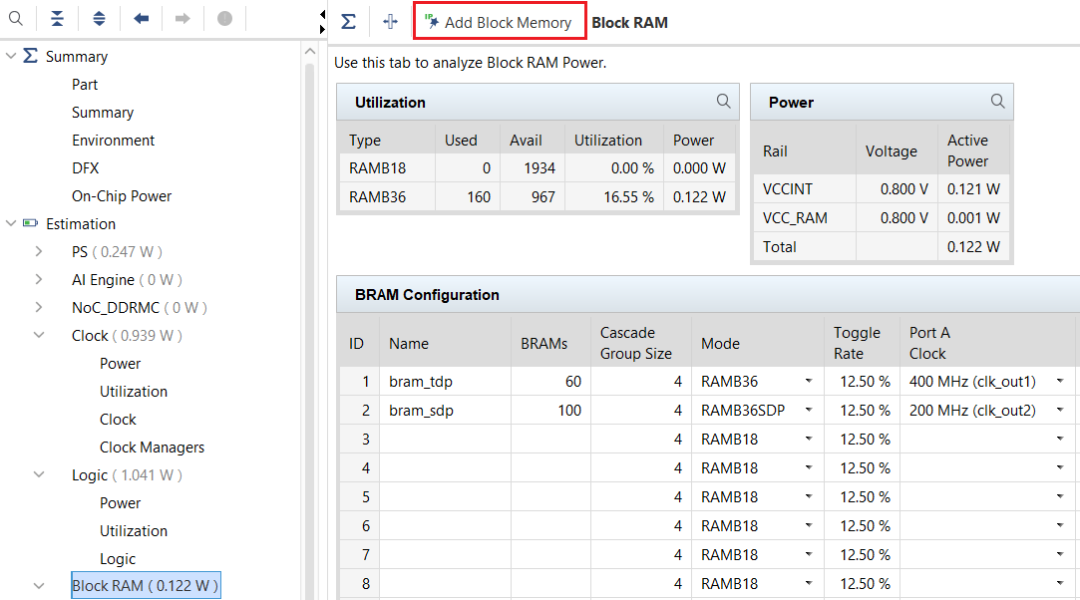

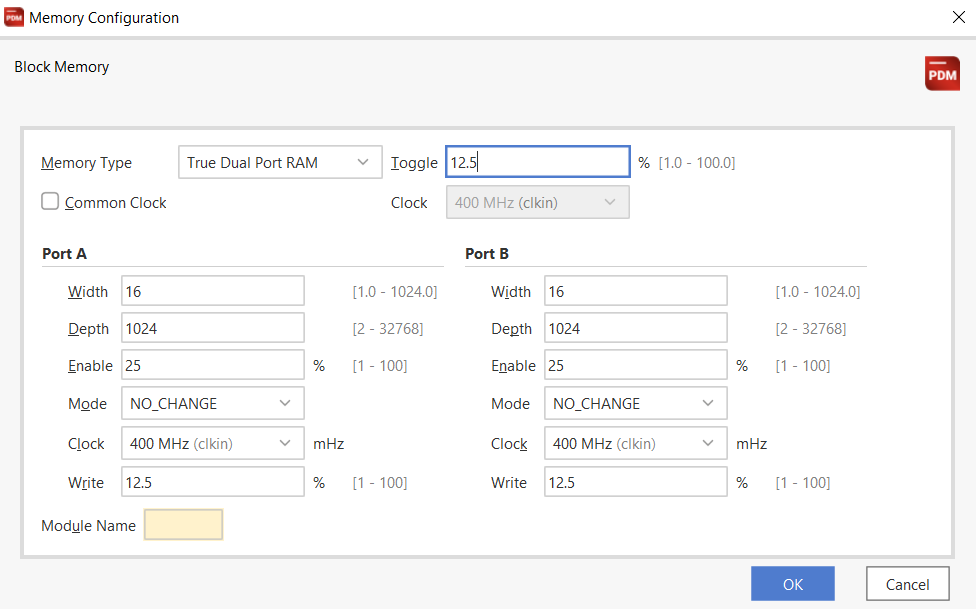

对于Block RAM,选中BlockRAM之后,。会显示Add Block Memory选项,如下图中的红色方框所示。可借助此选项更准确地得出BRAM的功耗。

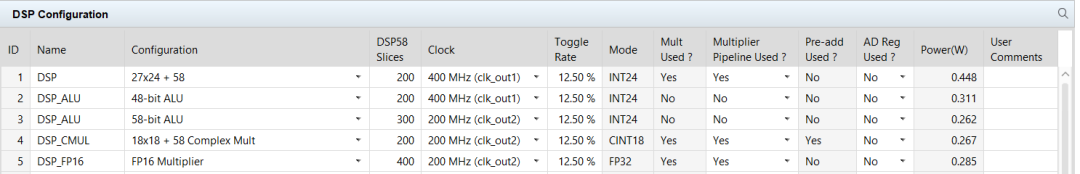

对于DSP,PDM提供了详细的设置界面,如下图所示。在这个界面上,可以填写DSP的工作模式、时钟频率、是否使用了乘法器等。

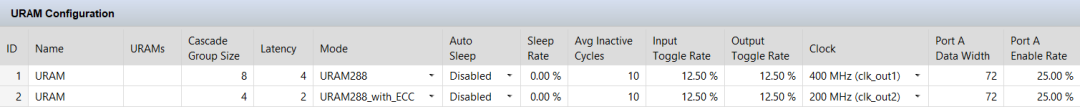

对于URAM,可进行级联个数设置、Latency设置、工作模式设置、工作频率设置等,如下图所示。

此外,我们还可以进行其他部分的功耗评估,如PS、AIE、NoC、DDR控制器等硬核。

审核编辑 :李倩

-

国芯科技近日成功推出了新一代指纹芯片CCM41012024-04-10 3538

-

Cadence推出全新一代AI IP和软件工具2023-09-20 2485

-

STM32U599平衡图显性能与功耗的新一代产品2023-09-05 581

-

如何简化从 XPE 向 PDM 的迁移2022-11-03 1529

-

德州仪器(TI)推出新一代KeyStone II架构2021-05-19 2562

-

新一代纳秒级高带宽仿真工具平台HAC Express的优势2021-01-11 1046

-

谷歌正式推出了新一代安卓系统“安卓10”,亮点功能不少2019-09-04 5346

-

FPGA与DSP竞争新一代基站设施2019-07-19 2034

-

Xilinx推出新一代系统级设计存储器解决方案UltraRAM2017-02-08 1668

-

Xilinx推出Smarter无线电解决方案 可满足新一代LTE与多载波GSM平台性能需求2014-02-21 1033

-

ST助力NTT Plala推出先进新一代智能IPTV机顶盒2013-09-22 4059

-

面向新一代多核器件的电源管理技术2013-04-03 13822

-

Xilinx发布新一代Smarter Networks和数据中心解决方案2013-03-06 1334

-

Xilinx Kintex-7:业界推出最快的28nm新一代可编程逻辑器件2011-03-28 4516

全部0条评论

快来发表一下你的评论吧 !