FPGA在电光/红外系统中平衡架构、IP和功耗

描述

作者:DR. TIBOR KOZEK,JUJU JOYCE,SUHEL DHANANI

现代电光/红外(EO/IR)系统变得越来越复杂,因此需要FPGA最好提供的处理能力。这些系统中最关键的设计挑战是将高性能传感器/视频处理与低功耗相结合。为了帮助解决这一难题,本文介绍了关键的传感器处理和视频处理算法,以及如何在FPGA上实现它们。

便携性和多功能性,加上领先的 COTS 技术,是许多现代航空航天和国防 (A&D) 传感器平台的特征。无论是安装在无人机系统(UAS)、人包上,还是作为自主传感器留下来,光电/红外(EO/IR)系统都变得极其复杂,需要FPGA提供的最好处理能力。由于低尺寸平台中的可用能量和散热,功率限制也收紧了。

这些军用成像系统变得越来越复杂,并集成了多个先进的传感器 - 从热红外到可见光谱,甚至紫外焦平面。不仅这些传感器输出必须全部校正(有缺陷的像素校正和颜色校正)并进行插值,而且来自多个传感器的图像必须融合,覆盖和进一步处理,以便在战场上进行本地显示和/或传输。这些系统的关键设计挑战是将高性能传感器/视频处理与低功耗相结合。以下讨论重点介绍一些关键的传感器处理和视频处理算法,以及如何在FPGA上实现这些算法。由于基于 FPGA 的设计减少了元件数量,同时增加了灵活性,因此降低了系统功耗。

典型传感器处理系统

FPGA 是几乎所有最先进的 EO/IR 系统的首选平台,因为它们满足了可编程性、高性能传感器/视频处理和低功耗的要求。

事实上,每一代新一代低功耗 FPGA 的特性都通过结合使用架构增强功能和更低的内核电压,以及硅特征尺寸缩小带来的几何优势,显著降低了静态和动态功耗。

传感器处理

EO/IR系统中使用的图像传感器的输出需要使用算法进行校正,例如用于非均匀性校正和像素替换的算法。虽然这些算法通常只需要每个像素进行一些数学运算,但需要以像素速率进行计算,并且每个像素的数据可能不同。在这种情况下,FPGA是一个理想的平台,因为架构中固有的并行性,以及算法IP的现成可用性,以实现视频处理功能。

对于非均匀性校正,需要将像素特定系数流式传输到实现校正公式的逻辑块中。对于较小的传感器,这些系数可以存储在内部FPGA存储器中。根据传感器的分辨率和系数的精度,内存要求会有所不同。对于较大的传感器,这些数据需要缓冲在外部存储器中,并与每个视频帧的像素流同步读出。在任何一种情况下,通常都需要根据一些选定的参数(例如焦点阵列(FPA)温度)来更改校正数据集,该温度从地面到高度变化很大。

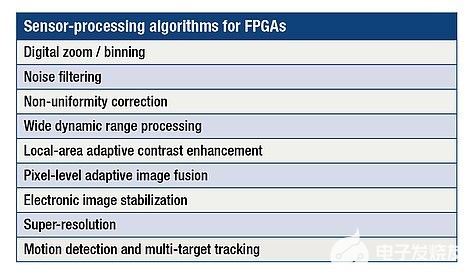

这种算法的典型数据流将双重缓冲校正系数,以允许来自闪存的相对较慢的数据流在应用新数据集之前完成。FPGA的主要优势之一是能够创建适合算法的数据路径,而不是改变算法以适应预定义的架构。这对于实现低功耗至关重要。FPGA中的海量I/O和大量逻辑元件允许轻松实现并行性,现成的IP算法有助于简化设计。表1显示了一些可用于FPGA的更典型的传感器处理算法,例如Altera的Cyclone系列中的算法。

表 1:适用于 FPGA 器件的典型传感器处理算法,如阿尔特拉的旋风系列。

FPGA降低EO/IR传感器系统功耗的另一种方法是大幅降低占位面积。例如,图1显示了一个基于Altera Cyclone FPGA的系统,该系统实现了具有集成处理功能的热传感器。FPGA 可执行实时图像增强、图像稳定和数字增强分辨率,还可以驱动集成的微显示器。在这种情况下,FPGA功耗约为500 mW。

图 1:集成图像处理的热传感器系统。

视频处理:混合和缩放

军用EO/IR系统通常包括多个图像传感器,其输出必须融合在一起并显示在具有非标准分辨率的自定义显示器上。(“非标准”意味着分辨率不同于典型的台式机或笔记本电脑LCD。视频处理系统可用于在自定义显示器上从两个视频源生成复合图像。FPGA内部的视频数据路径可以从多个源生成复合图像。

输入视频首先格式化为所需的色彩空间,然后与多个其他视频流进行缩放(调整大小)和混合(alpha混合)。缩放和混合是最常用的视频功能之一,可以使用FPGA可用的现成IP算法来实现。

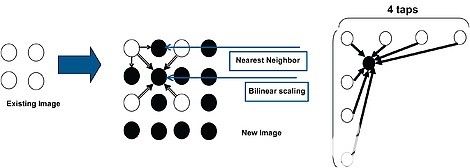

缩放可以像复制(或删除)前一个像素一样简单,也可以使用复杂的插值过滤技术来实现以生成新像素。图 2 显示了可用于缩放的不同算法之间的差异。

图 2:不同的视频缩放算法及其在视频缩放IP中的实现

该图说明了所有生成的像素(以纯黑色显示)与所有原始像素(以白色显示)。有许多方法可以生成纯黑色像素;例如,最近邻算法复制前面的像素。更复杂的方法是取垂直和水平维度的两个相邻像素的平均值。有时这被称为双线性缩放 - 双线性,因为它使用大小为2x2的像素数组来计算单个像素的值。

进一步了解这一概念,可以通过在水平维度中使用“m”像素和在垂直维度中使用“n”像素来计算新像素。图 2 还显示了如何使用每个维度中的四个像素生成像素(也称为四抽头缩放引擎)。

当然,这个技巧涉及分配给每个像素的权重 - 在通过算法实现时也称为系数。系数将决定缩放图像的质量。

图 2 描述了一个可用于交替旋风 FPGA 的此类扩展 IP 核。此功能预集成了各种“Lanczos”过滤器功能。Lanczos 多元插值方法用于计算任何数字采样数据的新值。当用于缩放数字图像时,Lanczos 函数指示原始图像中的哪些像素和比例组成最终图像的每个像素。

也可以从一系列Lanczos算法中进行选择以缩放图像或完全绕过它们以支持自定义系数。在任何一种情况下,该函数都会自动执行为本质上是二维滤波器的HDL代码生成繁琐的工作。它还将其映射到各种FPGA结构,如DSP模块和嵌入式存储器模块,从而提高生产率并缩短整体设计时间。

视频叠加

另一个常用的功能是混合和覆盖两个或多个视频流。这通常由 alpha 混合函数完成。这是一种从两个或多个像素生成复合像素的方法。为一个像素分配一个称为 alpha 的不透明度值。当 Alpha 为零时,该像素是完全透明的(即:不显示)。当相同的 Alpha 值为 1 时,像素是完全不透明的 – 只能看到该像素,而不显示另一个像素。

在数学术语中,复合像素的值计算如下:

C = αP1 + (1-α)P2

哪里

α是阿尔法值

P1 是视频层 1 中的像素 1

P2 是视频层 2 中的像素 2

C 是复合像素

可以使用相同的技术来创建半透明图像,因为 alpha 值可以设置在 0 到 1 之间的任何位置。

组合来自两个(或更多)图像的信息的一种更复杂的方法是利用图像融合算法。想象一下,一个热红外传感器和一个可见光图像传感器描绘了同一个场景,但每个传感器都包含图像不同部分的信息。

如果可以应用 Alpha 混合来选择一个图像或另一个图像在组合输出中的主导地位,那么 alpha 就没有一个单一的值可以从传感器中提取所有可用的信息。

左上角的可见图像包含有关周围环境的信息,而右侧的热视图仅显示背景温差的可识别特征。相反,热传感器的性能不受场景中强光源的影响,而可见光摄像机则由于饱和而在同一区域内不提供任何信息。

在融合视图中,来自两种输入模式的信息的无缝组合是逐个像素实现的。一种模式中缺少的细节从另一种模式中“填写”,反之亦然。最简单的融合形式之一是对根据局部图像统计数据计算的每个像素应用具有不同 Alpha 值的 alpha 混合。然而,最先进的融合算法通常不止于此,并对输入图像进行分解,从而提取每个像素周围的相关特征。然后将这些特征组合在一起形成融合图像。

审核编辑:郭婷

-

ISPl362在基于FPGA的红外成像系统中的应用2012-08-12 2311

-

FPGA低功耗设计小贴士2015-02-09 3002

-

FPGA系统功耗瓶颈的突破2018-10-23 3013

-

FPGA架构和应用基础知识2018-12-14 2926

-

SoC FPGA的电机控制IP模块和经过验证参考设计2019-06-24 3372

-

如何利用28nm高端FPGA实现功耗和性能的平衡?2019-09-17 2922

-

【MPS电源评估板试用申请】基于FPGA的红外热成像系统2020-06-18 1745

-

DSP+FPGA+ASIC设计的实时红外图像处理系统2010-07-22 1334

-

FPGA架构的功耗及影响功耗的用户选择方案2010-08-27 2235

-

W5100在FPGA系统中实现TCP_IP网络通信2012-04-24 2973

-

基于SoPC系统的红外解码IP核的设计与实现方法研究2012-11-30 8198

-

28nm高端FPGA如何实现功耗和性能的平衡?2013-05-17 4102

-

基于FPGA的多功能红外图像源系统设计2016-08-30 533

-

基于FPGA技术的红外实时采集系统设计2017-11-24 3271

-

如何使用FPGA实现多功能红外图像源系统的设计2021-01-26 1042

全部0条评论

快来发表一下你的评论吧 !