缓解并联DC-DC转换器阵列中不需要的输入拍频

描述

当一系列开关DC-DC转换器并联以获得更高的功率输出时,工作频率的差异会导致公共输入总线上出现不需要的拍频。结果是转换器输入部分循环的交流纹波电流意外增加。通过使用简单的输入滤波,可以显著降低交流输入纹波电流。具有较高基波开关频率(》1 MHz)的DC-DC转换器允许使用较小的滤波元件,适合整体空间和重量非常宝贵的系统。

虽然单个DC-DC转换器通常是一种更可取的解决方案,但在许多情况下,需要两个或多个转换器来满足军用系统的功率容量要求。在此类应用中,可以并联连接两个或多个DC-DC转换器阵列以产生所需的功率 - 并且在应用需要鲁棒性,容错或N + 1冗余电源的其他情况下,使用N + 1冗余电源来满足容量要求。

在电源故障可能是灾难性的关键军事应用中,容错电源使用N+ 1类似的转换器来提供非常高的可靠性。通过冗余,容错系统确保在转换器发生故障时,至少比承载负载所需的最小模块多一个模块。

如果阵列中的DC-DC转换器采用相同的馈电供电工作,则它们通常并置以获得共享热和屏蔽功能的优势,同时节省空间。虽然这些转换器可能属于同一类型,但除非所选的DC-DC转换器允许同步,否则会发生开关频率不匹配。

由于在相同输入总线电压下并联运行的非同步DC-DC转换器存在细微变化或不匹配,因此这些转换器的工作频率存在很小的差异。转换器工作频率的这种差异导致阵列输入电流中存在不需要的拍频。结果,在转换器的输入部分循环的交流纹波电流增加。虽然提供同步方法的转换器确实避免了拍频,因为没有工作频率不匹配,但选择现成的转换器的选择受到限制,这可能导致整体系统效率和功率密度降低。通过实现简单的输入滤波器,可以轻松显著抑制一系列非同步转换器的输入纹波电流以及拍频分量,从而可以考虑非同步转换器。

DC-DC 转换器并联阵列中的拍频

为了演示这个问题以及输入滤波的影响,让我们来看看需要大量功率的军用电源系统,例如RF发射器或微波无线电链路。例如,需要MIL-STD-704E电源输出功率为2.1 kW的系统并联连接八个270 W总线转换器,以形成高功率DC-DC阵列。为简单起见,将使用缩小版本(两个并联的高输入电压 270 W 正弦波幅总线转换器阵列,总输出功率为 540 W)进行测量(图 1)。

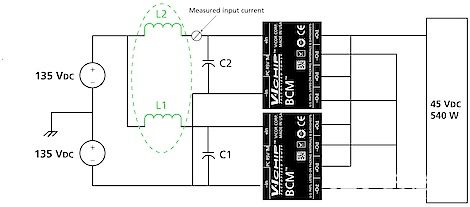

图 1:由两个高输入电压 270 W DC-DC 转换器组成的阵列,与随后的输入滤波电感器 L1 和 L2 并联,以绿色显示。

(单击图形可缩放 1.9 倍)

尽管正弦波幅度总线转换器以固定的多MHz频率开关,但该系列成员的器件间差异会导致阵列中的每个转换器以略微不同的开关频率工作。阵列中每个DC-DC转换器的开关噪声之间的相互作用会产生不需要的拍频,其倍数是转换器工作频率之间差异的倍数。

不需要的拍频的影响在阵列的DC-DC转换器之间循环的纹波电流中最为明显。开关频率的纹波电流加起来,对转换器的整体纹波电流包络产生幅度调制。例如,在前面描述的并联DC-DC转换器阵列和图1所示的测试设置中,一对标称开关频率为1.7 MHz的互连总线转换器可能具有f1= 1700 kHz和f2 = 1702.7 kHz的实际开关频率。两者之间的2.7 kHz差值意味着总输入电流对视在纹波的频率分量要低得多。

在纹波幅度最高的时间内,所讨论的两个转换器之间的互连布线中的铜损高于其需要:直流DC未使用循环交流纹波电流,但它仍然流过具有有限电阻的导体。高附加纹波电流也会对输入旁路电容器施加压力,并且系统噪声可能会增加,具体取决于电路板布局。在某些情况下,这些环流会建设性地干扰足够的振幅,从而导致转换器本身的不可预测行为,例如,错误地检测到模块内的过流情况。

为了实际证明输入纹波电流增加和产生低拍频分量的问题,一对高压270 W BCM总线转换器作为一个简单的并联阵列连接,如图2所示。对于初始测量,输入电感L1和L2不包括在内,并且除了输入旁路电容C1和C2之外没有输入滤波。由于阵列中两个模块的异步切换,交流输入纹波电流频率也不同。在公共输入且无电感滤波的情况下,交流纹波电流混合并产生基于较低拍频的调制幅度的纹波,如前所述。

该阵列由两个工作在 270 VIN 和 45 VOUT 的总线转换器构成。该转换器型号的标称基波工作频率为1.7 MHz,同样,图1所示的滤波电感不在电路中。测量了其中一个模块的输入纹波电流,如图1所示。所得到的性能的时域图如图2(a)所示。对于本测量中使用的总线转换器阵列,满载工作时的总输入电流约为2.1 ADC。

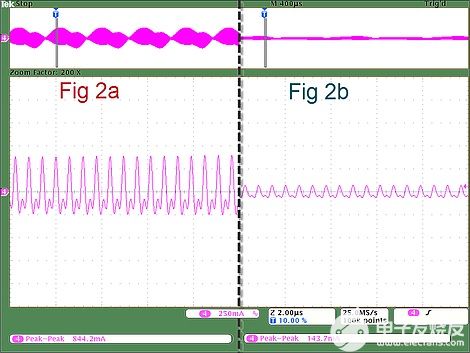

图 2:时域示波器图(2a)显示,没有滤波电感器的纹波电流很高(峰峰值为844 mA)。图(2b)显示,使用滤波电感时纹波电流大幅降低(峰峰值为143 mA)。

(单击图形可缩放 1.9 倍)

抑制节拍

通过相当简单的输入滤波,可以很容易地控制阵列中非同步转换器之间循环的不需要的交流纹波电流。输入电感器(图1中标记为L1和L2)用作附加输入滤波器。在该实验装置中,电感为0.4 μH,并与阵列中每个总线转换器的+In支路串联。输入电感器在开关频率下增加一个转换器的输入级与阵列中其他转换器之间的阻抗。在这种情况下,在总线转换器的1.7 MHz基波开关频率下,电感器的阻抗约为4 Ω。这种阻抗降低了系统中的高频交流环流。

添加输入电感后的性能如图2(b)所示。

整体纹波幅度显著减小,纹波电流包络的较低频率调制也相应减小。因此,使用输入滤波电感器时,输入纹波电流的幅度从844 mA峰峰值降至143 mA峰峰值以下。

因此,观察到,如果在该并联转换器阵列的公共输入总线上不使用滤波,则非同步DC-DC转换器阵列输入端的循环交流纹波电流可能会高得多。事实上,与直流输入电流相比,交流纹波电流可能很大。然而,通过使用简单的输入滤波,可以显著降低交流输入纹波。由于本例中使用的V•IChip转换器工作在较高的基波开关频率(》1 MHz),因此与较低开关频率转换器所需的滤波元件相比,采用了具有较低损耗的较小滤波元件。这对于整体空间、重量和效率都非常宝贵的系统来说是有利的。

输入滤波可抑制交流输入纹波电流

从图2所示的结果可以看出,输入滤波在显著抑制并联开关DC-DC转换器阵列中拍频的影响方面发挥着重要作用。使用简单的输入滤波电感器可以看出,其中一个总线转换器模块(在两个高输入电压270 W DC-DC总线转换器的阵列中)的交流输入纹波电流的幅度降低了80%以上。

审核编辑:郭婷

-

DC-DC转换器电路图 Boost升压型DC-DC转换器的工作原理2023-09-19 5882

-

MAX8515并联稳压器在DC-DC转换器的输出应用中的应用2023-03-30 3075

-

DC-DC转换器的相关资料分享2021-12-28 2785

-

双向DC-DC转换器的设计与分析2021-11-20 5287

-

DC-DC转换器和AC-DC转换器的区别及功能2021-11-17 7263

-

什么是DC-DC转换器?DC-DC转换器是如何命名的?2021-11-09 5389

-

DC-DC转换器原理2021-09-15 3585

-

正激式和反激式DC-DC转换器介绍2020-12-09 4479

-

利用全型、小型及微型系列DC-DC 转换器设计高功率阵列2016-05-24 787

-

使用Maxi、Mini和Mincro系列DC-DC转换器设计大功率阵列2016-01-06 1112

-

DC-DC转换器2010-03-09 4187

全部0条评论

快来发表一下你的评论吧 !