microblaze之Video Processing Subsystem调试误区

描述

内容:总结video processing subsystem调试中遇到的问题,以及在解决问题中的思路方法论,引为前车之鉴。

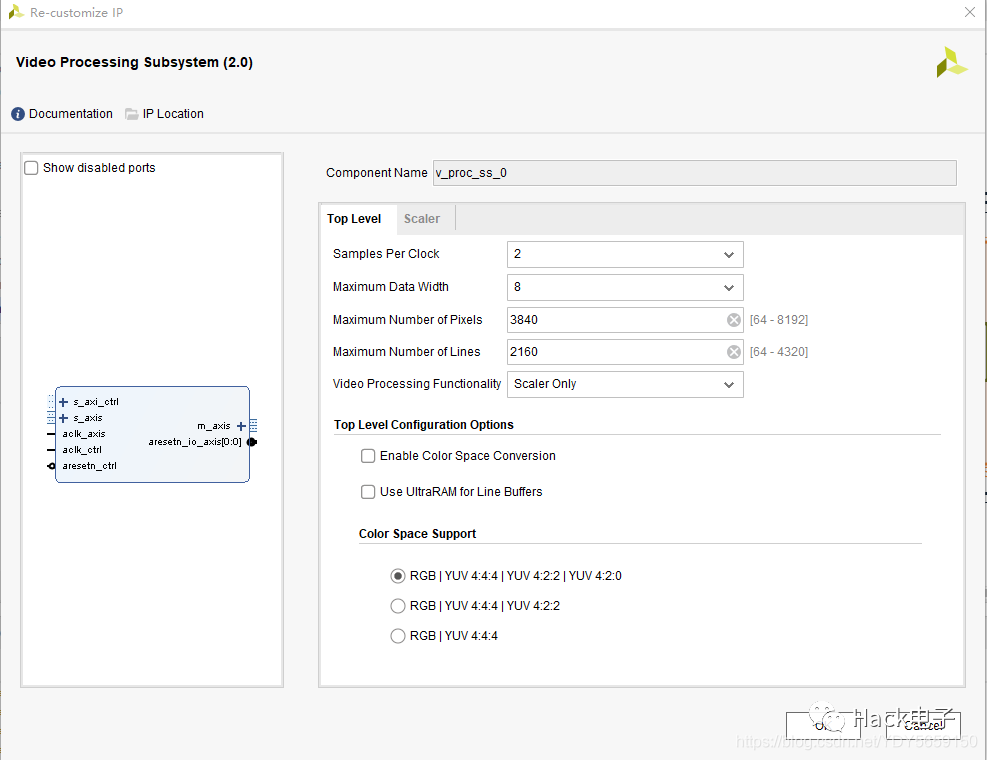

1,我的目的是希望采用vps中的scaler模块对图像进行拉伸缩小。IP的配置如下:

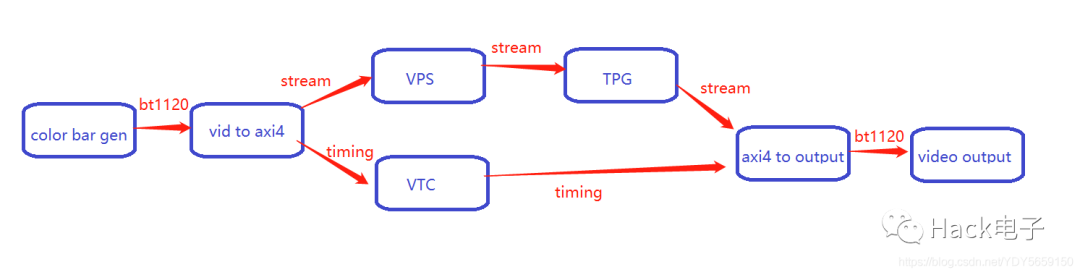

2,整个系统的框架图如下,仅比上期的内容增加了scaler模块,如下:

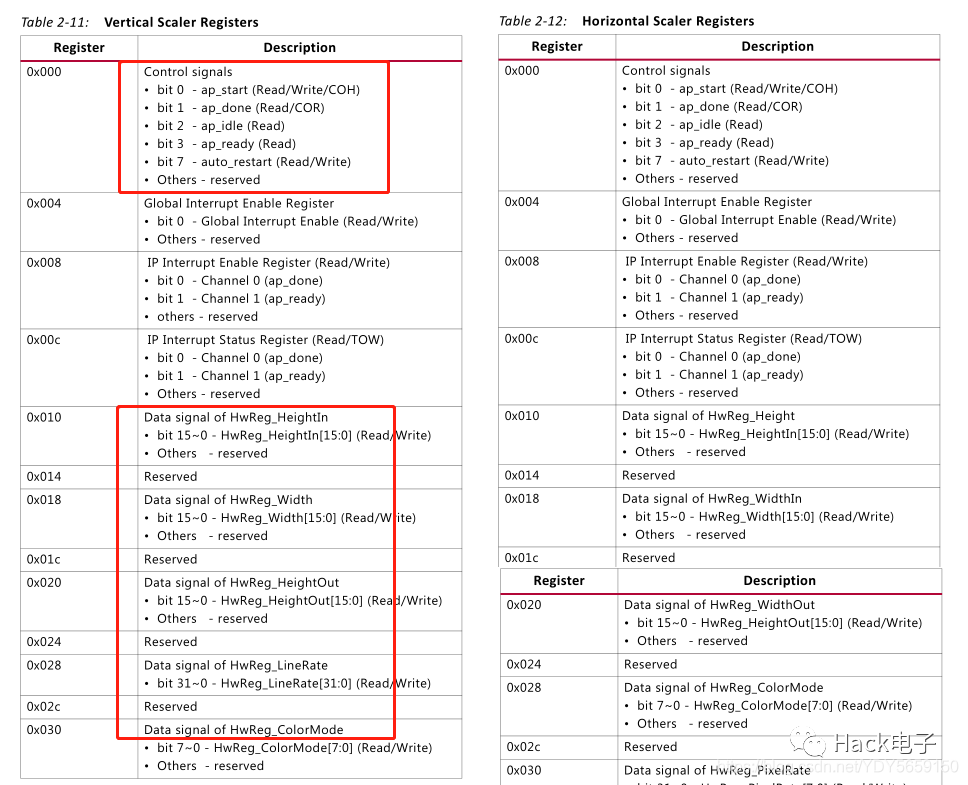

3,查手册,可以知道这个scaler only组件分成了hscale,vscale和GPIO,其中GPIO是控制上下游stream流控设备复位用,暂时忽略。hscale和vscale的寄存器空间如下,主要关注图像的大小,以及缩放比率:

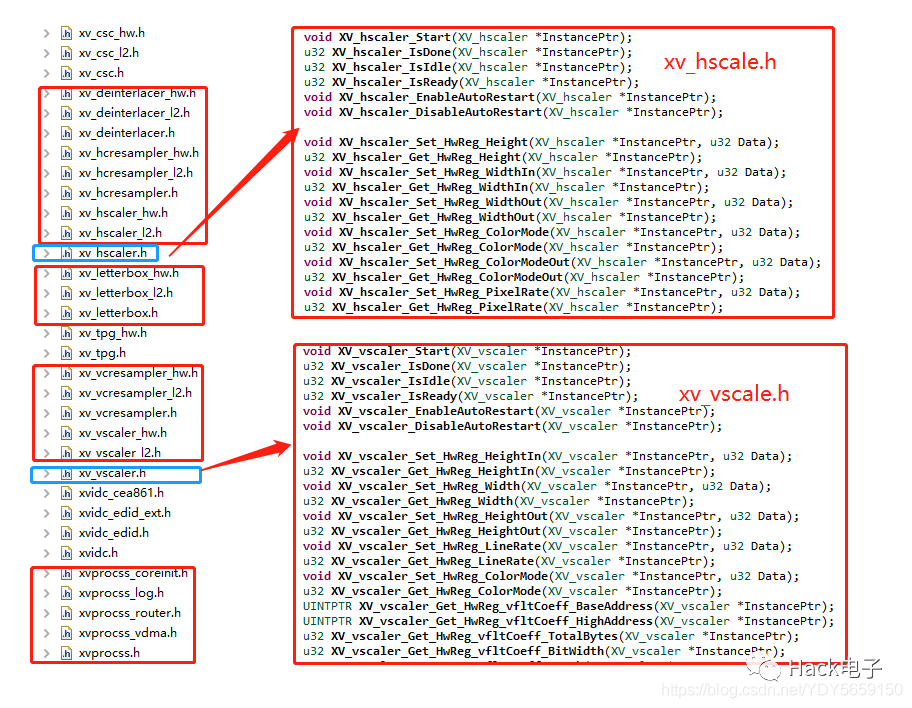

4,vivado中的工程综合完毕之后,进入SDK之中,可以看到xv_hscale.h和xv_vscale.h,文件内部包含了控制这个scale模块的函数。虽然使用的是scaler only模式,但是系统自动生成了所有的IP文件,例如deinterlace,csc等,因为这里指需要使用scale,因此直接操控xv_hscale和xv_vscale或许更简单。

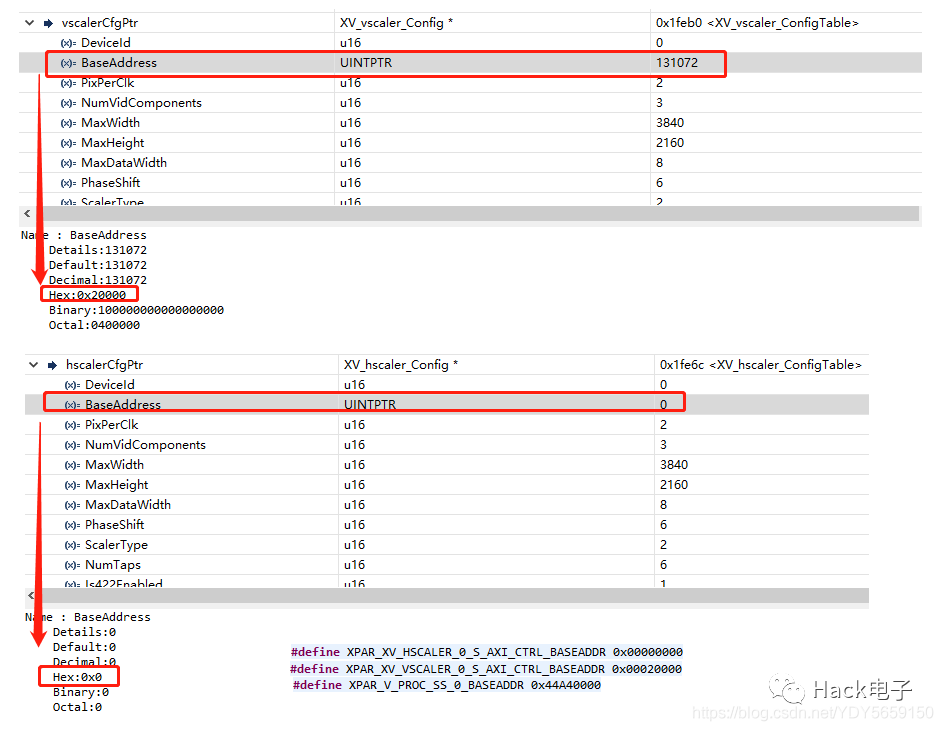

5,在SDK内部编写控制代码,下载之后输出没有图像,添加打印之后发现hscale初始化失败,而vscale初始化成功,对比了hscale和vscale的驱动代码后,发现是完全一致的,于是没有明白原因何在,如下:

6,在SDK中采用debug单步调试,于是发现了问题所在,原来hscale传递的基地址参数为0x00,这是一个非法的地址。但是想一想就知道这是系统自动生成的驱动文件,不应该出现这种低级的错误才对。于是去查看系统设备描述文件xparameters.h,发现hscale的地址确实是0x000000,vscale的地址是0x20000,而vps的基地是0x44A40000。

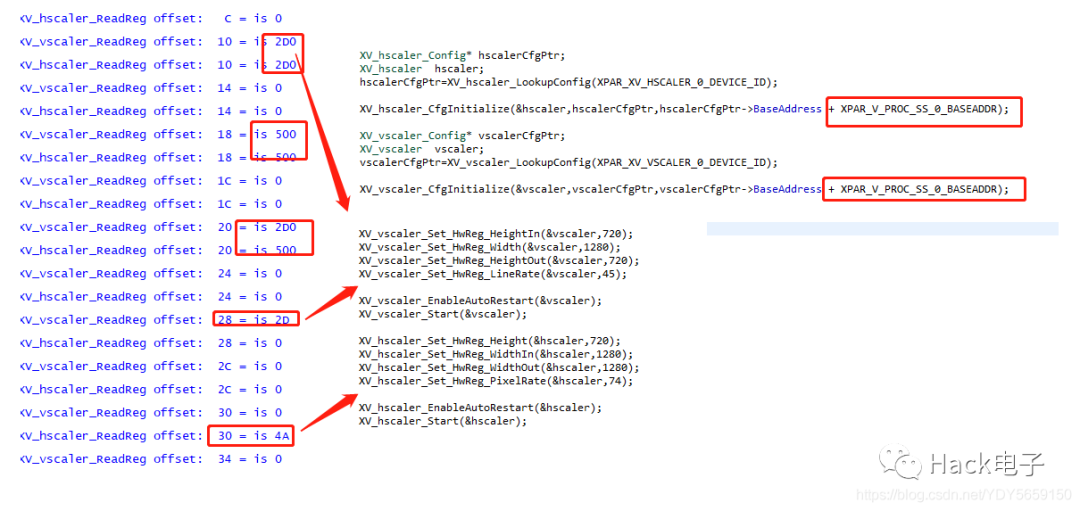

7,后面怀疑过自己的工程创建是否有误,以及创建IP过程中可否允许编辑起始地址,但结果根本无法编辑,工程也确认无误。后来想到应该是hscale和vscale的基地址仅仅是整个IP的偏移地址而已,在初始化的时候应该加上IP的首地址,于是做如下更改,并设置好图像的宽高,但是line rate和pixel rate却不知道填写多少,写一个45和74吧,因为我的图像是720P60,水平同比是45Khz,像素时钟是74.25,结果当然还是没有图像输出,原因是这个两个值是错误的。同时把寄存器读出来之后可以知道所有的数据是配置了的,那么原因就是某些数据是错误的。

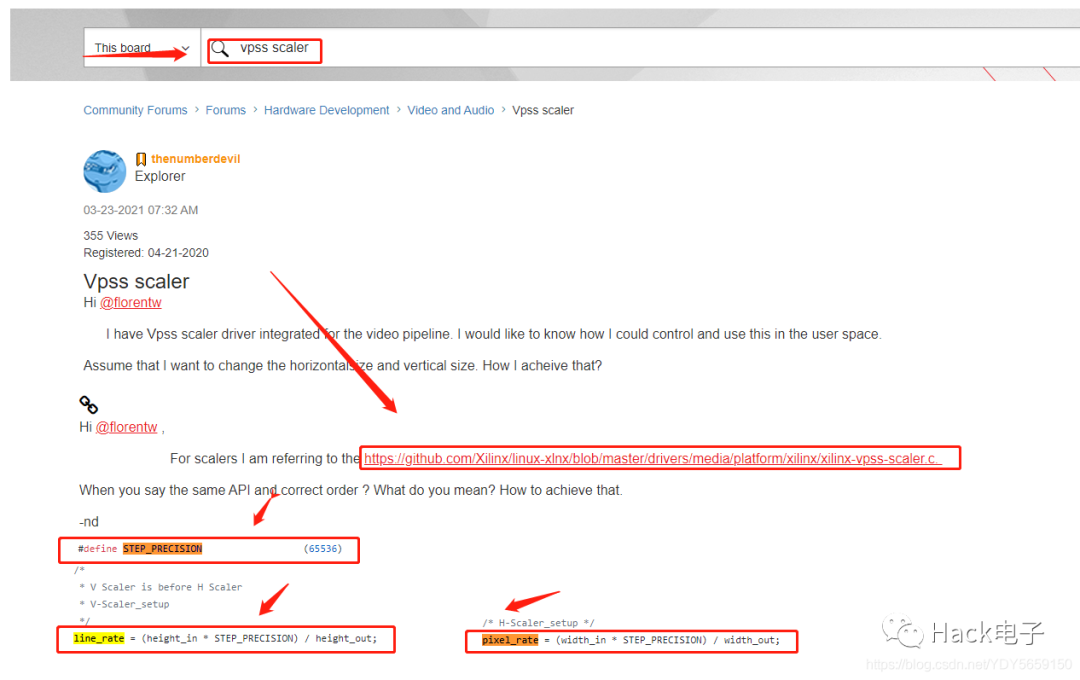

8,想到上次调试TPG模块的时候,图像的宽度需要除以2,进而也尝试之后仍然不对。于是去xilinx论坛社区找一下有无相同的问题。搜索vpss scaler后浏览,发现有人在gitup里面上传有scale的代码,于是点击后大致浏览一遍,发现了line rate和pixel rate 的计算公式:

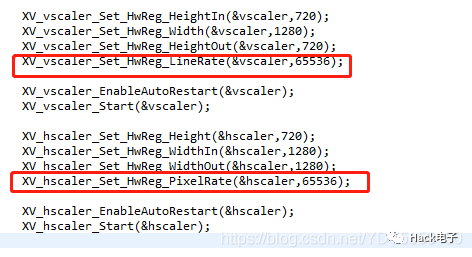

9,有这个发现之后,因为我的输入和输出的宽度和高度是一样的,因此line rate 和pixel rate应该设置为65536。现在终于知道了这两个参数指的意思分别是纵向和横向的缩放比率。

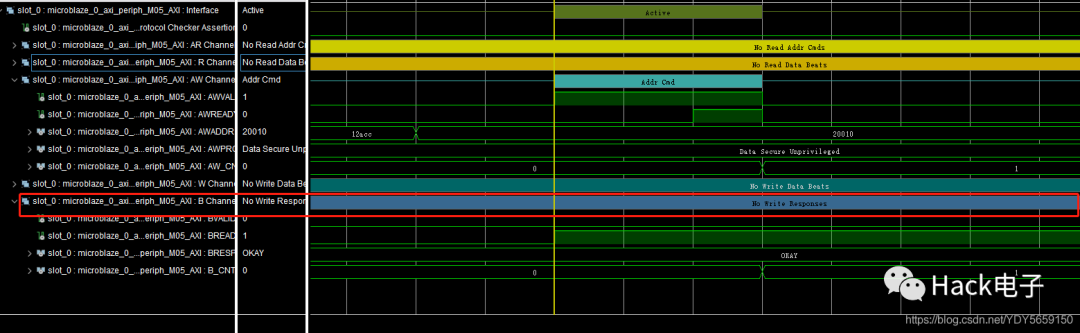

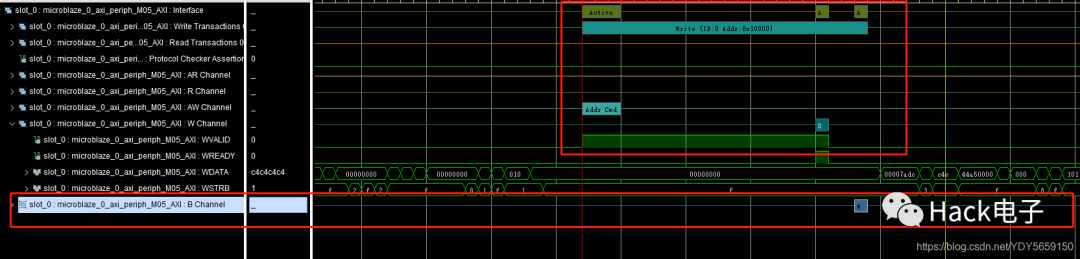

10,原本以为可以出图了,实际上还是没有出图,让人没想到的是程序只要执行scaler_set_HwReg的任何函数,程序立马就跑飞了。然后重新烧录bit文件,重新运行elf文件,还是一样的结果。这个时候我把Block design中的debug信号全部去掉,同时把AXI系统时钟由150M改为100M,最终的结果还是会跑飞。这时候我想软件上面没有改动的余地了,于是想知道VPS这个IP的AXI总线是处于什么状态,当我执行这些函数的时候。于是仅把AXI总线信号加入debug模块,触发运行后得到如下的结果,情况是VPS没有应答,因此CPU直接挂掉了。

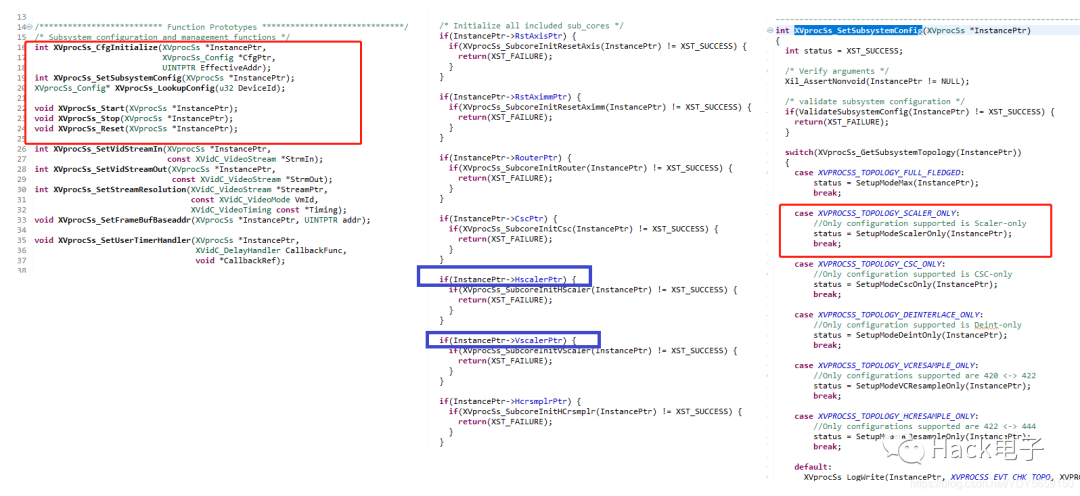

11,这个时候差点快绝望了,于是放弃直接控制h_scale和v_scale的方式,改用控制最上层的vps,谁知道xilinx需要做什么骚操作。首先看一下xvprocss.h文件信息,里面定义各种操作的函数,初始化函数中依据所定义的子IP,SetSubsystemConfig函数有选择性的进行配置。

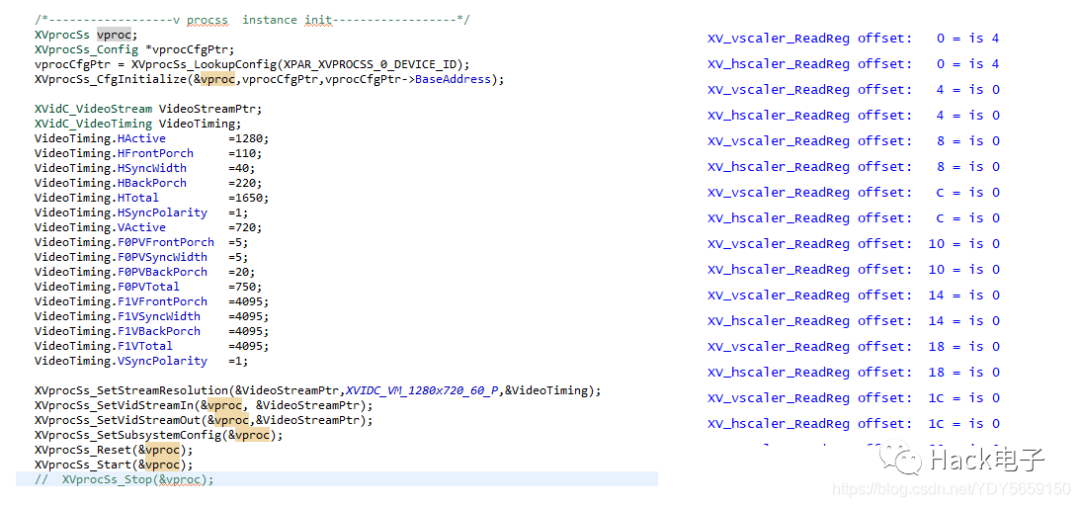

12,然后仔细的看了一遍函数中的数据结构定义,于是重新编写了控制程序,这时候想应该有图输出了吧,然而还是没有图输出。并且把里面的寄存器读出来之后,发现除了最开始0x00寄存器空间之外,其他数据全部是0,确实很意外。

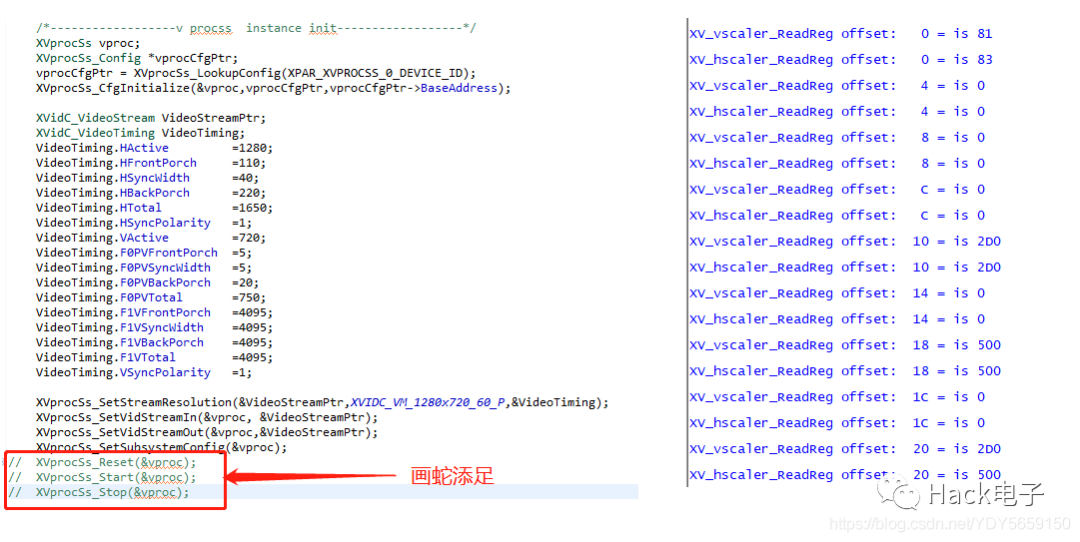

13,到了这个时候,确实没有招了,于是来回的改来改去,无意中多注释了两行代码,结果出图了,同时监控AXI总线上的数据,也有应答了。原来是我在配置完成之后,又把这个IP软复位了。因此其余的数据全部变成了0。印证了陆游的那句话,山穷水复疑无路,柳暗花明又一村。

总结:

1,通过调试这个IP,对于软件编程有了更进一步的了解;

2,其实直接控制h_scale和v_scale应该可以达到同样的功能,只不过这个IP需要有特殊的配置顺序,以及各种复位逻辑,任何的差池都会导致没有图像输出;

3,目前还没有深入了解这个IP的控制流程,还需要深入底层去看实现的细节部分,比如实现deinterlace等其他功能。

审核编辑:汤梓红

- 相关推荐

- 热点推荐

- Video

- MicroBlaze

- Subsystem

-

MicroBlaze串口设计2023-08-02 2578

-

Video Processing Using FPGAs in Video Surveillance Systems2008-08-08 6803

-

ATSC Standard:AVC Video Transport Subsystem Characteristics2008-10-16 3945

-

如何理解DM8148的HD Video Coprocessor Subsystem和Media Controller Subsystem中的HDVICP22018-05-28 2254

-

怎么远程调试microblaze软件2019-02-27 1753

-

调试Microblaze应用程序出现处理器无法停止的错误2019-07-17 4389

-

SDK 16.2无法调试Microblaze2019-09-27 2356

-

VIDEO PROCESSING FOR DLPTM DIS2009-10-01 742

-

Video and Image Processing Up2009-11-24 670

-

HDMI_1.4_2.0_RX_Subsystem_IP介绍和基础debug建议2022-03-25 5753

-

Video Processing subsystem例程分析2022-10-28 3216

-

Video Processing Subsystem与HDMI示例设计2025-11-07 925

全部0条评论

快来发表一下你的评论吧 !