十进制计数器的工作原理

描述

二进制编码的十进制是一个串行数字计数器,可计数十位数字,它会为每个新的时钟输入重置。由于它可以通过10种独特的输出组合,因此也被称为“十进制(BCD)计数器”。十进制计数器可以计数0000、0001、0010、1000、1001、1010、1011、1110、1111、0000和0001等。

4位二进制计数器将跳过16(24)个输出中的任何六个输出而作为十进制计数器。有一些用于十进制计数器的IC,可以在电子电路中随时使用,例如74LS90,它是一种异步十进制计数器,其电路图如下图所示:

上图显示了使用JK触发器构建的十进制计数器。J输出和K输出连接到逻辑1,每个触发器的时钟输入连接到下一个触发器的输出,除了最后一个触发器。与非门的输出与所有触发器的清零输入“CLR”并联。此纹波计数器最多可计数16,即24。

工作原理

当十进制计数器处于REST状态时,计数等于0000,这是计数器周期的第一阶段。当将时钟信号输入连接到计数器电路时,电路将对二进制序列进行计数。第一个时钟脉冲可以使电路计数到9(1001),下一个时钟脉冲前进到计数10 (1010)。

然后端口X1和X3将为高电平。众所周知,对于高输入,与非门输出将是低的。与非门输出连接到CLR输入,因此它重置十进制计数器中的所有触发器级,这意味着计数9之后的脉冲将再次从计数0开始计数。

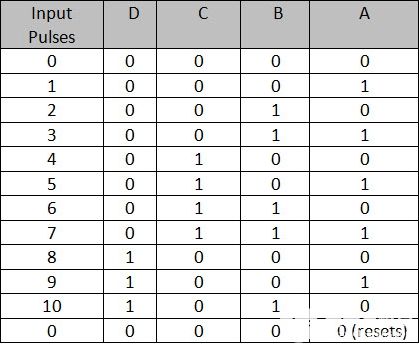

真值表

十进制计数器的真值表如下图所示:

上表描述了十进制计数器的计数操作,它表示输入脉冲的十进制计数的电路计数。当计数达到10 (1010) 时,与非门输出为零。计数由与非门X1和X3的输入解码。计数10后,逻辑门NAND将触发其输出从1到0,并重置所有触发器。

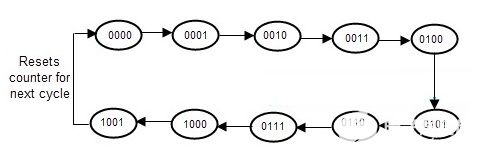

状态图

十进制计数器的状态图如下所示:

通过观察十进制计数器电路图,可以发现它有四个阶段,其中每个阶段都有一个触发器。因此它能够计算16位或16种潜在状态,其中仅使用了10个。计数从0000(0)到1001(9),然后与非门将复位电路。

多个计数器串联连接,可以计数到任何所需的数字。计数器电路可以计数的数字称为“Mod”或“Modulus”。如果计数器在计数n位后自行复位,则称为“Mod- n计数器”或“Modulo-n计数器”,其中n是整数。

Mod n计数器可以从0计算到2n-1。目前有几种类型的计数器可用,如Mod 4计数器、Mod 8计数器、Mod 16计数器和Mod 5计数器等。

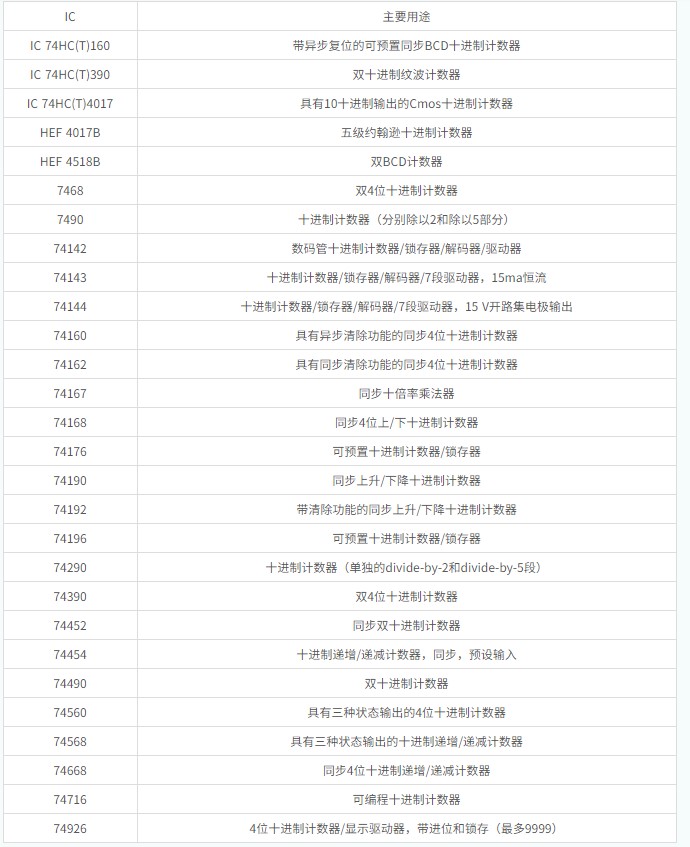

常用的十进制计数器IC

4017B和7049是设计十进制计数器最常用的IC,下面列出了用于十进制计数器的其它常用集成电路 (IC) 及其用途:

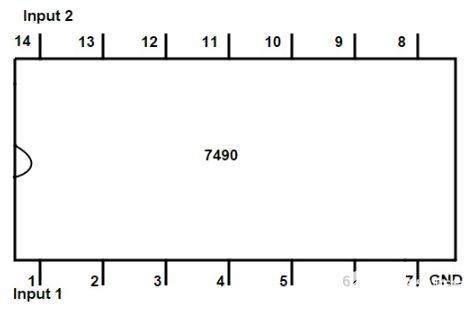

74LS90十进制计数器IC

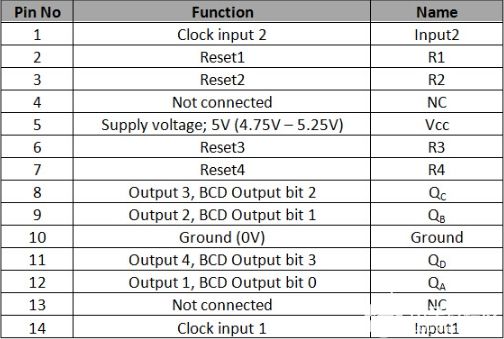

IC 74LS90是用来设计十进制计数器的最常用芯片之一,其符号如下:

引脚配置及说明如下:

工作过程如下:

74LS90是一个简单的计数器,可以从0到9计数。由于它是一个4位二进制十进制计数器,它有4个输出端口QA、QB、QC和QD。当计数达到10时,二进制输出每次复位为 0 (0000),另一个脉冲从引脚9开始。IC 7490的Mod通过更改RESET引脚R1、R2、R3、R4来进行设置。

如果R1和R2中的任何一个为高电平或R3和R4接地,计数器会将所有输出QA、QB、QC和QD重置为0。如果引脚R3和R4为高电平,则QA、QB、QC和QD上的计数为1001。

正如之前所说的,可以通过连接更多的IC n系列来增加十进制计数器的计数能力,例如可以用两个串联的7490 IC数到99。这款7490 IC内置了除以2和除以5的计数器。

74LS90还可以通过连接时钟输入2和QA,将所有剩余引脚连接到地,并将脉冲输入提供给1来用作除以10计数器。它可以通过在输入1处提供脉冲,将复位引脚R3和R4接地,并将QA与输入2连接来用作除以6计数器。

此外,7490 IC可以像双五进制计数器一样工作,用于以4位二进制数的形式存储十进制数字。

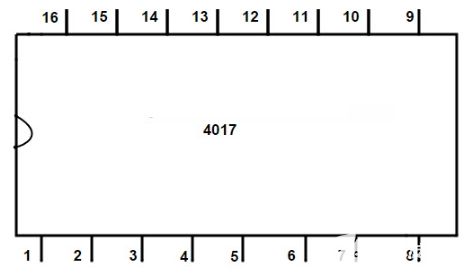

4017 CMOS十进制计数器

4017 CMOS十进制计数器IC符号如下:

引脚配置及说明如下:

频率计数中的十进制计数器

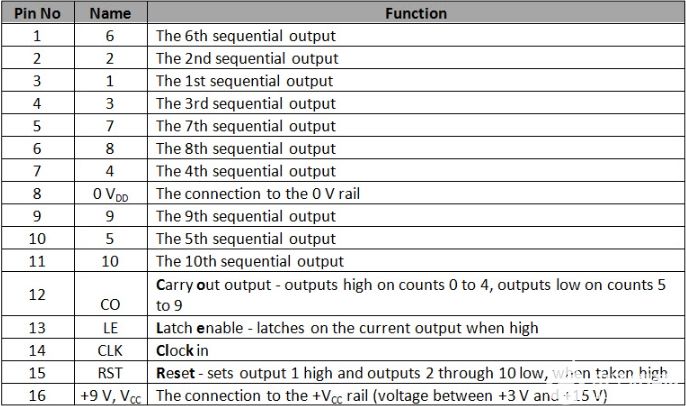

众所周知,二进制计数器可用于设计频率计数器。不过,在下图中,小编使用了十进制计数器(由JK触发器设计)给出频率计数器的电路设计图:

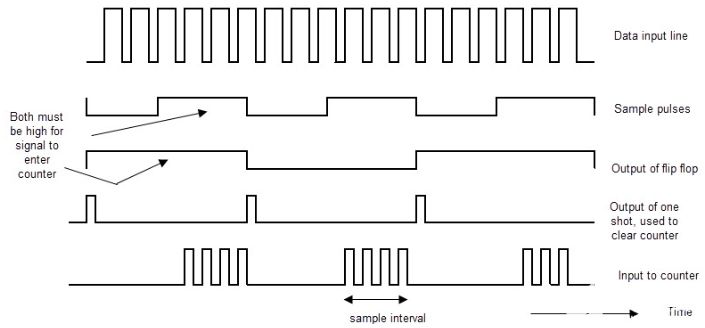

波段示意图:

为了计算未知计数器的频率,这里将未知频率馈送到一个输入端,并将采样脉冲馈送到与门的另一个输入端。当采样脉冲为高电平时,允许输入信号传送到计数器,否则不允许输入低电平采样脉冲。

未知信号的频率由计数除以采样时间间隔给出。与门的第三个输入由JK触发器给出,用于保存产生的输出或计数器的结果。当JK触发器的输入和采样脉冲均为高电平时,输出到达计数器。对于JK触发器的每个上升沿,计数器将由一个单次多谐振荡器通过向其发送一个脉冲来复位。

主要应用

十进制(BCD)计数器的主要优势和应用包括:

时钟生成

时钟分频

集成振荡器

低功耗CMOS

TTL兼容输入

应用在频率计数电路中

总结

众所周知,二进制计数器结构简单,但是读数不习惯,所以在有些场合采用十进制计数器较为方便。十进制计数器以二进制的形式来表示具体的十进制的数,可以计数0000、0001、0010、1000、1001、1010、1011、1110、1111、0000和0001等。在电子电路中,十进制计数器的应用领域非常的广泛。

-

十进制和4位二进制计数器数据表2024-05-31 701

-

双4位十进制和二进制计数器数据表2024-05-13 601

-

双十进制纹波计数器-74HC_HCT3902023-02-15 882

-

基于FPGA的十进制计数器2022-12-20 1138

-

CD4017十进制计数器的应用实验2022-05-11 1408

-

74ls160十进制计数器2018-01-18 266259

-

十进制计数器/分频器2017-04-06 4045

-

二五十进制计数器2016-03-22 1752

-

DIY十进制计数器2013-12-03 3768

-

4位十进制可逆计数器电路2010-12-10 7875

-

十进制计数器,十进制计数器原理是什么?2010-03-08 25808

-

8421码同步十进制递增计数器2009-09-24 7019

-

十进制计数器工作原理2008-01-21 30954

-

十进制计数器2007-06-20 5658

全部0条评论

快来发表一下你的评论吧 !