覆盖电子系统设计全环节的EDA技术的基础知识

描述

EDA 覆盖电子系统设计的全环节

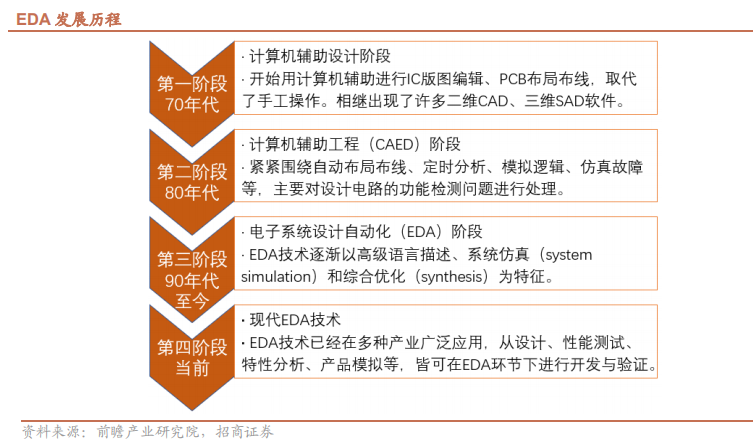

电子设计自动化(Electronic Design Automation,EDA)技术是指包括电路系统设计、系统仿真、设计综合、PCB版图设计和制版的一整套自动化流程。随着计算机、集成电路和电子设计技术的高速发展,EDA 技术历经计算机辅助设计(CAD)、计算机辅助制造(CAM)、计算机辅助制造(CAM)、计算机辅助测试(CAT)和计算机辅助工程设计(CAE)等发展历程,已经成为电子信息产业的支柱产业。

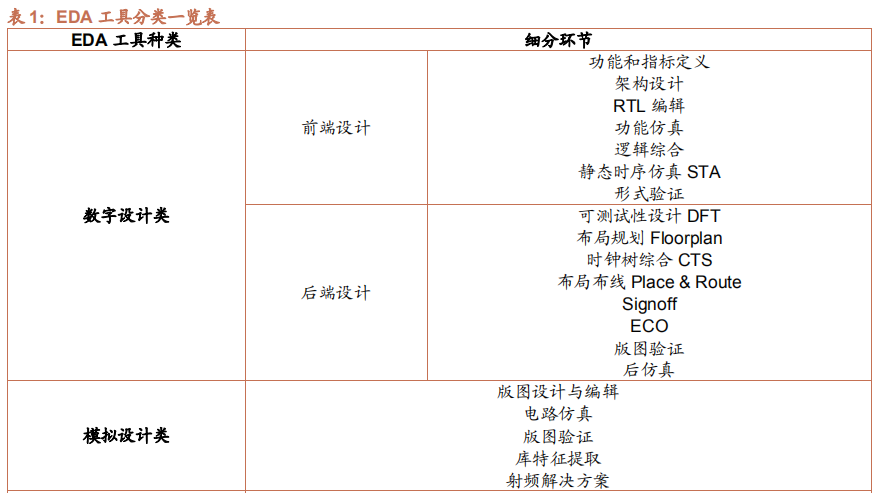

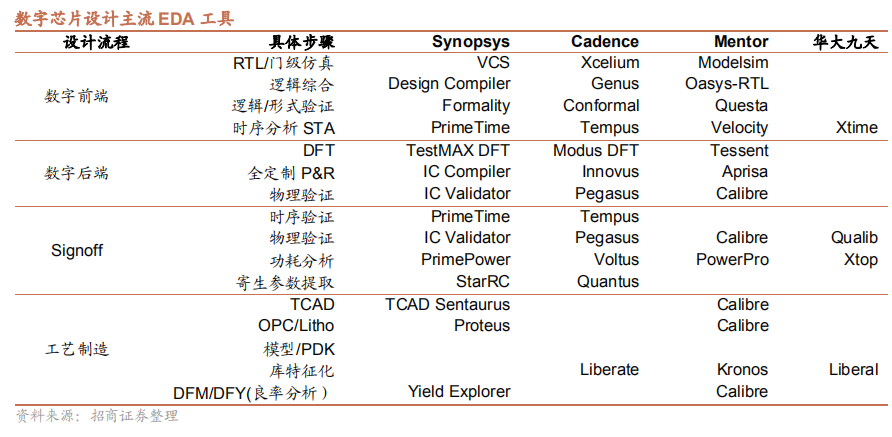

EDA 产品线繁多,根据 EDA 工具的应用场景不同,可以将 EDA 工具分为数字设计类、模拟设计类、晶圆制造类、封装类、系统类等五大类,其中系统类又可以细分为 PCB、平板显示设计工具、系统仿真及原型验证和 CPLD/FPGA设计工具等。

数字设计类工具主要是面向数字芯片设计的工具,是一系列流程化点工具的集合,包括功能和指标定义、架构设计、RTL 编辑、功能仿真、逻辑综合、静态时序仿真(Static Timing Analysis,STA)、形式验证等工具。

模拟设计类工具主要面向模拟芯片的设计工具,包括版图设计与编辑、电路仿真、版图验证、库特征提取、射频设计解决方案等产品线。

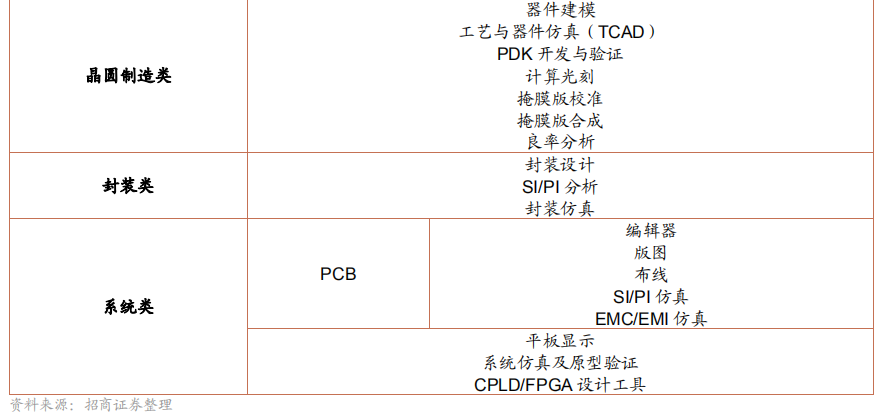

晶圆制造类工具主要是面向晶圆厂/代工厂的设计工具,该类工具主要是协助晶圆厂开发工艺并且实现器件建模和仿真等功能,同时也是生成 PDK 的重要工具,而 PDK 又是作为晶圆厂和设计厂商的重要桥梁的作用,因此可见 EDA工具和工艺绑定紧密,并且随着摩尔定律的推进需不断升级迭代。晶圆制造类工具包括器件建模、工艺和器件仿真(TCAD)、PDK 开发与验证、计算光刻、掩膜版校准、掩膜版合成和良率分析等。

封装类工具主要是面向芯片封装环节的设计、仿真、验证工具,包括封装设计、封装仿真以及 SI/PI(信号完整性/电源完整性)分析。随着芯片先进封装技术发展以及摩尔定律往前推进,封装形式走向高密度、高集成及微小化,因此对于封装的要求和难度有较大提高,目前高性能产品需要先进的集成电路封装,如将多芯片的异质集成封装方式、基于硅片的高密度先进封装(HDAP)、FOWLP、2.5/3DIC、SiP 和 CoWoS 等。

在系统类 EDA 领域,EDA 工具可分为 PCB 设计、平板显示设计、系统仿真工具(Emulation)、CPLD/FPGA 等可编程器件上的电子系统设计。EDA 工程的范畴不断扩展到下游电子系统应用,如果没有 EDA 技术的支持,想完成先进的电子系统设计机会是不可能的,反过来,生产制造技术的不断进步又必将会对 EDA 技术提出新的要求。

在系统类 EDA 中,印刷电路板(PCB)主要用作电子系统的载体,工程师通常将集成电路元器件焊接在 PCB 上完成整个电子系统的搭建、控制、通信等功能。目前主流的 PCB 工具有 Cadence 的 Allegro、Mentor Graphics 的 Xpedition及 Zuken 的 CR 等,国产 PCB 厂商有立创 EDA 等。

平板显示设计主要应用于面板的研发、生产和制造,国内 EDA 公司华大九天已经具备在平板显示领域全流程的工具,并且基本覆盖国内主要的面板厂商客户。

系统仿真工具(Emulation),与传统的仿真工具(Simulation)不同,主要聚焦于系统级别的仿真,广泛应用于加速软硬件联合开发的场景,而传统仿真更多聚焦于单一功能或者局部电路环节的仿真。西门子(Siemens)曾推出PAVE360 自动驾驶硅前验证环境(pre-silicon autonomous validation environment),该产品主要意图在于支持和促进创新自动驾驶汽车平台的研发。PAVE360 为下一代汽车芯片的研发提供了一个跨汽车生态系统、多供应商协作的综合环境,该系统不仅可以实现汽车硬软件子系统、整车模型、传感器数据融合、交通流量的仿真,甚至还仿真自动驾驶汽车最终在智能城市里面的驾驶。目前 EDA 三大巨头都在布局系统仿真工具,主流产品包括 Synopsys 的 Zebu、Cadence 的 Palladium 和 Simens EDA 的 Veloce。

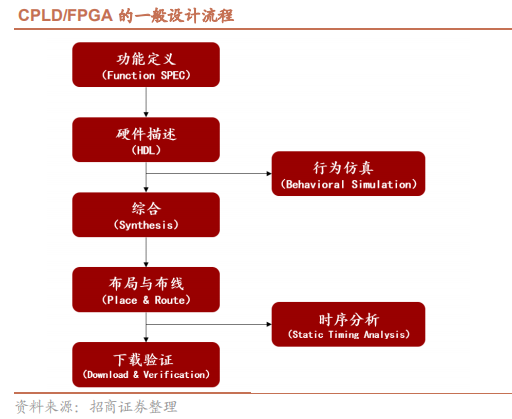

复杂可编程逻辑器件(Complex Programmable Logic Device,CPLD)和现场可编程阵列(Field Programmable Gates Array,FPGA)最显著的优势在于开发周期短、投资风险小、产品上市快和硬件升级余地大等。这两类芯片是比较特殊的芯片类型,需要与 EDA 工具协同才能工作,一般而言开发 CPLD/FPGA 的厂商都需要开发一套成熟的EDA 下载和验证工具来实现对芯片的编程。从 CPLD/FPGA 的简要设计流程可以看出,对工程师而言,其工序相对于传统芯片设计流程有明显减少。目前比较主流的可编程器件的 EDA 集成开发工具主要有 Altera 公司的 MAX+Plus和 Quartus、Xinlinx 公司的 Foundation 和 ISE,Lattice 公司的 ispDesignExpert 和 ispLever,Synopsys 的Synplify 以及 Cadence 的 Precision。

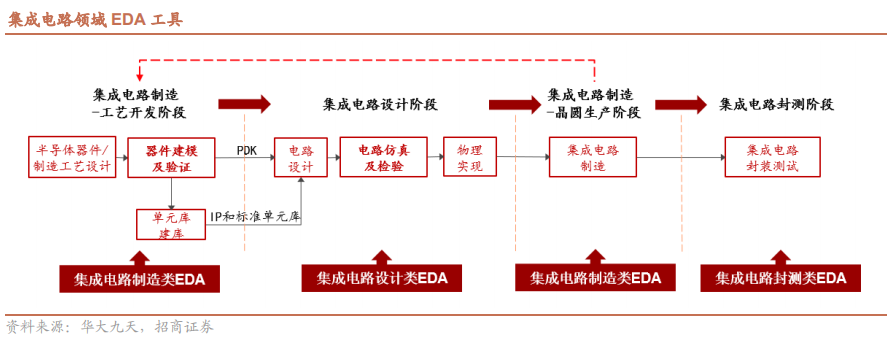

按照集成电路产业链划分,集成电路 EDA 工具可以分为制造类 EDA 工具、设计类 EDA 工具及封测类 EDA 工具。器件建模及仿真类工具就属于制造类 EDA 工具,晶圆厂(包括晶圆代工厂、IDM 制造部门等)借助器件建模及仿真、良率分析等制造类 EDA 工具来协助其工艺平台开发,工艺平台开发阶段主要由晶圆厂主导完成,在其完成半导体器件和制造工艺的设计后,建立半导体器件的模型并通过 PDK 或建立 IP 和标准单元库等方式提供给集成电路设计企业(包括芯片设计公司、半导体 IP 公司、IDM 设计部门等)。

设计类 EDA 工具则是基于晶圆厂或代工厂提供的 PDK或 IP 及标准单元库为芯片设计厂商提供设计服务,芯片设计厂商采用设计类 EDA 工具完成芯片的设计。封装类 EDA工具主要是提供封装方案设计及仿真的功能,从而帮助芯片设计企业完成一颗芯片的全生命周期的设计服务。

数字设计 EDA 的核心环节是逻辑综合和布局布线

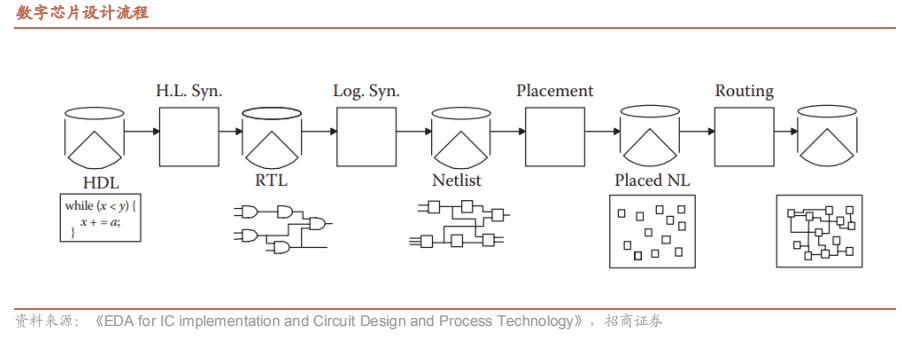

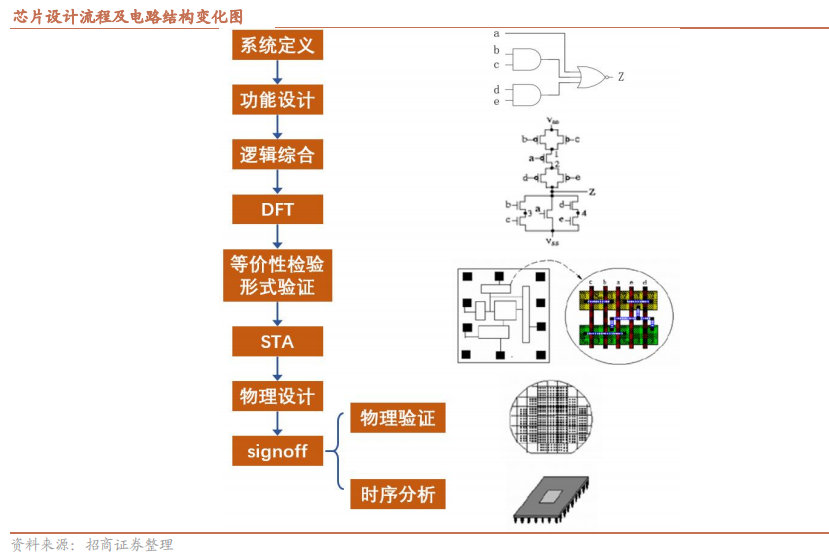

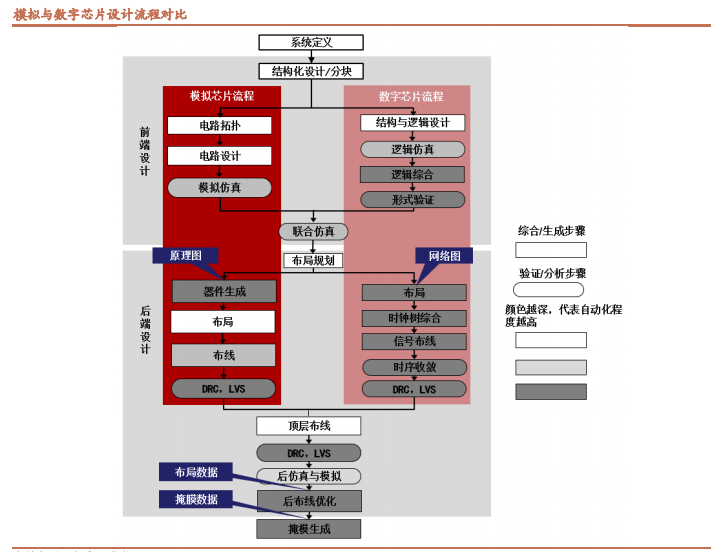

数字芯片设计多采用自顶向下设计方式,可以分为五大步骤:1)系统的行为级设计,确定芯片的功能、性能指标(包括芯片面积、成本等),2)结构设计,根据芯片的特点,将其划分为多个接口清晰、功能相对独立的子模块,3)逻辑设计,采用规则结构来实现,或者利用已验证的逻辑单元,4)电路级设计,得到可靠的电路图,5)将电路图转换为物理版图。

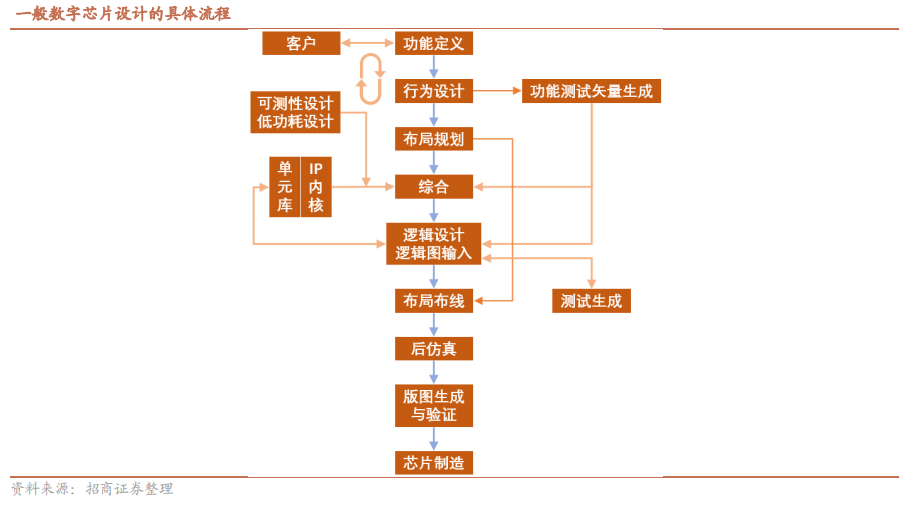

1、系统功能描述:确定芯片规格并做好总体设计方案,是最高层次的抽象描述,包括系统功能、性能、物理尺寸、设计模式、制造工艺等,功能设计主要是为了确定系统功能的实现方案,通常是给出系统的时序图及各子模块之间的数据流图,该部分工作主要是客户向芯片设计厂商(Fabless,无晶圆设计公司)提出的设计要求。

2、逻辑设计:将系统功能结构化,通常是以 RTL(寄存器传输级)代码(VHDL、Verilog、System Verilog 等硬件描述语句)、原理图、逻辑图等表示设计结果,完成相关设计规范的代码编写,并保证代码的可综合、可读性,同时还需要考虑相关模块的复用性。

3、逻辑综合:将逻辑设计中的电路表达语句转换为电路实现,使用芯片制造商提供的标准电路单元加上时间约束(Timing Constraints)等条件,尽可能少的元件和连线完成从 RTL 电路描述映射到综合库单元,得到一个在面积和时序上满足需求的门级网表。逻辑综合步骤是芯片前端设计中的核心环节,关系到整个芯片的 PPA 水平。

4、物理设计/布局布线:在逻辑综合后,基本是只有逻辑和时序约束的设计结果,而物理设计/布局布线则是让电路设计更贴近真实状况,即加入物理约束(Physical Constraints),从而使得电路成为一个真实能够在芯片制造商能够生产的芯片。综合后的网表和时序约束文件导入该环节工具中,进行布局布线,利用相关提取软件进行寄生参数提取,并重新反馈到物理实现的布局布线软件中,再次进行时序计算和重新优化,直到满足时序和功耗要求为止。

5、后仿真/物理验证:布局布线出来的结果是经过多层次的优化后的电路,为了保证该电路与最开始系统功能描述的电路功能一致,就需要进行后仿真/设计验证,主要包括设计规则检查(DRC)、电路版图对照检查(LVS)、电气规则检查(ERC)、寄生参数提取等。

验证工作贯穿整个设计过程。从芯片设计角度看,以物理实现为分界,芯片设计可以划分为前端(逻辑设计)与后端(物理设计),其实现过程中将不断对设计进行优化,优化可能改变逻辑描述方式和结构,存在引入错误的风险,所以验证贯穿整个设计过程,在每个环节都反复确保逻辑优化过程不改变功能、时序满足目标需求、物理规则无违规等等,因此产生大量的验证流程和工作,更涉及多方共同协作。

前端设计主要考虑逻辑和功能层面,后端设计主要目的是物理参数约束的优化。简单而言,前端设计更多的是逻辑/功能层面的实现,实现方式是以基础的逻辑单元进行连接设计,以实现系统需要的逻辑功能,前端设计一般没有过多考虑物理参数的约束,比如电路间走线的长度带来的延时等因素,仅仅考虑了单元器件的电气物理参数。而后端设计则是重点加入了物理约束,比如某些特定电路模块的摆放位置,以及电路间连线的物理参数也会被考量在软件优化中,因此后端设计后的电路更接近于满足需求的实际电路。

模拟和数字芯片设计流程对比方面,模拟芯片设计的自动化程度低于数字芯片设计。借用数字芯片设计的概念,模拟芯片设计也可以分为前后端,前端设计包括电路图设计及生成,涉及大量的算法、计算以及假设验证等,从自动化程度看,数字芯片在前端设计的自动化程度明显高于模拟芯片,主要是模拟芯片需要工程师手动选型电路拓扑并且选择合适的元器件。后端设计方面,数字电路的后端设计基本实现了全自动化,EDA 工具的性能直接影响到芯片产品的性能,模拟芯片后端设计的自动化程度较低,尤其在布局步骤方面。

后摩尔时代技术演进驱动EDA技术应用延伸拓展。后摩尔时代的集成电路技术演进方向主要包括延续摩尔定律(More Moore)、扩展摩尔定律(More than Moore)以及超越摩尔定律(Beyond Moore)三类,主要发展目标涵盖了建立在摩尔定律基础上的生产工艺特征尺寸的进一步微缩、以增加系统集成的多重功能为目标的芯片功能多样化发展,以及通过三维封装(3D Package)、系统级封装(SiP)等方式实现器件功能的融合和产品的多样化。其中,面向延续摩尔定律(More Moore)方向,单芯片的集成规模呈现爆发性增长,为 EDA 工具的设计效率提出了更高的要求。

面向扩展摩尔定律(More than Moore)方向,伴随逻辑、模拟、存储等功能被叠加到同一芯片,EDA 工具需具备对复杂功能设计的更强支撑能力。面向超越摩尔定律方向,新工艺、新材料、新器件等的应用要求 EDA 工具的发展在仿真、验证等关键环节实现方法学的创新。

审核编辑:郭婷

-

西门子EDA发布下一代电子系统设计平台2024-10-12 1526

-

为什么需要调试一个电子系统2022-02-24 1334

-

天线的发展及其对电子系统的影响是什么?2021-05-27 1831

-

基于EDA技术的FPGA设计计算机有哪些应用?2019-11-01 2652

-

基于EDA技术的FPGA该怎么设计?2019-09-03 2279

-

ModelSim 电子系统分析及仿真2018-09-11 3665

-

电子系统设计的基础知识2017-12-22 1231

-

汽车电子系统的极近场EMI扫描技术2017-02-07 904

-

电子系统仿真与MATLAB2016-05-04 5310

-

电子系统设计基本知识2012-08-01 3240

-

现代电子系统中电源技术的发展和应用2009-12-15 1352

-

数字电子系统的EDA设计方法研究2009-11-10 1290

-

电气与电子系统实验指导书2008-09-24 3769

全部0条评论

快来发表一下你的评论吧 !