SIwave与Sigrity在信号完整性方面的对比

描述

目录

1、基本情况介绍

2、仿真流程对比介绍

2.1、视图上的差异

2.2、仿真结果处理的差异

2.3、预处理方面差异

2.4、驱动码型差异

3、结果对比

3.1、读操作

3.2、写操作

4、模型的处理

4.1、IBIS模型

4.2、S参数模型

5、报告生成

6、总结

高速信号仿真工具众多,有较大用户群体的主要有Sigrity,Siwave,Hyperlynx,ADS,CST等。每个工具背后都有自己的黑科技加持,整体上都在朝着更准确、高效、便捷的目标发展。

本文对比了Siwave和Sigrity在SI仿真上的差异,对于新手用户来说,可以选择其中易于上手的一个。作者本人对Siwave更为熟练,Sigrity只是作为日常对比参照,且水平有限,其中有理解错误的地方,欢迎专家老师指点。同时,仿真用到的图纸文件也会放在文章末尾,欢迎各位下载学习。

1、基本情况介绍

本文仿真对象为恩智浦公司官网的i.MX8QXP开发板。(i.MX 8处理器家族高度集成,是英飞凌公司的一款非常具有代表性的产品,其广泛应用于工业控制,智慧城市,智能家居和汽车电子等领域,可支持图形、视频、图像处理、音频和语音功能,能够满足安全认证和高能效方面的需求。)

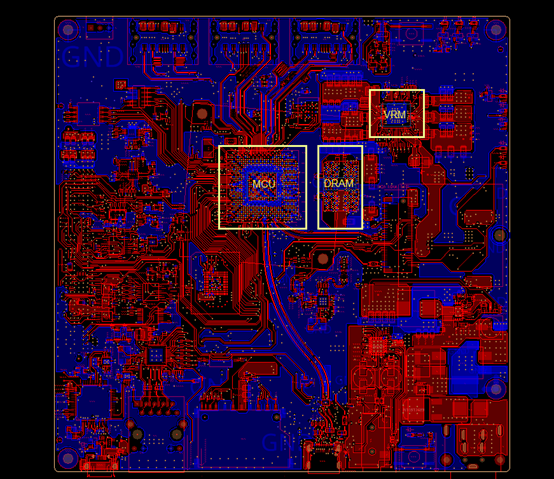

PCB布局整体如下图所示,橙色方框标注的MCU-DRAM-VRM系统为本文主要仿真对象,目标信号为LPDDR4信号。

图1、开发板PCB整体视图

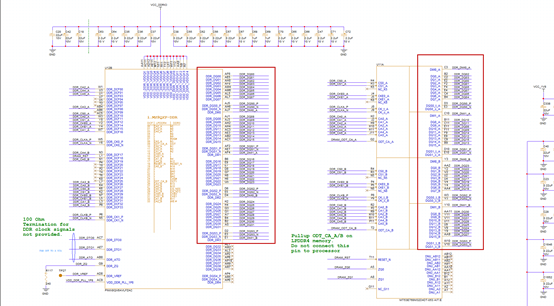

从图2原理图中可以看出(红色方框),目标IC设计中包含了4组数据信号,就对该4组数据信号进行仿真,地址线的仿真方法相同,因此本文不再重复。(根据DDR信号规范,数据信号为整个DRAM系统中速率最快的信号,其次是地址信号,是仿真和测试重点关注的网络,由于整个仿真过程需要参照JEDEC标准规范要求,因此需要对DDR信号规范有一定的了解,不了解的读者可以翻阅本人之前有关DDR4的相关介绍-采用ANSYS进行DDR4仿真。)

图2、开发板原理图中DDR部分

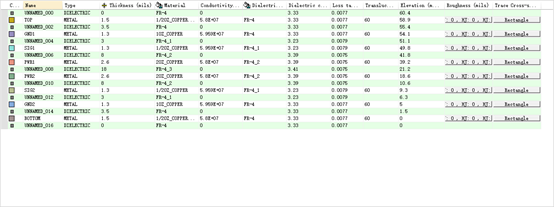

仿真叠层设置如图3所示,确保PCB设置一致,Siwave和Sigrity均使用相同叠层设置。

图3、PCB叠层设置

由于仿真中考虑了信号SSN效应,所以需要同时考虑PDN的影响,为了保持一致,器件参数统一按照下表进行设定。

| 模型参数 | 位号 | 容值 |

| GRM152D70E224ME19 |

C24,C25,C26,C27,C28C29,C30,C35,C36,C37,C38,C43,C44,C45,C46,C55,C56,C57,C62,C1646,C1647,C1648,C1649,C1651,C1652,C1653, C1654,C1655,C1656,C1657 |

2.2E-7 |

| GRM152R60J105ME15 | C68,C69 | 1E-6 |

| GRM155C71A225ME11 | C47,C48,C49,C50,C51,C52,C63,C64,C65,C66,C67,C70,C71,C72,C1645,C1650 | 2E-6 |

| GRM31CC80J226ME19 | C18,C19,C20,C39,C40,C41,C42,C133,C134 | 2.2E-5 |

表1、电源网络电容参数列表

同样为了方便对比,Siwave和Sigrity内器件驱动和接收参数均按照下表设置。

| Mode | Parameter | Value |

| Read | DRAM Slew | PD60-ODT40-VOH30 |

| SOC | ODT-60Ohm | |

| Write | SOC Rout | 80Ohm |

| DRAM | ODT-40Ohm |

表2、器件驱动参数设置表

最后可以简单介绍两款软件,以方便初学者做出适合自己的选择。

1)、Siwave是ANSYS公司发布的一款软件,包含在ANSYS Electronics Desktop(通常也称为“电子桌面”)中,电子桌面主要进行电动力学方面的仿真,可以满足从直流到太赫兹频段的各类仿真需求。其中包含的Siwave、Circuit和HFSS 3D layout三个模块主要用来处理PCB以及相应的电路-PCB协同仿真需求。从软件功能上看,信号完整性仿真仅仅是ANSYS 电子桌面众多能力中的其中之一,除此之外还可以进行电力电子仿真、射频和天线仿真、磁元件仿真以及多物理场的联合仿真等。如果使用者有较为复杂多变的仿真需求,ANSYS是不错的选择。遗憾之处在于,ANSYS公司没有一款Layout工具,这导致其处理PCB仿真需求时需要借助Cadence等其他EDA公司的软件进行部分PCB的前处理工作,这一点在进行PCB的优化上是远不如自带Layout工具的仿真软件方便的。

2)、Sigrity是Cadence公司旗下产品。除去高大上的芯片设计工具,我们通常用到的Cadence软件包主要有Orcad和Allegro,以及Pspice和Sigrity。Orcad和Allegro功能大家都知道,主要是原理图和Layout。Pspice为电路仿真工具。Sigrity为PCB仿真工具,内部包含了System SI,Power SI,Power DC等模块,目的是为满足PCB仿真中的信号和电源协同分析设计和仿真需求。SIgrity与SIwave在算法上非常相似,两者均采用了包括FEM、矩量法和传输线法的混合算法。从这里可以看到,Sigrity背后的Cadence不能处理复杂的电磁场仿真需求,但其在Layout和CAD方面是权威。而且从学习成本上,Sigrity相对资料更多,更容易上手。

2、仿真流程对比介绍

在对DDR的仿真处理上,Siwave和Sigrity整体流程类似。Siwave采用自身进行PCB的S参数提取,然后汇入Circuit中搭建系统电路进行仿真。SIgrity则是通过Power SI进行PCB的S参数提取,然后在System SI中搭建系统电路进行仿真。

2.1、视图上的差异

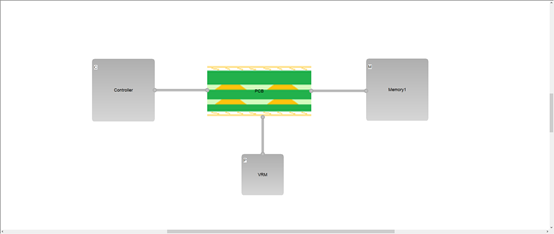

Siwave在汇入Circuit后,整体电路拓扑层次分明,关键信息几乎全部体现在主视窗中。

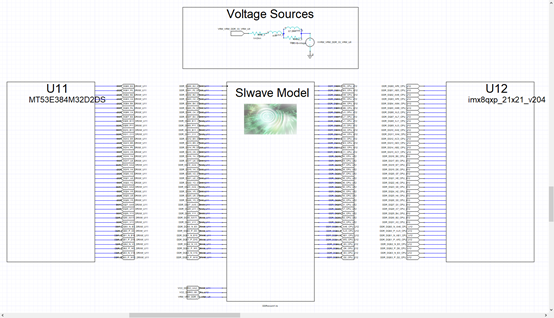

图4、Circuit中搭建的DDR仿真拓扑

Sigrity的系统界面主窗口相比更为简洁,用户需要对电路进行编辑,需要通过双击相应的图标来完成,更多的信息隐藏在二级界面中。

图5、Sigrity中搭建的DDR仿真拓扑

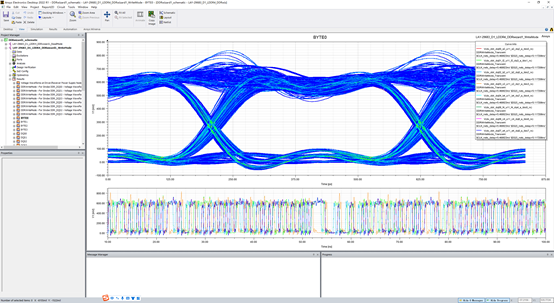

2.2、仿真结果处理的差异

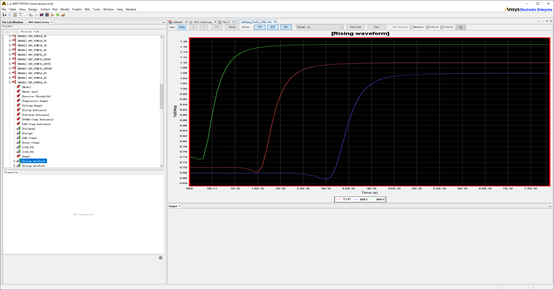

使用Siwave时,用户需要自行调出仿真结果,并且在眼图的导出中需要手动设置UI时长,且在对驱动参数、信号速率等重新编辑后,原始结果会被清除,若要保留则需要手动复制,总之整体的操作过程中手动的部分更多一些。

图6、Circuit仿真结果界面

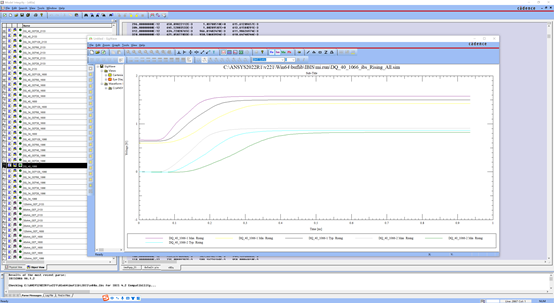

相反在使用Sigrity时,仿真结果是自动生成的,眼图等常用结果的呈现也更为自动化,用户在进行驱动参数、信号速率等重复编辑,软件也能自动保存每次仿真的结果。即整个过程中自动的部分更多一些。

图7、System SI仿真结果界面

2.3、预处理方面差异

Siwave因为整合度较高,充分发挥了ANSYS电子桌面的强大之处,因此在模型预处理方面更为全面,包括S参数的合规性检查,IBIS模型的检查、修复、重新编辑等。因此个人认为更为专业一些。

图8、Siwave对S参数模型的处理

图9、Siwave对IBIS模型的处理

图10、Cadence自带的IBIS模型工具

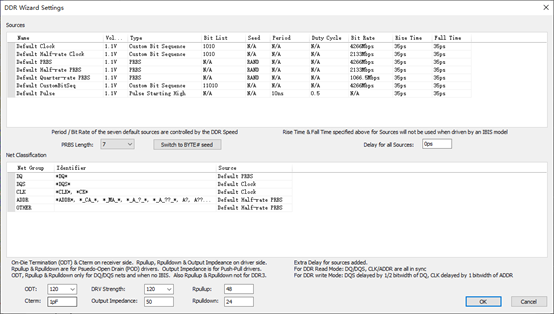

2.4、驱动码型差异

Siwave和Sigrity在驱动码型上存在一定差异。其中,Siwave默认为PRBS码型,可设置每个网络码型由系统随机生成。

图11、Siwave中的码型设置界面

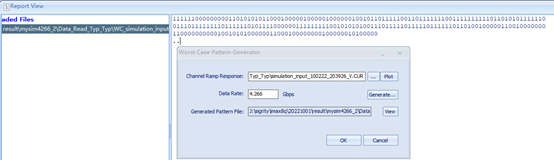

Sigrity在驱动码型的设置上也类似,但多了一个通道检测的功能,可以根据通道响应特性生成“worst case”的驱动码型。这点主要考虑了PDN的SSN效应,根据Larry Smith(高通PI首席专家)的文章,系统在特定的码型驱动下,可以被激发出导致系统崩溃的浪涌,并将这种现象定义为Rogue Wave。从这个角度来看,worst case是一种检验DDR系统鲁棒性的较为便捷的方法。

图12、Sigrity码型生成工具

3、结果对比

设置信号速率为4.266Gbps,分别仿真得到结果。

3.1、读操作

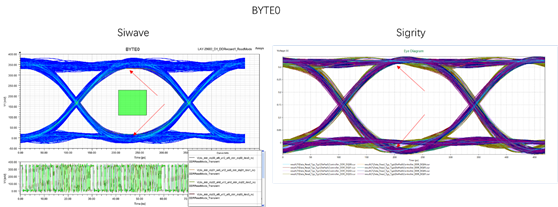

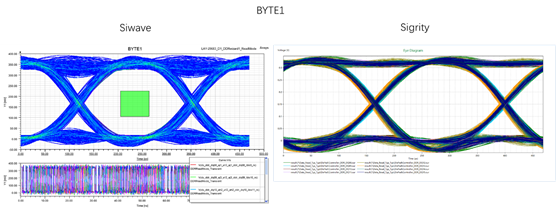

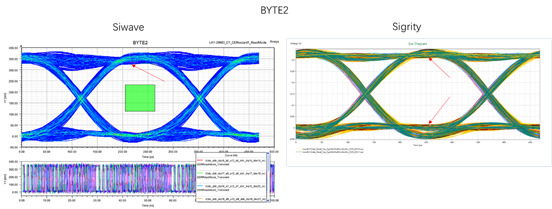

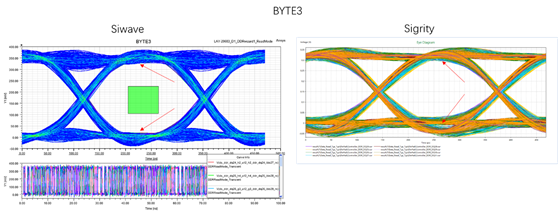

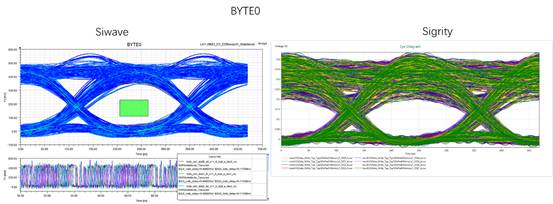

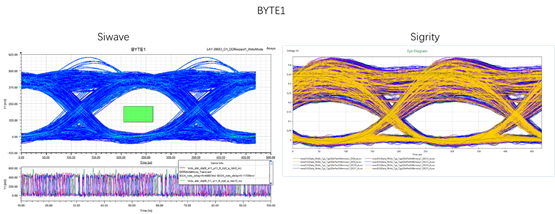

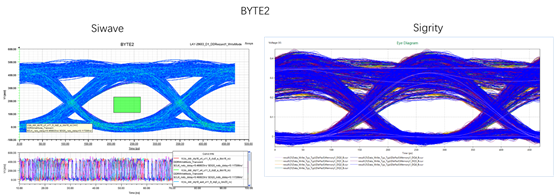

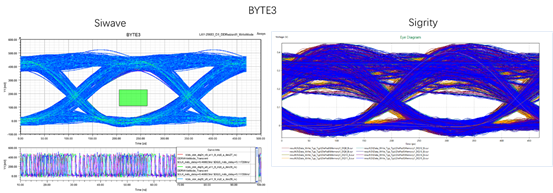

可以看到两个工具在读操作下的结果基本一致,波形细节存在一定的差异,比如Sigrity波形的眼高要略小于Siwave结果。个人猜测可能主要是两个工具在处理IBIS模型数据上存在一定的差异。(为什么不是S参数结果的差异呢?原因在下文中。)

图13、Byte0结果对比

图14、Byte1结果对比

图15、Byte2结果对比

图16、Byte3结果对比

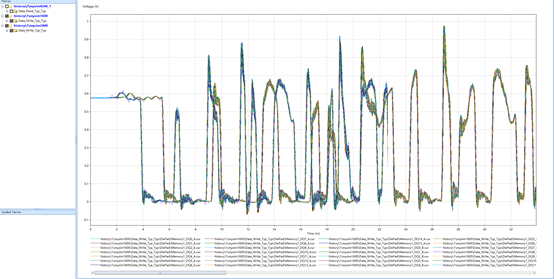

3.2、写操作

在写操作结果中,两者出现了巨大的差异。Siwave取得的结果明显优于Sigrity。Sigrity结果中高电平幅值一致性非常差,导致“眼皮”厚度明显大于Siwave结果。

图17、Byte0结果对比

图18、Byte1结果对比

图19、Byte2结果对比

图20、Byte3结果对比

4、模型的处理

4.1、IBIS模型

按照Wei-hsing Huang(SPISim USA 的首席顾问,后被ANSYS收购)的博客文章,IBIS模型的使用存在频率上限,超出使用频率上限,缓冲器将没有足够的时间来完成上升、下降或两者间的转换。这种情况会导致模拟过程中存在不连续、故障甚至不收敛的情况。我们将这种现象定义为Overclocking。

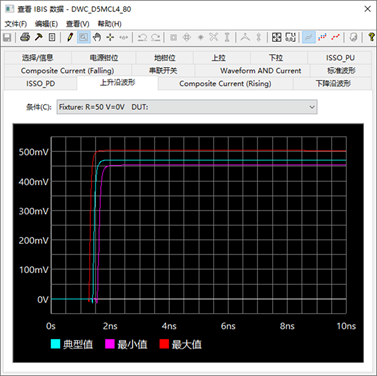

NXP官网提供的MCU模型便存在Overclocking情况,打开其DDR的驱动波形可以看到,其上升沿长度达到了10ns之久,已经严重超出4.266Gbps最小码型宽度。

图21、初始MCU模型上升沿波形

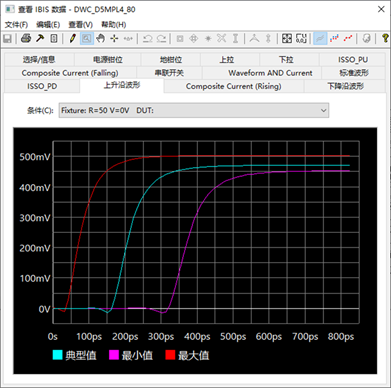

Siwave内部集成了IBIS模型预处理功能,可以最大化的对波形宽度部分进行裁剪,使其满足更高频率的要求。从下图中可以看到,优化后的波形上升沿宽度降低到不到800ps。

图22、优化后MCU模型上升沿波形

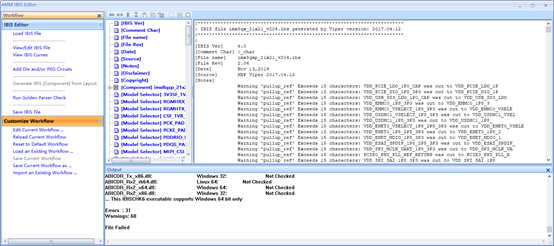

Sigrity中也包含了IBIS模型的检查功能,会对合规性进行检查。但仅限于检查,并未发现进一步优化处理的部分。正因如此,两者在写模式下结果才会出现较大的差异。

图23、Sigrity中的IBIS模型检查功能

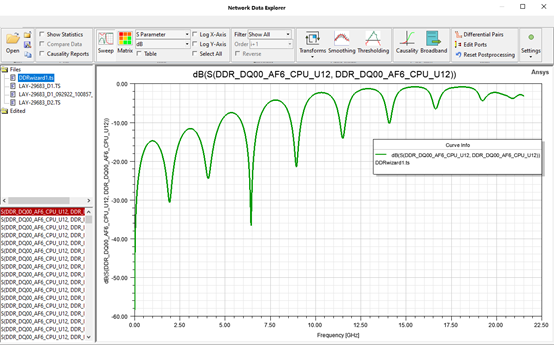

4.2、S参数模型

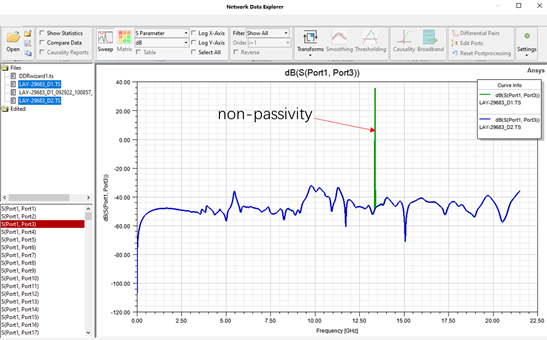

在Sigrity的使用中,发现其Power Si在生成S参数模型时存在不收敛的情况,将两次仿真结果放在一起进行对比,可以看到其中一次存在明显的Non-Passivity情况。笔者也不清楚为何会出现这种情况,希望了解的老师能够解答这个疑问。

图24、PowerSI两次仿真得到S参数对比

5、报告生成

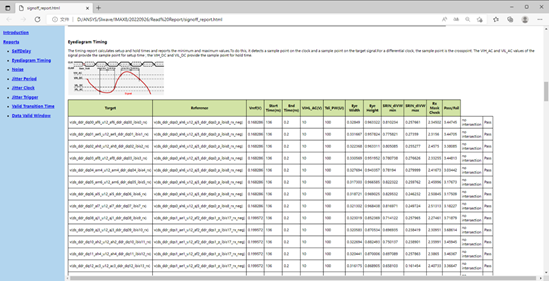

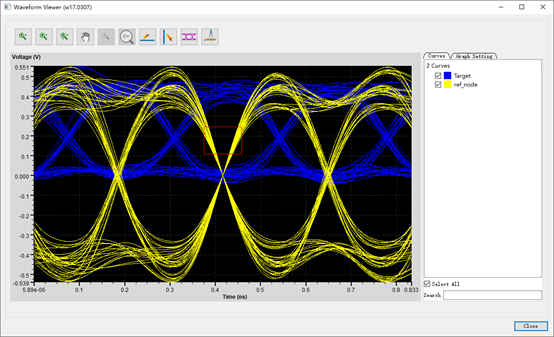

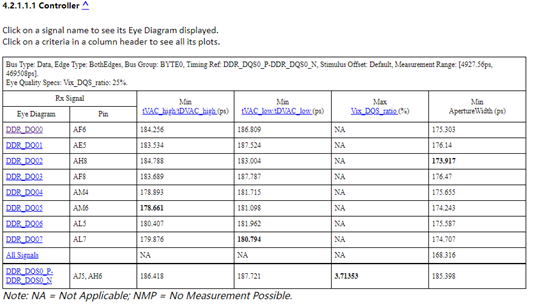

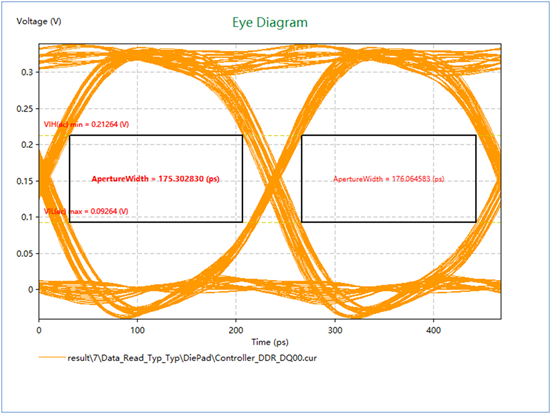

对于复杂的DDR仿真结果,查看JEDEC标准文档逐个进行合规性检查是一件繁琐的事情。Siwave和Sigrity作为成熟的商业软件,均具备完整的报告生成功能。其内置的报告生成功能极大的简化了这部分工作,可以自动对仿真结果进行检查,并且输出合规性报告。

相比之下,Siwave的报告生成功能较为繁琐,使用者需要去对结果信号重新定义,才能得到相应的仿真报告,同时,Siwave的仿真报告中缺乏如叠层信息、去耦电容信息、模型驱动设置等关键信息,且网页格式的结果文档中不能够再次打开波形查看。

图25、Siwave合规性报告(部分截图)

图26、Siwave合规性报告(部分截图)

Sigrity的报告生成相对来讲更为简单便捷,用户不需要重新对信号间关系进行重新定义,仅需要简单的几步操作即可得到完整包含信号波形的结果文件。这点相较于Siwave来讲还是很人性化的。

图27、Sigrity合规性报告(部分截图)

图28、Sigrity合规性报告(部分截图)

6、总结

从简单的横向对比可以看到,主流商业SI仿真工具均可以完成大部分的仿真需求。但现阶段下没有一家可以做到尽善尽美的。若要在产品的研发过程中充分发挥SI的价值,使用者就需要克服软件中存在的不足之处。

本文中使用的PCB文件和IBIS模型已经在网盘中共享给各位读者(链接:https://pan.baidu.com/s/13_ojhpP0glnzss8cXx8a_w提取码:b10s),欢迎大家下载学习,也希望有朋友能够使用其它工具复现本文结果,对市面上的商业软件进行一个横向大比拼!

审核编辑:汤梓红

-

ADS在信号完整性和电源完整性仿真方面的应用2022-08-30 8607

-

什么是电源和信号完整性?2021-12-30 2115

-

详解信号完整性与电源完整性2021-11-15 2561

-

信号完整性与电源完整性的仿真2021-09-29 1649

-

信号完整性精华版资料集,经典案例+pcb设计指南,速来下载~2019-09-03 6325

-

怎样学好“信号完整性”?2017-08-29 21544

-

信号完整性原理2016-08-29 1169

-

关于信号完整性的问题2016-08-12 2176

-

信号完整性与电源完整性仿真分析2011-11-30 2109

-

信号完整性仿真应用2009-11-25 4246

-

信号完整性原理分析2009-11-04 1287

-

什么是信号完整性2009-06-30 5875

全部0条评论

快来发表一下你的评论吧 !