Vitis™统一软件平台2022.2最新更新

描述

本文由 AMD 赛灵思 Vitis 统一软件平台产品营销经理

Eddie Wu 撰写

Vitis 统一软件平台 2022.2 版已正式发布!主要增强特性包括下列内容:

为 Versal AI 引擎阵列提供新的 Vitis 库功能:

DSP 库 - 增强特性。

求解器库功能。

视觉库功能。

超声库功能。

针对 Versal 器件的设计流程增强:

控制内核在 AI 引擎阵列中的相对布局,从而提升性能,提高利用率。

强化面向 Versal ACAP 设计的配置与调试功能,包括死锁检测、较大布线数据采集、RTL/Python 测试平台支持。

Vitis 集成设计环境下的异构设计的新仿真选项。

以下是对部分主要增强特性的介绍:

Vitis 库经过强化,支持更多AI 引擎阵列功能

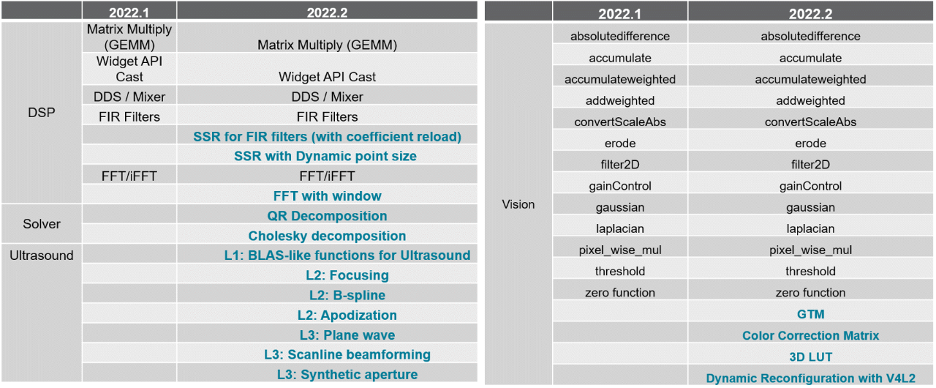

通过系数再加载功能和动态点大小,DSP 库现可支持超高采样率 (SSR) FIR 滤波器。在指向 AI 引擎阵列的 FFT 功能中,新增 FFT 窗口化元素。

对于求解器库,为 AI 引擎阵列新增两个矩阵分解功能,分别是 QR 分解和乔里斯基 (Cholesky) 分解。这两种是得到广泛运用的矩阵运算。

Vitis 视觉库为 AI 引擎阵列新增四项功能:全局色调映射 (GTM)、色彩校正矩阵、3D 查找表和符合 V4L2 的动态重配置。

2022.2 版还提供新的超声库,其中包括 L1 级到 L3 级功能:

L1 例程为超声波提供类似基本线性代数子程序 (BLAS) 的功能。

L2 例程为聚焦、变迹和 b 样条等功能提供 AI 引擎图。

L3 例程提供合成孔径、平面波和扫描线波束成型等超声子系统。

2022.1 版和 2022.2 版为 AI 引擎提供的 Vitis 库的更详细介绍请见下文。

Versal ACAP 设计流程强化

AI 引擎编译器

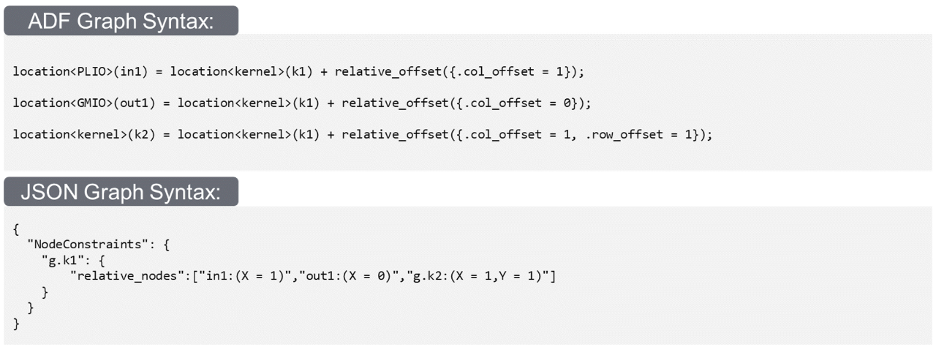

在这个新版本中,AI 引擎相对约束提供了在 AI 引擎内控制内核相对布局的途径。这有利于用户从 AI 引擎阵列获得更高性能和更充分的利用率。可以将约束定义为自适应数据流程 (ADF) 图格式和 JavaScript 对象标记 (JSON) 格式。

ADF 和 JSON 图形语法例如下所示:

Vitis 工具仿真与分析的新特性

1. 采用 Vitis 分析器配置、调试和分析 AI 引擎

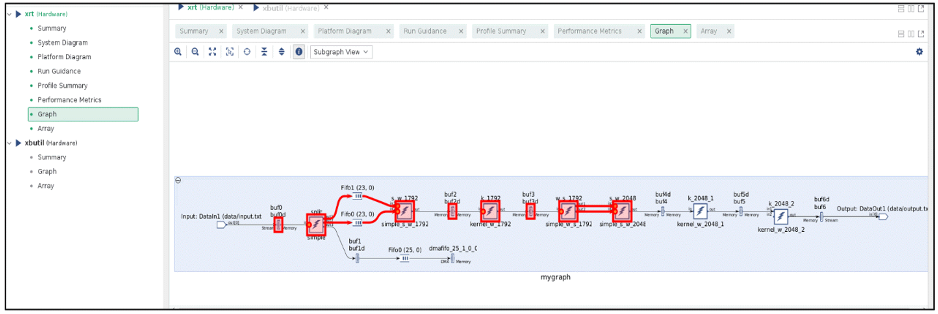

在 2022.2 版中,可以在 Vitis 分析器中的硬件模拟阶段分析 AI 引擎的状态,为调试提供帮助。而在 2022.2 版以前,用户必须在硬件内构建设计,才能开展同样的分析。这项特性允许用户在构建硬件前开展配置,加快迭代速度,同时帮助缩短设计周期。

从 2022.1 版起,通过 Linux 上的 xbutil 和 XRT,就可以启用死锁检测。现在使用赛灵思系统调试器 (XSDB) 也支持同样的特性。这对裸机用户有所帮助。可以生成与 xbutil 生成的文件等效的 JSON 文件。这个文件可以导入 Vitis 分析器查看。

死锁检测流程如下所示:

这项新特性将对 XRT 的支持扩展到对基于 AI 引擎的 XSDB 流程的支持。

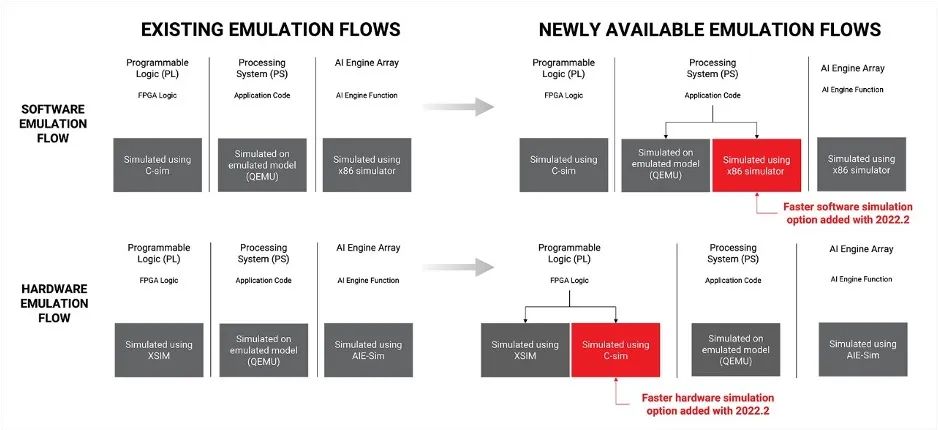

2. 支持在 x86 主机上用 PS 应用开展软件模拟

除了在嵌入式平台上的 QEMU,现在用户可以在 x86 仿真器上通过编译和运行处理系统 (PS) 应用来模拟软件,加快软件模拟的速度。这项功能无需创建 SD 卡镜像,也无需在 QEMU 中引导 Linux,从而避免相关开销,加快周转时间。用户可以使用 XRT 控制加速内核,自己则专注于高级功能模型。使用此功能前,必须在主机上安装赛灵思运行时库 (XRT)。

3. 除了 RTL 以外,还可以使用 SystemC 功能模型进行硬件模拟

与 RTL 相比,SystemC 功能模型能加快编译速度,缩短执行时间。此外,用户也可以搭配使用 C 内核和 RTL 内核来调试 RTL 块。在 2022.2 版中,支持 C/C++ 内核、基于 AXI4-Memory Map 的内核和基于 AXI4-Stream 的内核。

新的仿真选项进一步丰富了用户可用的功能仿真流程,如下所示。这些新的仿真流程主要用于协助实现快速功能仿真。

4.使用简单的 RTL 测试平台或基于 Python 脚本的流量生成器为仿真 AI 引擎内核提供支持

这项特性允许用户将 RTL 测试平台重复用作流量生成器 (TG) 或使用 Python 创建流量生成器。这样做无需完整平台就可以单独验证内核。

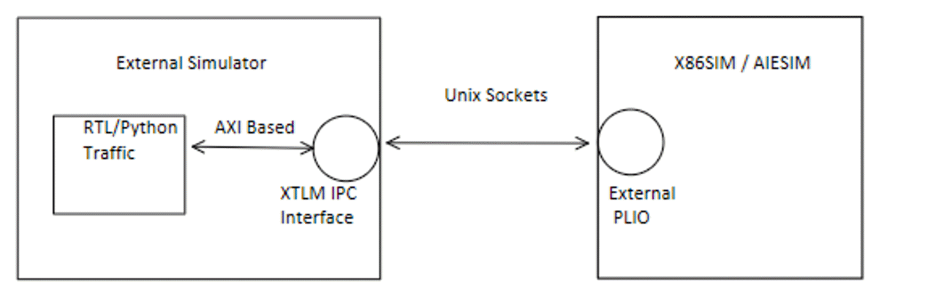

RTL 仿真器使用上述测试平台,x86SIM/AIESIM 负责仿真 C 或 AI 引擎内核代码,利用 Unix 套接字和 XTLM IPC 接口在两个进程间建立通信,如下所示:

通过 Vitis 软件平台 2022.2 版,我们现在支持Python、VHDL、Verilog 和基于 SystemVerilog 的流量生成器。

审核编辑:汤梓红

-

全新AMD Vitis统一软件平台2025.2版本发布2025-12-12 858

-

全新AMD Vitis统一软件平台2025.1版本发布2025-06-24 1938

-

全新AMD Vitis统一软件平台2024.2版本发布2024-12-11 1830

-

Vitis 统一软件平台文档2023-12-20 1697

-

Vitis统一软件平台文档:嵌入式软件开发2023-09-15 717

-

Vitis统一软件平台用户指南:系统性能分析(v2020.1)2023-09-13 689

-

Vitis 统一软件平台文档:应用加速开发2023-07-19 1754

-

在赛灵思FPGA SoC平台上使用VITIS AI加速人工智能应用2022-11-22 3544

-

Vitis软件平台、vitis实例、裸机SOC(SDK)程序移植教程2022-07-25 19334

-

Vitis软件平台、vitis实例、裸机SOC(SDK)程序移植2021-01-31 2441

-

Vivado硬件平台更新后Vitis工程要如何快捷更新2021-01-22 3181

-

Vitis 统一软件平台简介 可实现最高的AI推断性能2020-11-24 4616

-

Xilinx首次推出软件和硬件设计统一的开发工具平台2020-08-17 1622

-

Xilinx Vitis统一软件平台面向所有开发者解锁全新设计体验2019-10-10 3452

全部0条评论

快来发表一下你的评论吧 !