运算放大电路振铃产生的原因及解决方法

模拟技术

描述

写在前面

想必大家都学过运算放大电路,然而电路参数稍微处理不好便会导致你设计的运算电路效果大大折扣。振铃在运算放大电路中是经常出现的问题,因为参数的问题或者PCB板硬件本身的问题,往往导致你设计的放大电路不放大反而振荡,振荡电路不振荡反而放大,大学的时候实验室老师就是这么嘲笑我们的,哈哈。

刚下班,回家也没什么事儿,索性就加会儿班,写个博客,分享自己在这方面的理解,同时呢也做为自己的硬件学习笔记吧,我今天分享得就是运放电路振铃产生的原因,以及解决办法。下面我们开始吧。

振铃产生的原因

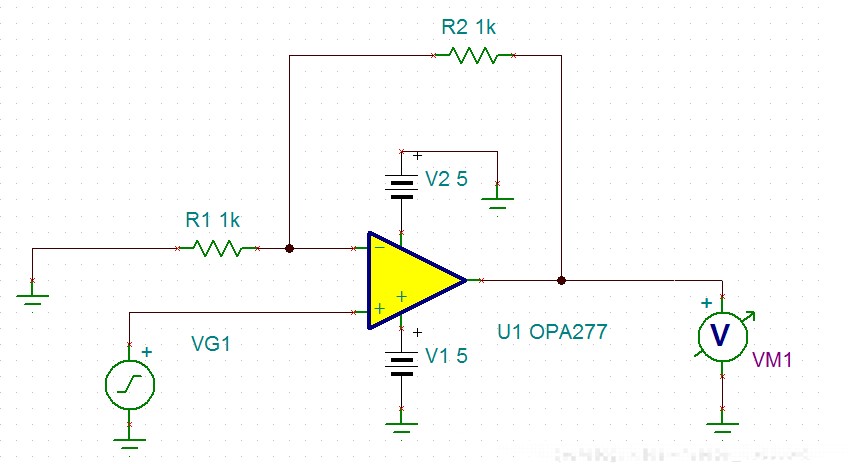

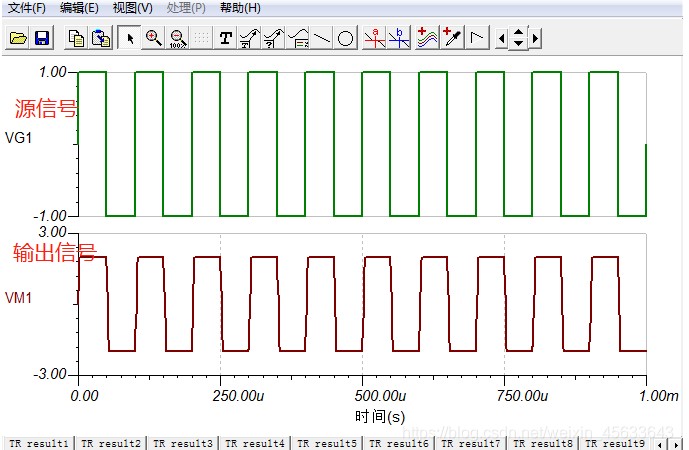

振铃是怎么产生的,知道了这点我们就知道采取什么措施来避免运放电路的振铃的产生。我们先来看一个运算放大电路的例子,如下图所示:为一个同相比例放大电路,信号源频率为10K,幅值1V的方波。运放采用双电源供电。

上图所示的参数下,其输出波形如下图所示,输出波形还算理想,幅值为2V,符合设计所想。但是你要明白仿真软件的仿真结论实在器件理想化的情况下建立的,所以此处的运放也是理想运放,不存在寄生电感电容电阻等,所以仿真结果趋于理想化。当器件焊接到PCB板上以后,PCB板的各种寄生参数都会影响运放的外围参数,同时现实中使用的运放也不是理想化的,这连两个因素使运放往往不以我们所期待的方式运行。我们今天要讲的运放电路的振铃,就是从PCB板的寄生参数出发去分析它产生的原因。

运放振铃产的原因就是由于反向输入端的寄生电容与反馈电阻构成了一个低通滤波器,大家知道低通滤波器会导致相位滞后。而运算放大器呢,又是一个无脑的东西,它不知道人们把它接成了什么样子,它只知道吧同相端与反相端的电压差值放大无穷大倍,然而放大倍数又不可能无穷大,这就得益于输出端的反馈回路。当输出电压过大时,反馈到反相端的电压也会变大,进而输出端电压减小,当输出端电压过小时,反馈到反相端的电压就变小,进而使输出端的电压增大,这样的一个过程如此往复形成一个动态平衡,保持输出端电压稳定。

但是当反馈回路出现了延迟,会出现什么情况呢?那就是输出端的电压已经到达预定电压值了,可是由于反馈回路上的延迟,运放认为输出端的电压还没增加到达预定电压,还在继续增大输出电压,当运放反应过来之后又发现输出电压过大,又开始减小输出电压,当输出端的电压已经减小到达预定电压值了,同样由于延迟的存在,运放认为输出端的电压还没减小到预定电压,当运放反应过来时输出电压又低于预定电压了,然后又开始增大输出电压。循环往复,这就产生了振铃。这一节我们讲了振铃产生的原因,下一节我们就来看看振铃到底是什么样的。

见识振铃

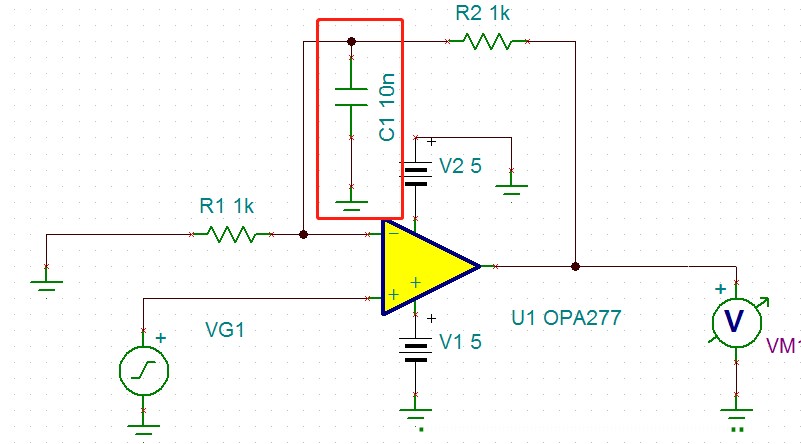

上面我们说了振铃产生的原因,下面我们就人为制造一个振铃产生的条件:在反向输入端并一个电容到地,让其与反馈电阻构成一个低通滤波器的延迟环节。如下图所示:红色圈住的部分为人为加入的反相端寄生电容10nF,其他参数不变。

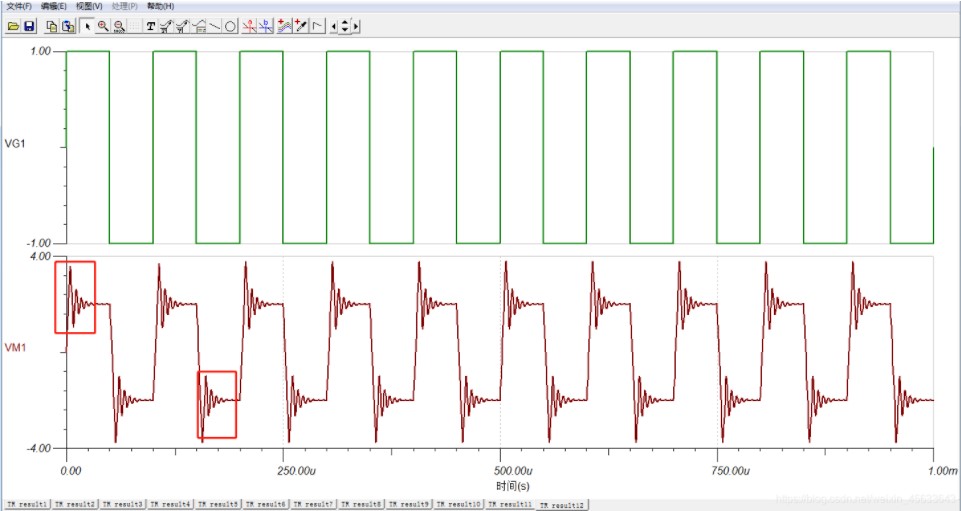

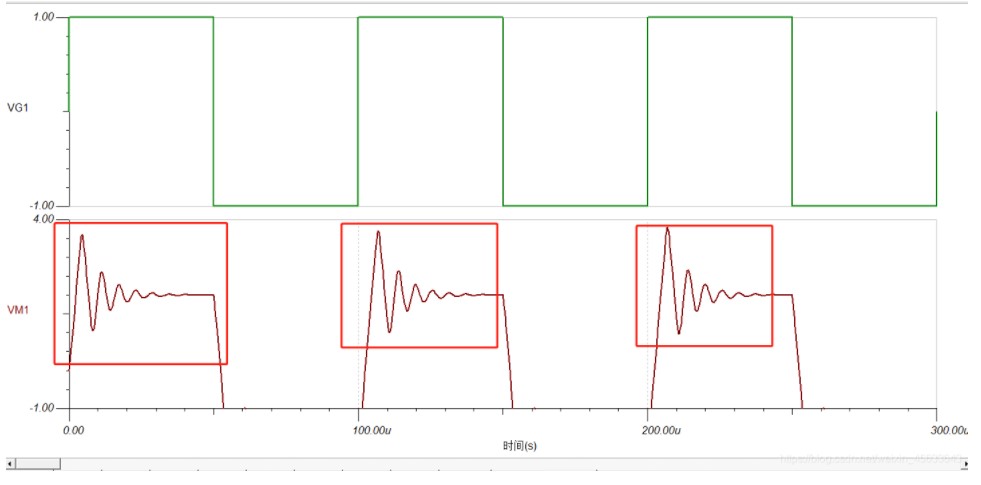

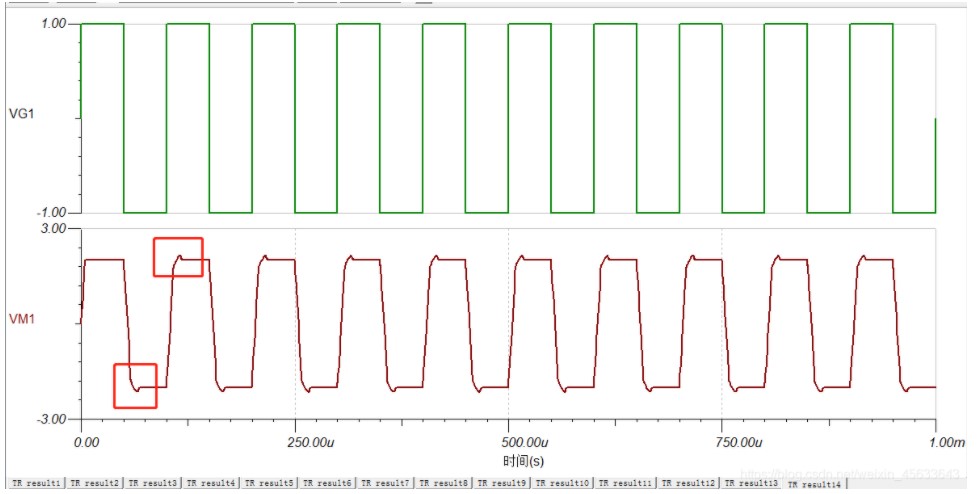

参数设置完毕,我们来看下输出波形,如下图所示:

看不清楚?我们在来个特写:振铃就是这样的,跟我们刚才分析的一样。

产生振铃的其他原因

上面我们说到了产生振铃的原因是反相输入端的寄生电容,除了这个原因还有其他什么原因会导致振铃的产生呢?有的,

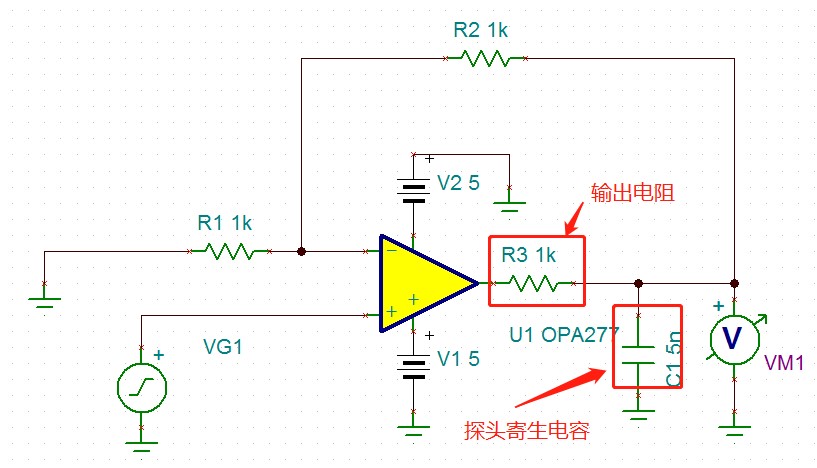

1、当你在使用示波器测量波形的时候,由于示波器探头也存在寄生电容,这个电容与运放的输出电阻也构成了低通滤波的延迟环节,同样的也会造成振铃现象,我们来看图:

来看看这种情况下的输出波形,不出意外的,也出现了振铃:

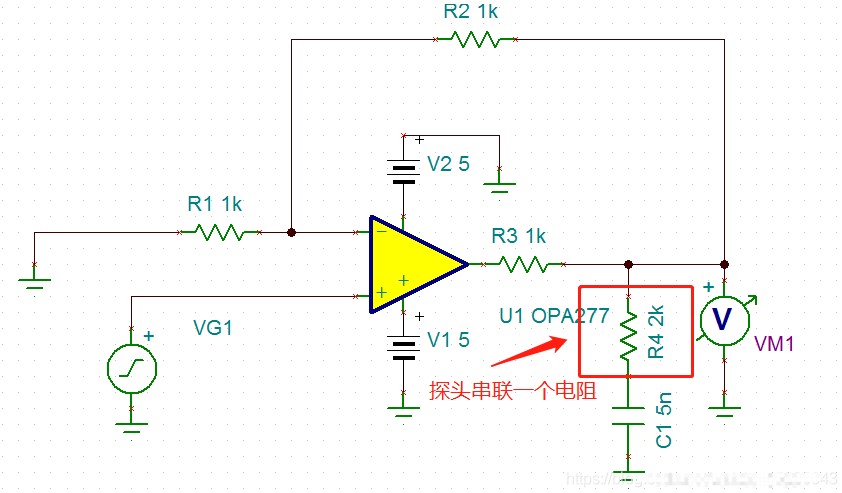

怎么解决示波器探头的寄生电容的问题呢,总不能不用吧,当然不是,有钱的话可以买些有源探头呀,只不过有点贵。不买也行,就教你一个方法,在是示波器探头上串一个电阻,破坏掉低通滤波器的形成环境,因为是示波器的探头阻抗很大,串一个电阻进去,对测量结果基本没影响,好了不多说,上图:

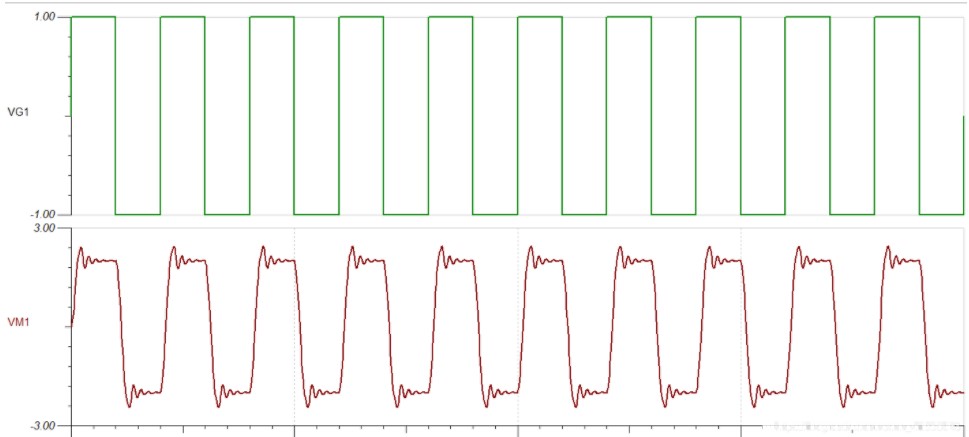

再来看看输出波形,振铃现象是不是明显改善了呀,想要尽量改善振铃甚至避免振铃现象就要合理的设置参数,这里就不一点一点修改参数了,只指明一个方向,具体电路具体分析。

2、运放本身的容性负载,也会导致振铃的产生,其具体解决方法同1,这里就不做过多的分析解释。

PCB板上运放的反相输入端不要覆铜

为什么呢? 就是我们前面说的,反相输入端如果覆铜的话会导致反相输入端存在寄生电容,这也是振铃产生的重要原因。而同相输入端则可以覆铜,因为同相端即使存在延迟也不会导致振铃产生。

-

运算放大电路是如何进行补偿的2022-11-04 4909

-

运算放大器振荡的解决办法2024-09-13 601

-

什么叫放大电路的振铃现象2015-04-11 5166

-

“驯服”振荡运算放大器2018-09-26 1991

-

开关电路中的三极管产生漏电源的原因及解决方法?2020-02-17 6048

-

变频器过电压产生的原因及解决方法2009-12-30 6138

-

产生虚焊的原因及解决方法介绍2018-02-27 91779

-

图像处理振铃效应原理_图像处理中振铃现象2018-05-14 21266

-

振铃产生的原因介绍2018-08-17 10431

-

回流焊锡珠产生的原因及解决方法2020-04-03 10477

-

锡珠产生的常见原因及解决方法2022-07-30 22160

-

焊接机器人焊偏产生的原因及解决方法2023-03-06 2901

-

高低频的阻抗匹配电路概念及要点 高速电路的振铃产生原因及解决办法2023-09-22 15677

-

PCB产生串扰的原因及解决方法2024-01-18 3370

-

BGA焊接产生不饱满焊点的原因和解决方法2024-11-18 2133

全部0条评论

快来发表一下你的评论吧 !