PCB制作正片图电流程的电镀夹膜问题如何解决

PCB设计

描述

传统PCB制作流程有两种:正片图电流程和负片直蚀流程,两种流程对线路图形的设计要求各不相同。特别是正片流程,如果外层线路设计不合理,如有大的空旷独立线路,会在图电时产生夹膜问题,导致蚀刻时短路。

为什么正片图电流程空旷区这种小间隙的位置会更容易产生蚀刻不净短路,首先要了解一下正片图电流程的生产过程:前工序--à沉铜/板电--à线路图形转移--à图电(镀铜镀锡)--à退锡蚀刻--à后工序。

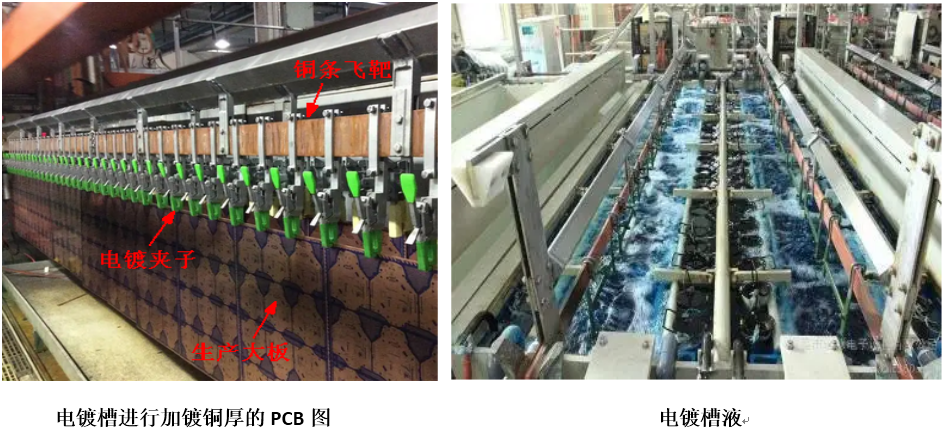

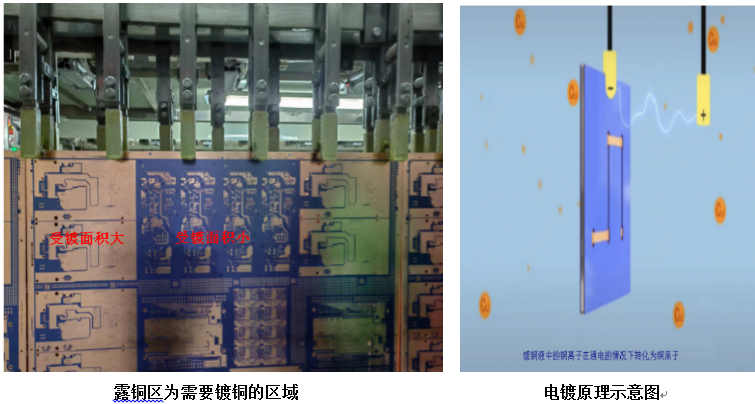

电镀的原理是将生产大板并排夹在一条铜条飞靶上,再把板子放到含有铜离子的电镀槽液中,电流通过铜条飞靶传递到板子上,板子上露出铜面的地方在电流的作用下,会吸附电镀槽液中的铜的离子,并还原成铜原子。

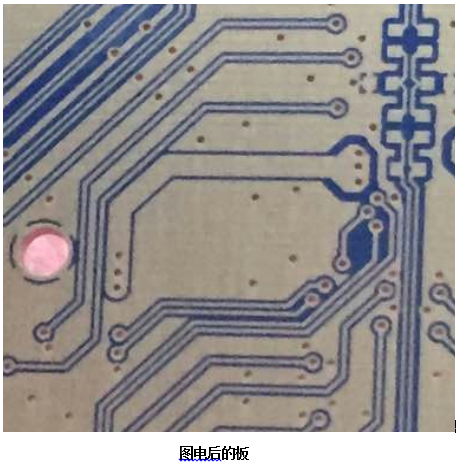

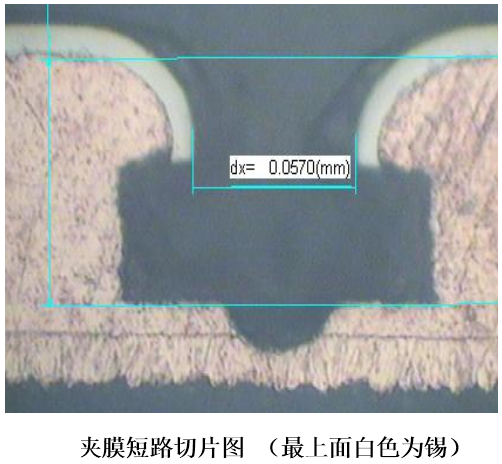

下图蓝色为干膜,白色为图电后的线路及铜面,图电为先镀铜,后镀锡,蚀刻时用锡来保护走线及铜面的,所以图电后板面有一层白色的锡,蚀刻前需板蓝色的干膜先退洗掉,露出铜面过行蚀刻,蚀刻后再把锡退先掉,就得到我们想要线路图形了。

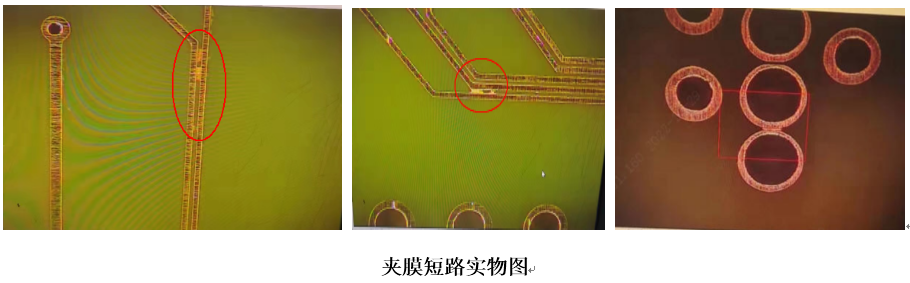

电流的大小与受镀面积有关,如果板子上线路分布太过空旷,特别是分布不均匀的独立线区域,所受到的电流非常大,严重会导致电流过大烧板,轻则导致独立线区域镀铜很厚,当线与线,线与焊盘,焊盘与焊盘等间隙过小时,如4mil以下间隙,则会导致这些间隙过小的地方存在线路板行业经常说的一个名词叫“夹膜”就是把下图中的干膜夹在中间,导致后续的不能蚀刻,从而造成品质问题。

以上说的夹膜,可能有些小伙伴不太理解,做正片线路工艺也叫图电工艺,做外层线路时先在板面上压干膜,再通过曝光,显影等工序,露出需要电镀的走线及铜面,成品无铜区域会被干膜覆盖,这样电镀就只会镀我们需要的走线及孔壁铜等,夹膜是指当线路间隙较小时,如果铺铜不均匀或是没有铺铜的线路,电镀时走线铜厚会超过干膜的厚度,随着电镀时间的增加,电镀铜锡就有可能会从干膜两侧延伸包裹干膜,这种现象就称为夹膜。在蚀刻时需要先把干膜退洗掉,露出需要蚀刻的铜面,而夹膜的地方干膜就无法完全去掉,由于干膜本身也是抗蚀层,蚀刻时此处的铜就保留下来造成板子短路。

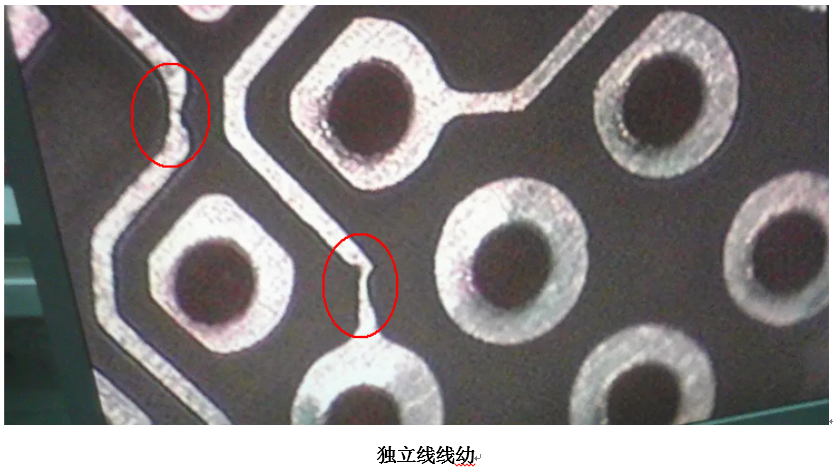

除夹膜外,独立线路还会因为空旷区蚀刻药水活性大,咬蚀过快,导致线幼。

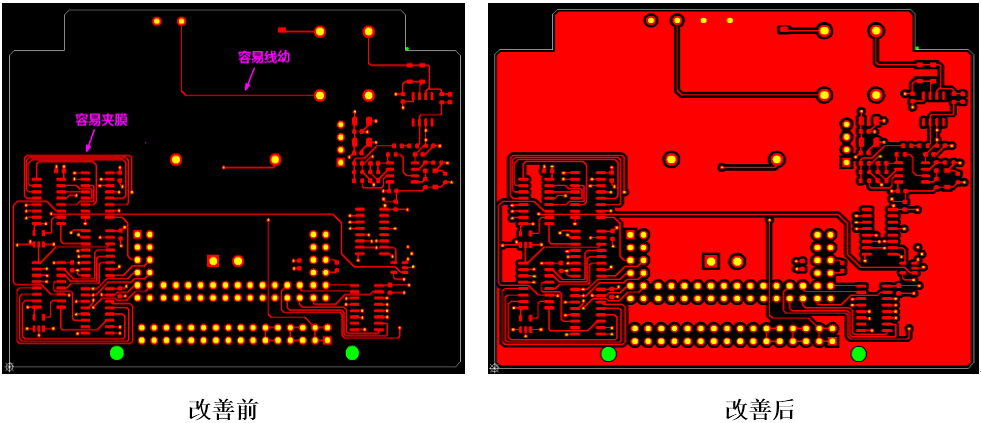

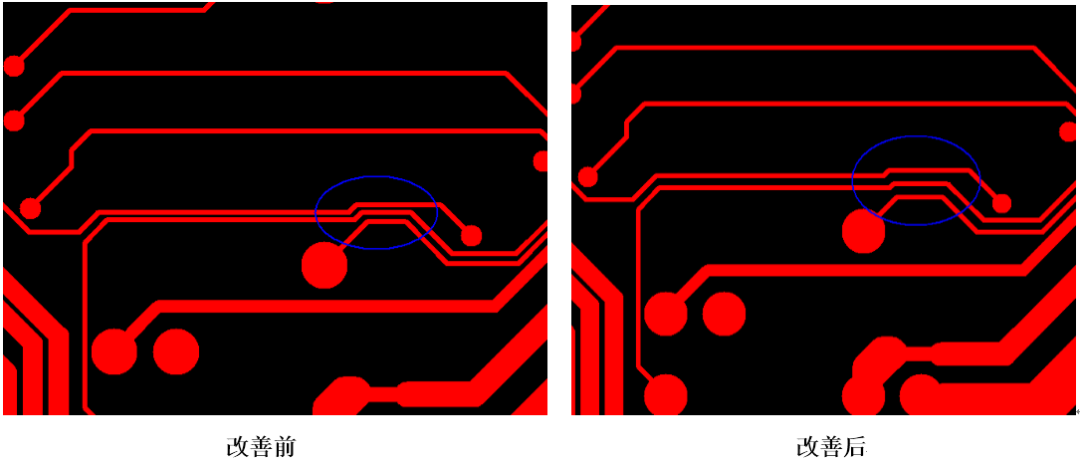

改善建议:

(1)空旷区铺铜 ,提高受镀面积,保证电镀均匀。

(2)无法铺铜时,可以加大独立区线距至6mil以上(1OZ)

编辑:黄飞

- 相关推荐

- 热点推荐

- 电镀

-

电镀塞孔如何解决PCB的信号、机械和环境问题?2024-02-27 1365

-

pcb正片和负片流程差异2024-01-23 5993

-

PCB正片和负片有哪些区别2023-11-08 2977

-

单双面板生产工艺流程(四):全板电镀与图形电镀2023-02-10 10602

-

正片工艺、负片工艺,到底是怎样的呢?华秋一文告诉你2022-12-08 12509

-

电镀夹膜形成的原因及改善建议2022-11-06 4385

-

PCB夹膜产生的原因及解决方法2020-07-19 5865

-

如何解决PCB板的电镀夹膜问题2020-03-08 4155

-

pcb夹膜怎么处理2019-05-09 5035

-

PCB图形电镀夹膜原因分析2018-09-20 6899

-

PCB板夹膜原因分析2018-05-30 12354

-

我们知道的PCB正片和负片有哪些区别 ?2017-06-23 6369

-

PCB样板的正片与负片简介2016-12-19 4288

全部0条评论

快来发表一下你的评论吧 !