FPGA设计:为什么要做同步设计?

可编程逻辑

1397人已加入

描述

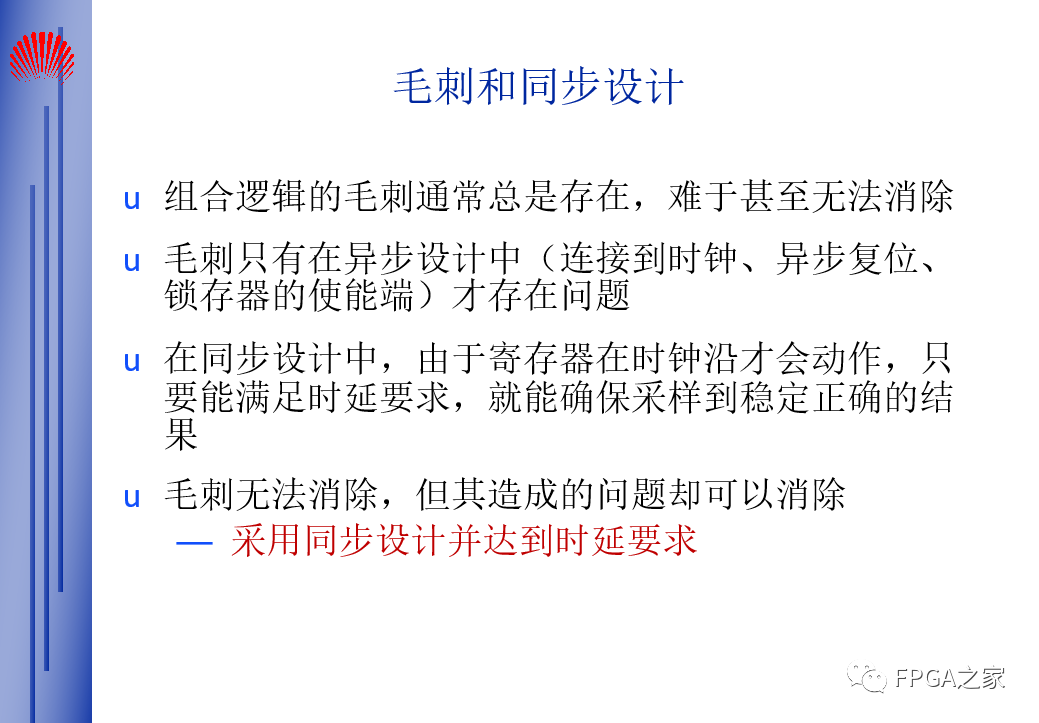

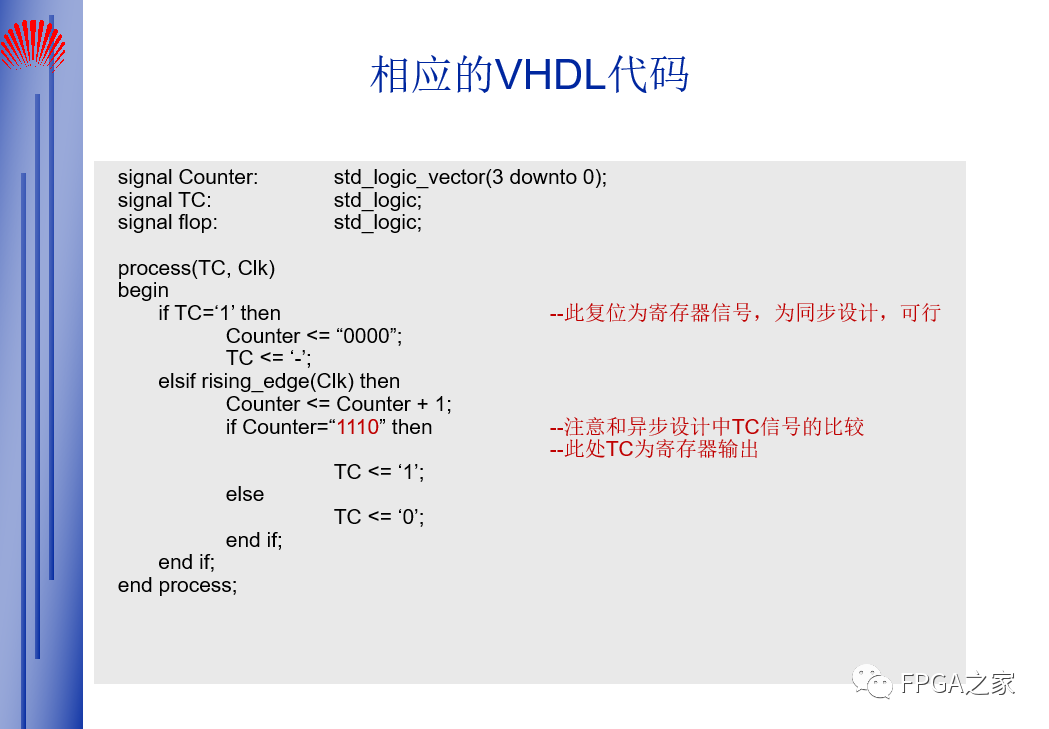

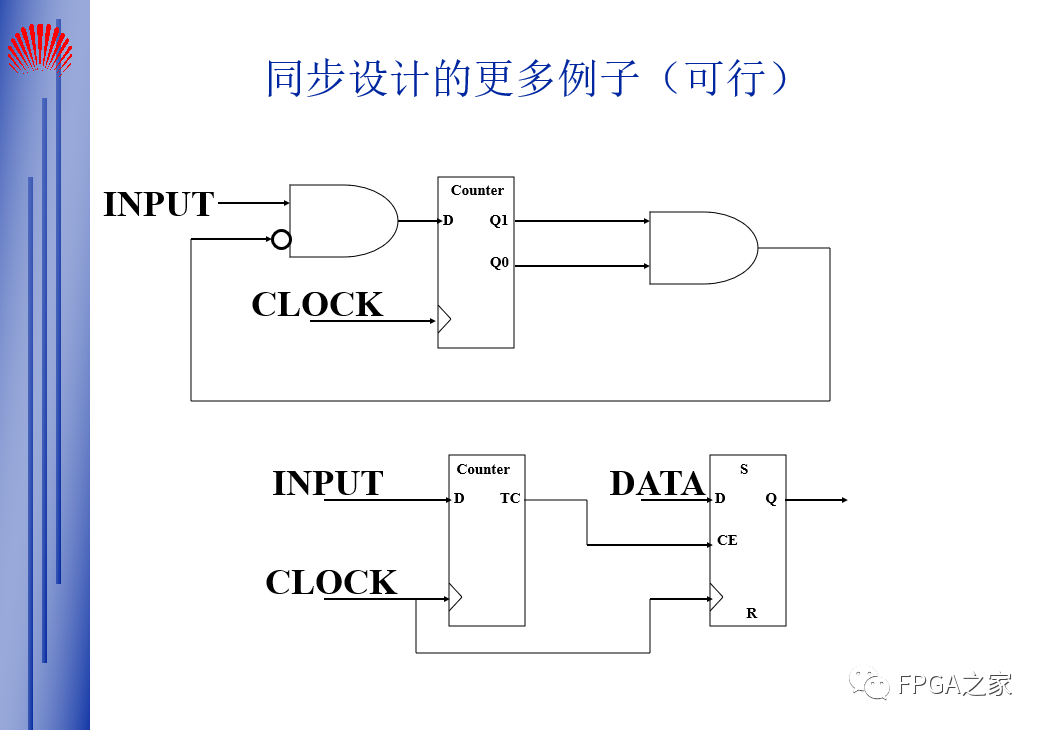

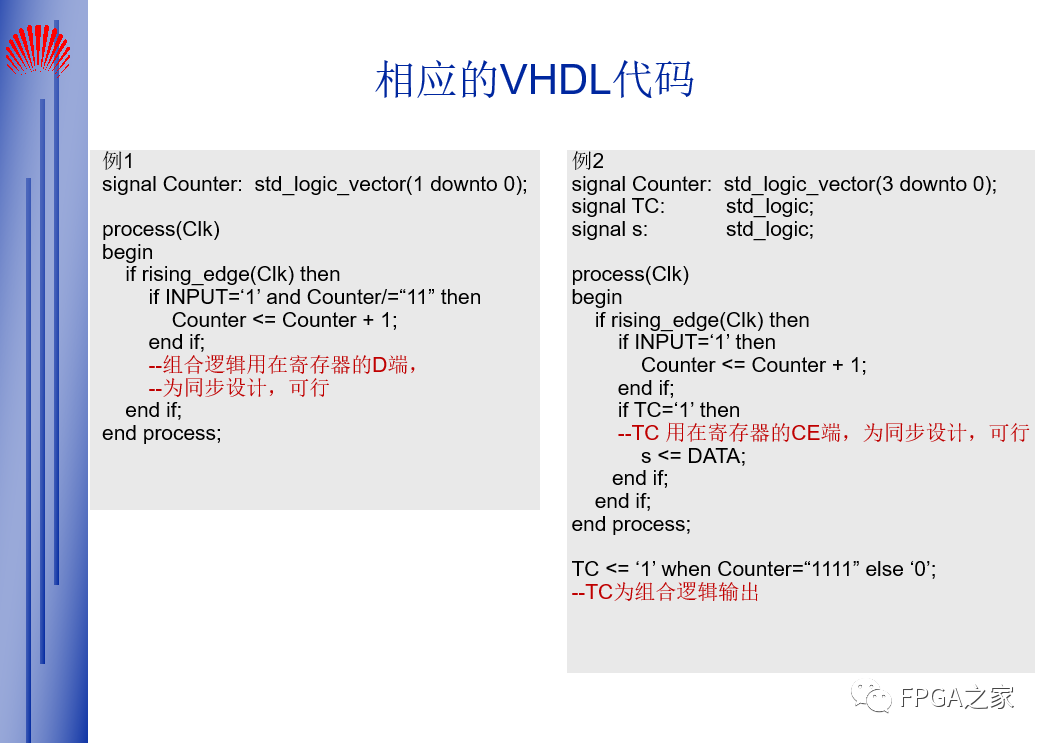

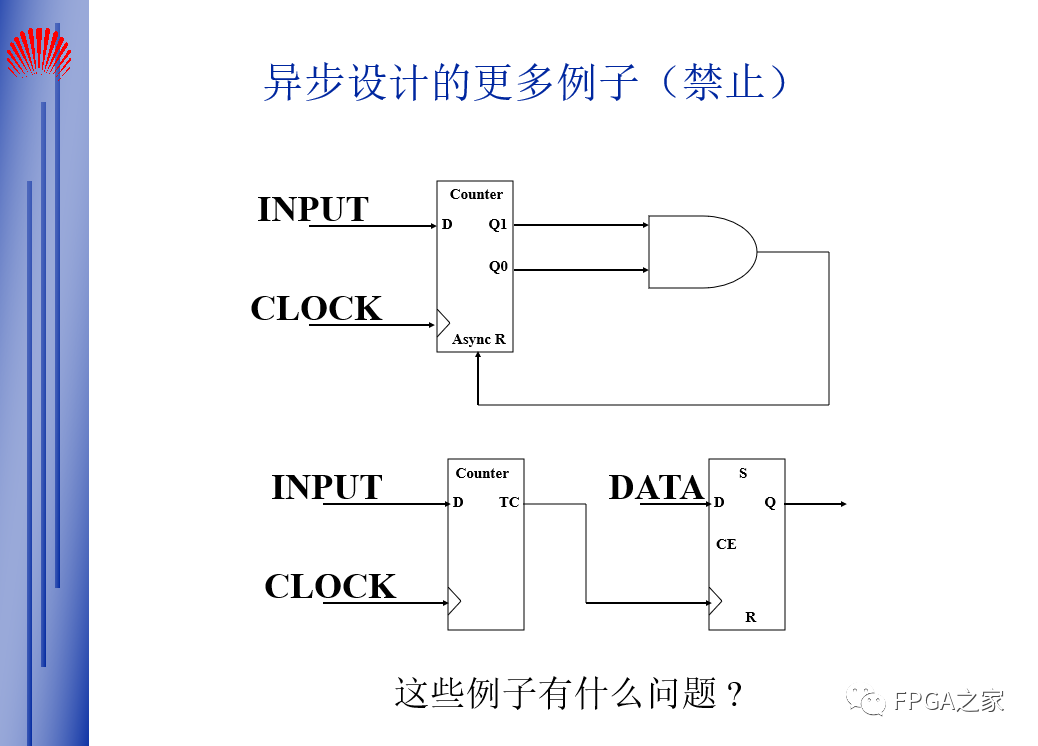

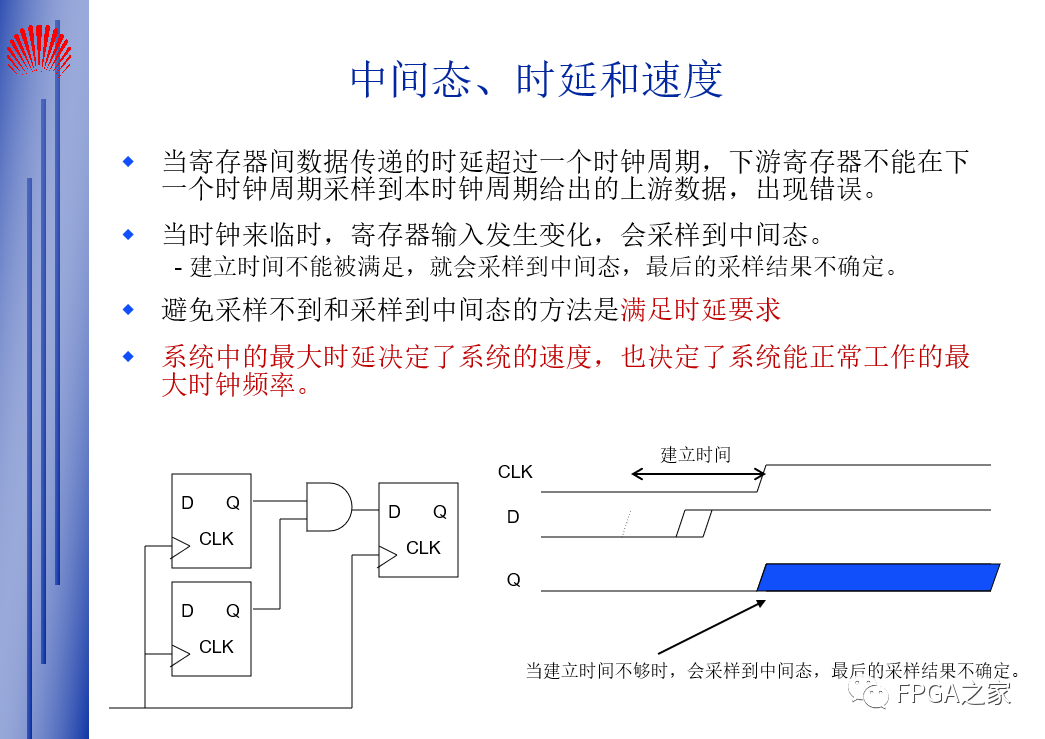

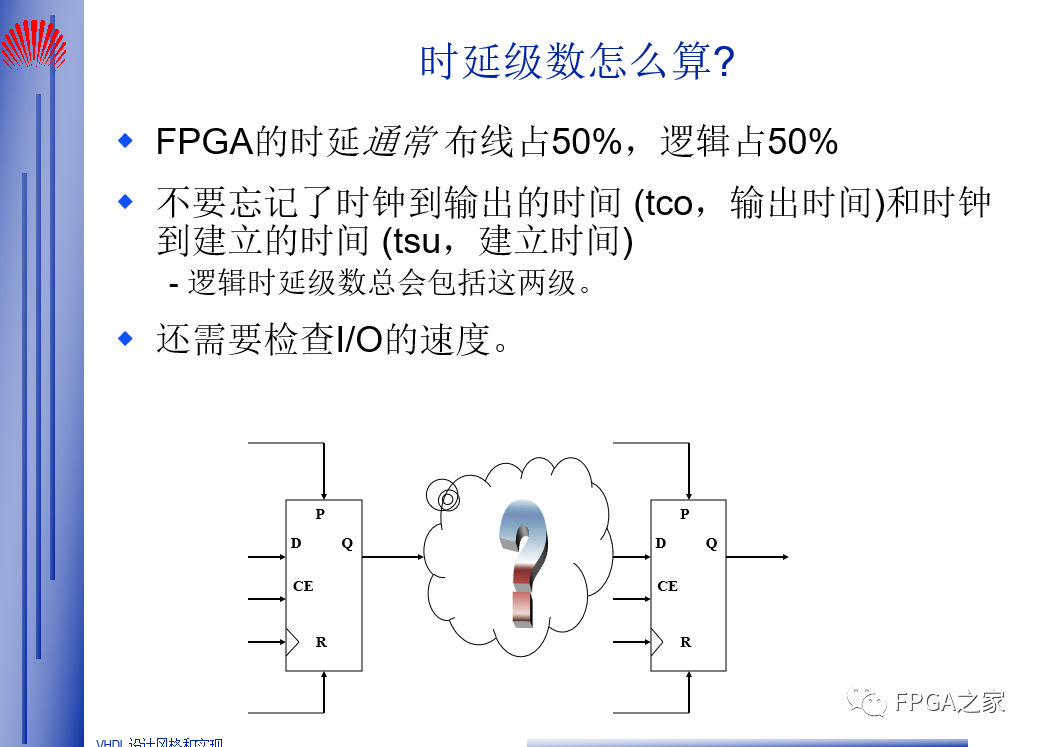

同步设计:。 上游数据到下游逻辑单元的传递是通过时钟来同步的

-只要能满足时延要求,就可以确保下游逻辑单元能正确采样到_上游数据。

编辑:黄飞

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

同步与多个FPGA接口的千兆样本ADC2024-10-10 416

-

fpga与dsp通讯怎样同步时钟频率?dsp和fpga通信如何测试?2023-10-18 3569

-

基于FPGA实现电路的同步提取性能设计2019-04-19 4547

-

采用FPGA实现同步、帧同步系统的设计2017-11-07 1289

-

同步异步通信转换的CPLD_FPGA设计2016-12-16 969

-

基于FPGA的帧同步器的设计与仿真2016-01-04 668

-

基于FPGA的帧同步系统设计方案2013-11-11 5982

-

WCDMA主同步的FPGA实现2011-05-14 1209

-

帧同步系统的FPGA设计2010-08-06 886

-

基于FPGA的快速位同步系统设计2010-07-28 760

-

利用FPGA的永磁同步电机控制器原理及设计2010-03-17 3911

-

FPGA的同步设计2010-01-25 619

-

FPGA的时钟频率同步设计2010-01-04 3230

-

基于FPGA的GPS同步时钟装置的设计2009-07-30 880

全部0条评论

快来发表一下你的评论吧 !