自动性能测量和时序分析有助于军事嵌入式系统避免过早过时

描述

陆地、海洋和空中军事嵌入式系统的持续成功取决于修改系统以满足新兴需求的能力。随着时间的推移,对基于软件的系统累积的修改会导致该系统的性能下降。最终,由此产生的性能下降使系统开发人员可以选择放弃计划的新功能或更换硬件并接受早期过时。还有另一种选择。自动性能测量和时序分析技术为开发人员提供了优化累积修改导致的大部分性能下降的工具,从而避免放弃功能或过早过时。

军事嵌入式系统在其生命周期中通常会多次增强。其中许多增强功能都是软件更新。随着时间的推移,软件更新累积起来增加了对计算平台的需求。这可能导致硬件的功能不足以满足应用程序需求,并可能导致间歇性故障。

然后,系统开发人员面临着艰难的选择,要么放弃计划的新功能,导致功能衰减,要么更换硬件(即早期过时)。

一个可行的替代方案需要确定高影响、低风险的策略来优化软件,从而最大限度地延长计算平台的使用寿命。此替代方案包括自动性能测量和时序分析。

性能问题

军用嵌入式系统,尤其是航空电子系统,如BAE系统鹰的任务控制计算机,通常是实时嵌入式系统。实时系统是不同的,因为它们的正确行为既取决于其操作在逻辑上是否正确,也取决于执行这些操作的时间。开发这些系统的工程师必须能够提供令人信服的证据,证明软件始终在其时间限制内执行。

软件的本质意味着每次执行时,它都可能采用不同的代码路径,从而导致不同的执行时间。即使以相同的方式使用系统,内部状态的差异也可能意味着用户看到的执行时间差异很大。正因为如此,完全有可能在不发现任何时序问题的情况下严格测试软件,然后在实际使用中遇到导致重大时序问题的情况。因此,为了确保系统始终满足其执行时间,有必要建立其最坏情况执行时间(WCET),这也是DO-178B的考虑因素。

查找最坏情况的执行时间

测量是一种通常用来获得实时系统定时行为置信度的方法。为了测量时序,工程师通常将检测点放在他们想要测量的代码段的开头和结尾。这些点通过切换输出端口(通过示波器或逻辑分析仪监控)或通过读取片内定时器并将生成的时间戳记录在存储器中来记录经过的时间。

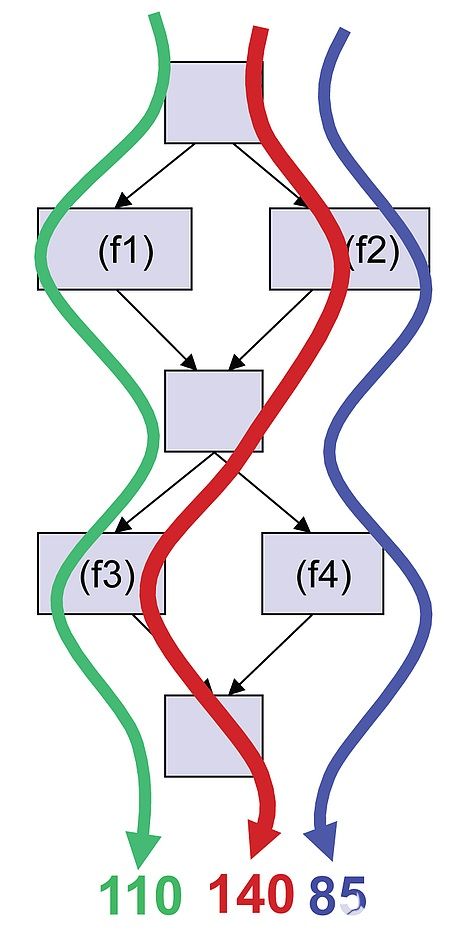

遗憾的是,这些高水位线可能无法反映代码执行所需的最长时间。当测试尚未执行通过代码的最长路径时,就会发生这种情况,如图 1 所示。运行两个测试,如图 1 所示,由绿色路径和蓝色路径表示。从这些测试中观察到的执行时间分别为 110 和 85。尽管这些测试执行了软件中的所有代码,但仍有第三条路径(以红色显示),其执行时间为 140,使其成为最长路径。

图1:执行路径:高水位线可能不反映代码执行可能需要的最长时间。当测试尚未执行通过代码的最长路径时,会发生这种情况。

此示例表明,仅执行所有代码不足以执行最长路径。对于非平凡的代码,很难设计出肯定会使代码沿着最长路径行驶的测试。通过在代码中的每个决策点添加检测点,可以避免这种情况。每当执行检测点时,都会记录其 ID 和时间戳。在系统上运行一系列测试会导致创建计时跟踪。将跟踪中的计时信息与有关代码结构的信息相结合,可以查找有关软件计时行为的信息,包括 WCET 的预测。

对于可能涉及数百万行代码的典型军事应用,手动检测程序将非常费力;此外,通常生成的跟踪数据量使得手动尝试将跟踪数据与程序结构信息相结合变得不可行。幸运的是,程序检测、跟踪处理、将跟踪数据与程序结构信息相结合以及数据挖掘/表示等任务都可以实现自动化。Rapita Systems 的 RapiTime 是一种自动化性能测量和时序分析技术,有助于解决获取以 C、C++ 或 Ada 实现的大型军事嵌入式系统的详细时序信息的挑战。

性能优化

了解 WCET 只是解决方案的一部分:当面临软件组件超出其执行时间预算的问题时,必须采取系统、科学的方法来优化组件的性能。

软件性能优化需要回答三个问题:

优化的最佳位置在哪里?

建议的优化是否在改进?

可以做出多大的改进?

优化的最佳位置在哪里?

在典型的复杂应用中:

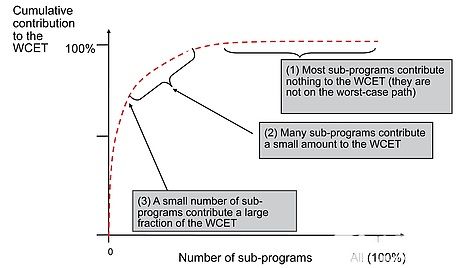

(1)大多数子程序实际上并不处于最坏情况的路径上;它们对最坏情况的执行时间没有任何贡献。优化这些子计划根本不会减少WCET。

(2)许多子计划对WCET的贡献很小,因此不能代表优化的良好候选者。优化这些子计划所付出的努力不会构成对资源的有效利用。

(3)少数子计划占整个WCET的很大一部分(图2)。因此,子程序是优化的潜在候选者。

图2:分项计划对整个WCET的累计贡献

通过检查WCET信息,工程师可以轻松识别相对较少的组件,在这些组件中,优化可能会对整体最坏情况的执行时间产生重大影响。

我在改进事情吗?

有时,试图通过猜测最坏情况的热点在哪里,优化该代码,然后查看效果来缩短分析过程是很诱人的。然而,软件优化的经验告诉我们,即使是对他们的代码有深入了解的高技能软件工程师,如果不访问详细的时间信息,也几乎不可能确定WCET的重要贡献者,从而确定优化的最佳候选者。

通常看起来如此明显 - “一定是进行所有这些浮点计算的代码部分是优化的最佳候选者” - 而实际上,一些看似无害的赋值隐藏了一个几乎占用所有时间的内存副本。这个问题的答案很简单:不要猜测,测量。然后重复测量以量化改进(或缺乏改进)。

可以做出多大的改进?

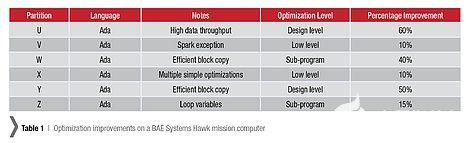

表 1 显示了通过简单的软件优化过程可以获得的最坏情况执行时间的改进水平。这些结果是使用RapiTime技术在BAE系统鹰的任务计算机上提供详细的计时信息来实现的。这些优化导致WCET总体下降了23%。

表 1:BAE系统鹰任务计算机的优化改进

WCET 和性能优化的好处

在军事嵌入式系统修改期间访问自动性能测量和详细的时序分析可以为开发人员提供许多优势:

1. 采用系统科学的方法获取系统定时行为的信心。

2. 有关最坏情况执行时间的详细信息可以快速确定优化的候选对象。

3. 自动测量可以评估候选优化的有效性。

能够进行最佳时序优化意味着避免不必要地过时硬件,并消除放弃计划的新功能或更换硬件并接受早期过时的需求。

审核编辑:郭婷

-

嵌入式开发为什么需要输出调试信息?2023-11-28 3663

-

嵌入式系统外围接口的时序分析与电路设计2023-10-09 648

-

嵌入式系统产品有多可靠?2022-11-16 554

-

测试和分析工具有助于验证和实施军事系统的安全性2022-11-11 1742

-

嵌入式操作系统测试的相关资料分享2021-10-27 1144

-

嵌入式系统在物联网行业有什么应用?2020-04-15 3347

-

物联网嵌入式系统有什么特征?2019-10-31 3104

-

物联网嵌入式系统有什么特点?2019-08-26 2171

-

RF功率测量及控制有助于确保系统安全、高效地运行2019-06-25 2024

-

开发嵌入式系统的选择2019-06-20 880

-

嵌入式系统产品的可靠性2018-08-30 2342

-

可配置混合信号IC和异步状态机有助于优化嵌入式设计2017-05-09 16223

-

现代DAC和DAC缓冲器有助于提升系统性能、简化设计2016-01-04 924

-

嵌入式系统优先级反转问题的分析2006-03-11 1223

全部0条评论

快来发表一下你的评论吧 !