SAR型ADC的RC滤波器设计

模拟技术

描述

本文是ADI智库SAR型ADC课程的笔记的第一篇,内容为SAR型ADC的模拟输入模型、反冲电压,以及如何设计RC滤波器。这个系列课程应用性比较强,因为工作中经常会用到SAR 型ADC芯片,所以特别做了笔记,加深理解。另外,课程中对于公式的推导有些粗略,我这里会比较详细的列出来推导过程;其实就是一阶RC电路的暂态分析,看来把电路基础学好是非常必要的。

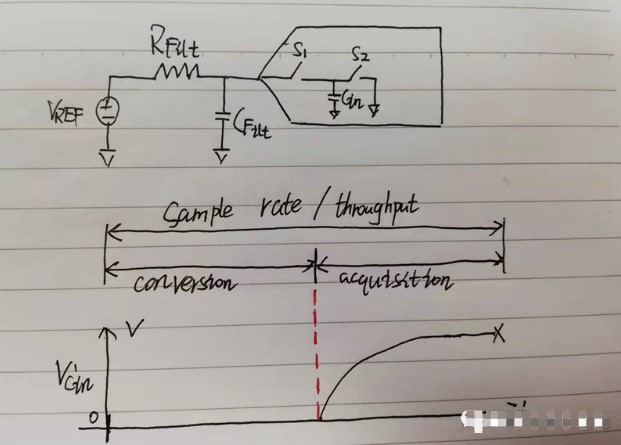

随着此类ADC的精度和采样率不断提高,因此驱动此类ADC的难度也越来越大。图1是SAR型ADC的模拟输入模型,不必管ADC内部的具体情况;它告诉了我们输入节点到底发生了什么。为了简化数学,模拟做了适当的简化,选择最经典的最差情形建立条件:S1和S2是两个开关,转换周期内S2是闭合的,所以此时Vcin=0V,这样采集周期开始时,Vcin从0V开始指数上升。

我们经常会看到RC滤波电路与ADC输入端相连,加滤波器的目的简单来说,限制了下游信号的带宽,因此信号链和驱动器(即RC滤波器前级电路)的噪声都会被RC滤波器限制了带宽,减小了噪声。但是,这个RC滤波器也有副作用,它将导致电荷重新分配,减小电压建立的速度。反冲电压也是因为电荷在两个电容上重新分配出现的。

图1(SAR型ADC的模拟输入模型)

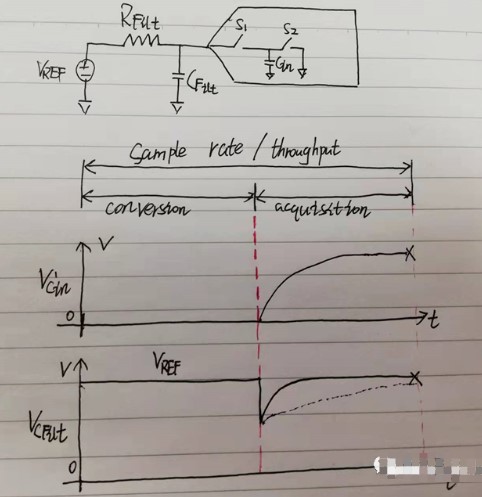

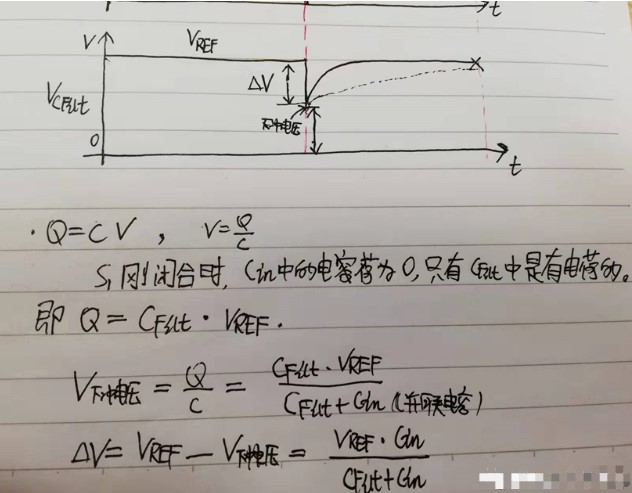

下面我们看下如何计算反冲电压,见图2。转换周期即S1断开S2闭合这一段时间的电压为Vref,采集周期刚开始即S1闭合S2断开后,ADC输入端的电压从图中可看出,它先被拉低,尔后呈指数上升。

图2

我们可通过电荷守恒(流入的总电荷等于流出的总电荷)计算出反冲电压值。详细见图3。从中我们就能明白为什么RC滤波器需要设计,而不是随便选阻容了。其实原因非常直观,因为采集周期开始时会有一个很大的干扰,随后电压呈指数上升,如果电压在采集周期结束都没有完成建立,——甚至发生震荡——那么ADC采集到的电压精度是不准确的。图3中虚线的电压就没有在采集周期结束前完成建立,当然画得不太准确。另外,SAR型ADC具有零延迟的特点,不管采样电压转换成什么样的输出,都会在下一个周期提供给ADC输出端;所以SAR型ADC的RC滤波器设计需要简单注意下。

图3

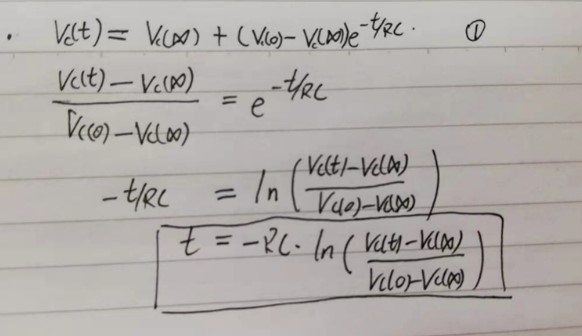

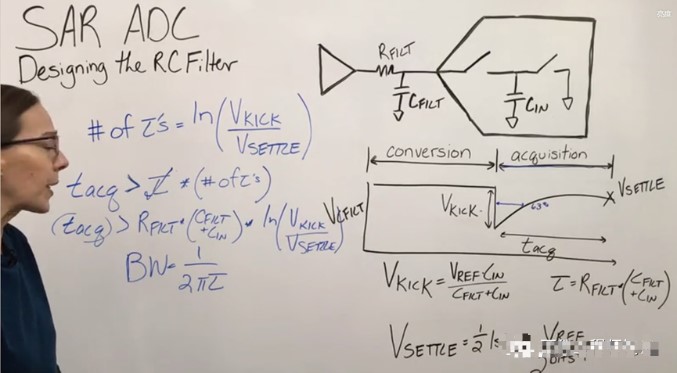

最后就是RC滤波器的设计了。首先看下RC电路的相关公式,因为只有知道它,才能明白课程中的推导是怎么来的,详细见图4。图4中的圈1公式非常值得记住,因为不管是电容电压上升还是下降,它都是适用的。有的课本是把上升和下降的公式分为两个,觉得一个的更好。它的推导是从微分方程推出来的。更多的详细见课本,如时间常数(如电容电压上升情况,一个时间常数,电容电压上升至总输入电压的约63%)等。

图4

课程中给出的公式见图5,它将前面的一切都整合到了一起。根据一个有效的经验法则,我们希望在此ADC分辨率的1/2 LSB的范围内完成建立,这就是Vsettle的来历,结合图4,它实际上就是V(∞)-V(t);Rfilt*(Vfilt+Cin)为时间常数;Vkick为V(0)即电容充电的起始电压。

通常会在数据手册中找到固定的转换周期的数值,那么用采样速度减去这个固定的转换周期,就是采集时间了。看ADC加上设计好的RC滤波器后是否能在采集周期结束前完成采集电压的建立,也就是Tacq大于我们计算出的建立时间。

图5

RC滤波器的设计存在一种反向关系,带宽太小可以减小噪声,但是会延长建立时间;反之亦然。总之,就像找到一个神奇的数值,在带宽和建立时间达到某个平衡。另外,RC电路的设计也是有考虑的,固定的截止频率下,电阻可以大点,它的优点是可以减小功耗,它的问题是增大了热噪声,或者ADC的输入偏置电流加在电阻上如果阻值太大会有直流误差的。

本文为理解SAR型ADC提供了一个很好的框架。更多详细见该课程,课程中有实际仿真测试等。另外,需要注意的是,这里假设了驱动电压是理想电压源,实际电路中的驱动源往往是运放等,它会带来一些别的影响。所以课程中比较推荐用他们的工具进行仿真。

-

SAR ADC采样外围滤波电路配置电路计算原理2026-03-31 484

-

用RC低通滤波的话,转折频率是可以满足,但是RC滤波器中,充电时间常数RC能满足△-∑型ADC的采样时间要求吗?2025-01-16 478

-

精密SAR模数转换器的前端放大器和RC滤波器的设计2023-11-24 645

-

SAR型ADC的模拟输入模型、反冲电压和RC滤波器计算2023-09-14 5136

-

如何选择saradc前端的rc滤波器?2023-09-13 1777

-

高性能全集成SAR型ADC2023-03-31 2132

-

π型滤波器的工作原理及作用2023-02-16 17672

-

为SAR ADC选择合适的放大器和RC滤波器资料下载2021-04-28 1254

-

如何设计RC滤波器及运算放大器的选择2021-01-16 5655

-

如何选择SAR ADC前端的RC滤波器2019-08-21 6432

-

SAR型ADC应用2019-08-06 4226

-

RC无源低通滤波器设计问题?2019-01-08 4146

-

SAR型ADC前端RC滤波器设计2018-11-13 5463

-

精密SAR模数转换器的前端放大器和RC滤波器设计2016-01-07 1234

全部0条评论

快来发表一下你的评论吧 !