【高云半导体Combat开发套件试用体验】RISC-V处理器蜂鸟E203在高云FPGA平台上的移植实践

描述

本文来源电子发烧友社区,作者:yuzhiwen1986, 帖子地址:https://bbs.elecfans.com/jishu_2295853_1_1.html

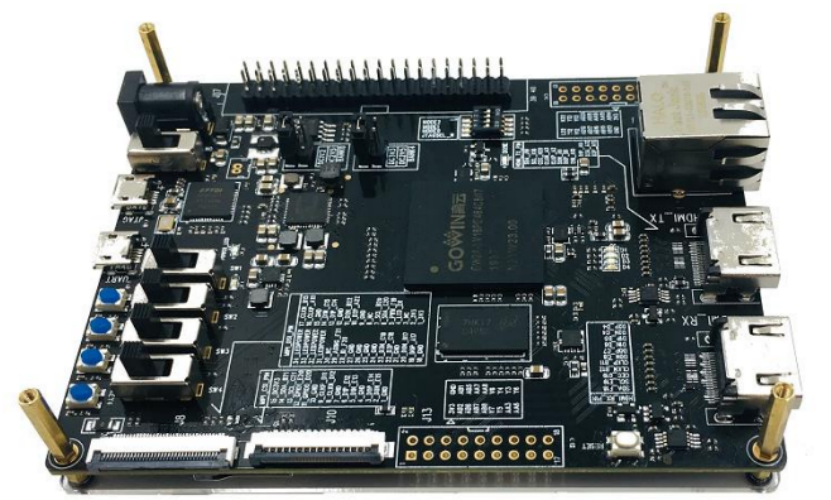

高云FPGA 平台介绍

Combat开发套件是以高云半导体 GW2A 系列 FPGA 产品为核心,是高云半导体晨熙®家族第一代产品,内部资源丰富,具有高性能的 DSP资源,高速LVDS 接口以及丰富的 BSRAM 存储器资源,这些内嵌的资源搭配精简的FPGA 架构以及 55nm 工艺使 GW2A 系列 FPGA 产品适用于高速低成本的应用场合。

外设接口管脚说明

本次项目中用到的I/O口如表下描述

| 信号名 | FPGA管脚序号 | BANK | 描述 | I/O电平 |

|---|---|---|---|---|

| SYS_CLK | M19 | 2 | 50Mhz有源晶振 | 3.3V |

| FPGA_RST | AB3 | 5 | 复位,低电平有效 | 3.3V |

| LED1 | U17 | 3 | LED指示灯1 | 1.5V |

| LED2 | U19 | 3 | LED指示灯2 | 1.5V |

| LED3 | U18 | 3 | LED指示灯3 | 1.5V |

| LED4 | T17 | 3 | LED指示灯4 | 1.5V |

| QSPI_DQ[0] | ||||

| QSPI_DQ[0] | ||||

| QSPI_DQ[0] | ||||

| QSPI_DQ[0] | ||||

| QSPI_CS | ||||

| QSPI_SCK | ||||

| MCU_TCK | C22 | 2 | ||

| MCU_TDI | F22 | 2 | ||

| MCU_TMS | J22 | 2 | ||

| MCU_RST | V14 | 4 | ||

| MCU_WAKE_UP | R18 | 3 | 按键3唤醒MCU | 1.5V |

| PMU_PADRST | T19 | 3 | 按键2复位PMU | 1.5V |

| PMU_PADRST |

时钟复位电路

开发板为 FPGA 提供了一个 50MHz 有源晶振,连接到了全局时钟引脚。

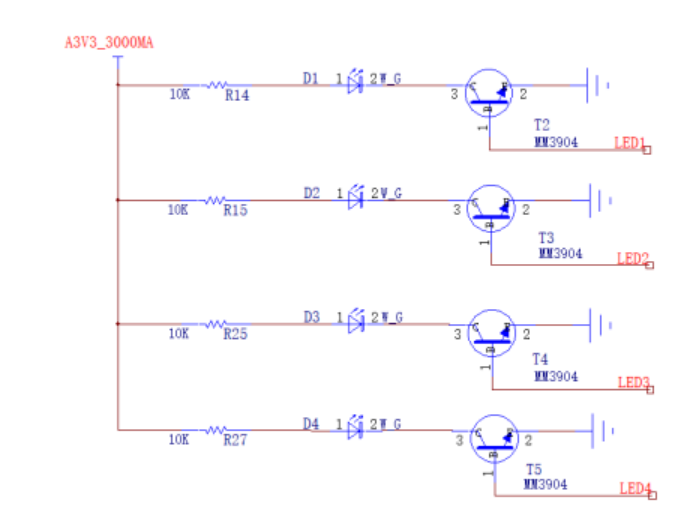

LED指示灯

开发板中有 4 个绿色 LED 灯,用户可通过 LED 灯显示所需状态。可通过以下方式对 LED 灯进行测试: 当 FPGA 对应管脚输出信号为逻辑高电平时,LED 被点亮;当输出信号为低电平时,LED 熄灭

MCU 唤醒电路

开发板有4个按键开关,用户可以通过手动控制对应FPGA管脚输入低电平,触发MCU唤醒。本项目中使用KEY2/3/4作为复位和唤醒电路,电路图如下

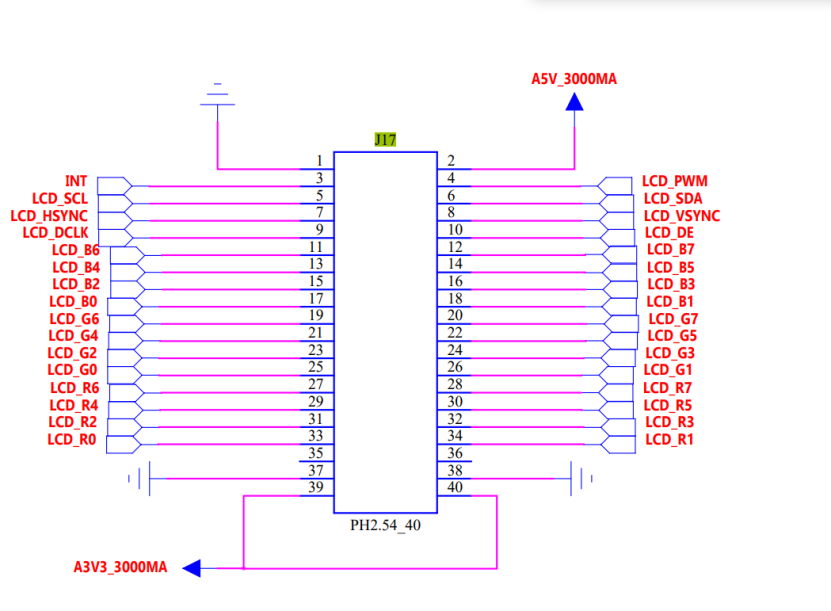

复用J17作为MCU的JTAG调试接口

LCD_PWM ->C22 -> MCU_TCK

LCD_SDA ->F22 ->MCU_TDI

LCD_VSYNC->G22 -> MCU_TDO

LCD_DE -> J22 ->MCU_TMS

LCD_B7 ->V14 -> MCU_RST

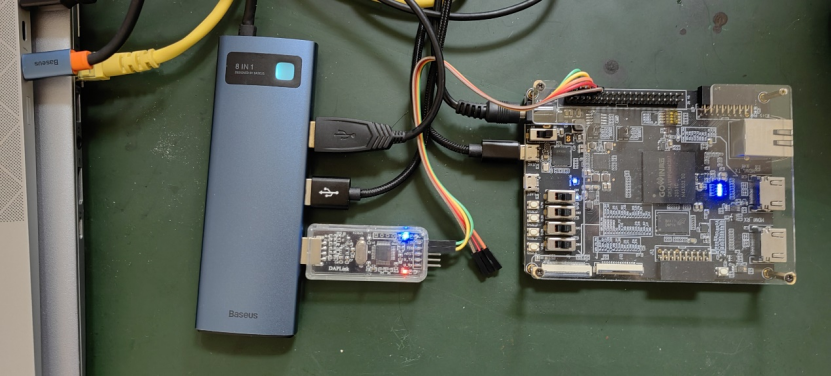

FPGA 原型平台和MCU调试仿真器

FPGA 原型主要分为两部分:FPGA 开发板,和调试器。接下来章节分别予以介绍。完整的 FPGA 开发板原型(包括 FPGA 开发板和MCU调试器)如下图所示:

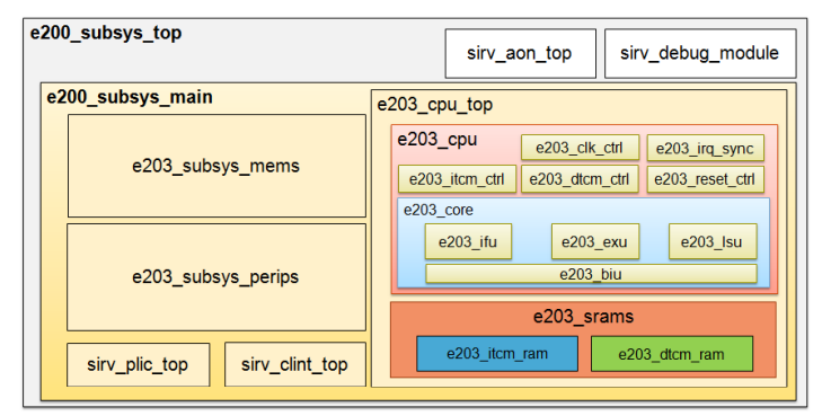

蜂鸟E203开源SoC

对于一个处理器核,还需要配套的 SoC 才能具备完整的功能。蜂鸟 E203 内核不仅仅完全开源了 Core的实现,还搭配完整的开源 SoC 平台,请参见《蜂鸟 E203 开源 SoC 简介》了解更多 SoC 的介绍与信息。蜂鸟 E203 开源 SoC 的Subsys 模块的款图如下:

Linux平台环境搭建

这里以Ubuntu系统为例进行说明。

代码下载和基本环境配置

- 下载E203源码

git clone https://github.com/SI-RISCV/e200_opensource.git

- 下载iverilog源码

`git clone https://github.com/steveicarus/iverilog.git

- 切换到v11分支(必须用V11或以上的版本)

git checkout v11-branch

- 安装依赖

sudo apt-get install autoconf gperf flex bison build-essential

- 编译、安装iverilog和vvpsh autoconf.sh

./configure

make

make install

- 创建python软链接

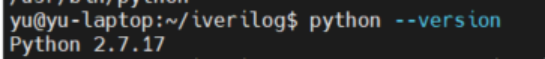

查看一下python的版本,我的还是Python2,新更新一下:

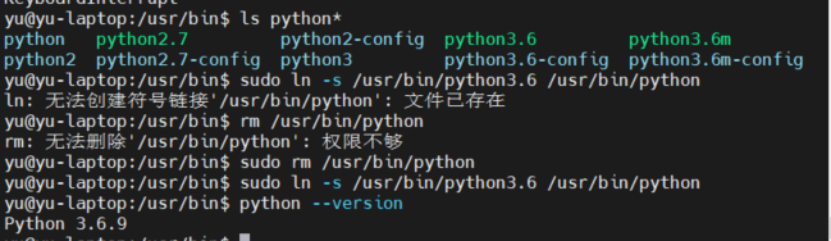

查看一下/usr/bin目录下面有哪些版本,如果有python3版本就创建一个新的软连接

sudo ln -s /usr/bin/python3.8 /usr/bin/python

其中/usr/bin/python3.8对应你实际安装的python版本。7. 安装gtkwave

sudo apt-get install gtkwave

HBird-E-SDK 下载和配置1. 将 HBird-E-SDK 项目下载到本机 Linux 环境中,使用如下命令:

git clone [https://github.com/SI-RISCV/hbird-e-sdk](https://github.com/SI-RISCV/hbird-e-sdk)

- 由于编译软件程序需要使用到GNU 工具链,假设使用完整的 riscv-tools 来自己编译 GNU 工具链则费

时费力,因此本文档推荐使用预先已经编译好的 GCC 工具链。我们已经将工具链上传至网盘,网盘具体地址记载于

hbird-e-sdk 项目(https://github.com/SI-RISCV/hbird-e-sdk)的 prebuilt_tools 目录下的 README

中,用户可以在网盘中的“RISC-V SoftwareTools/RISC-V_GCC_201801_Linux”目录下载压缩包gnu-mcu-eclipse-riscv-none-gcc-7.2.0-2-20180111-2230-centos64.tgz和gnu-mcu-eclipse-openocd-0.10.0-6-20180112-1448-centos64.tgz,然后按照如下步骤解压使用(注意:上述链接网盘上的工具链可能会不断更新,用户请注意自行判断使用最新日期的版本,下列步骤仅为特定版本的示例)。

cp gnu-mcu-eclipse-riscv-none-gcc-7.2.0-2-20180111-2230-centos64.tgz ~/

cp gnu-mcu-eclipse-openocd-0.10.0-6-20180112-1448-centos64.tgz ~/

//将两个压缩包均拷贝到用户的根目录下

cd ~/

tar -xzvf gnu-mcu-eclipse-riscv-none-gcc-7.2.0-2-20180111-2230-centos64.tgz

tar –xzvf gnu-mcu-eclipse-openocd-0.10.0-6-20180112-1448-centos64.tgz

// 进入根目录并解压上述两个压缩包,解压后可以看到一个生成的 gnu-mcu-eclipse 文件夹

cd ~/hbird-e-sdk // 进入 hbird-e-sdk 目录文件夹

mkdir ~p work/build/openocd/prefix

// 在 hbird-e-sdk 目录下创建上述这个 prefix 目录 cd work/build/openocd/prefix // 进入到 prefix 该目录

ln –s ~/gnu-mcu-eclipse/openocd/0.10.0-6-20180112-1448/bin bin

// 将用户根目录下解压的

OpenOCD 目录下的 bin 目录作为软链接链接到该

prefix 目录下

cd ~/hbird-e-sdk // 进入 hbird-e-sdk 目录文件夹

mkdir -p work/build/riscv-gnu-toolchain/riscv32-unknown-elf/prefix/

// 在 hbird-e-sdk 目录下创建上述这个 prefix 目录

cd work/build/riscv-gnu-toolchain/riscv32-unknown-elf/prefix

// 进入到 prefix 该目录

ln -s ~/gnu-mcu-eclipse/riscv-none-gcc/7.2.0-2-20180111-2230/bin bin

// 将用户根目录下解压的 GNU

Toolchain 目录下的 bin 目录作为软链接链接到

// 该 prefix 目录下 注意:此步骤完成工具链的安装之后,后续开发程序示例无需重复执行此步骤。

Verilog 仿真测试

使用E203 源代码运行基于 Verilog 的仿真测试程序,可以使用如下步骤进行。

**步骤一:**准备好自己的电脑环境,可以在公司的服务器环境中运行,如果是个人用户,推荐如下配置:

(1)本项目使用 Ubuntu 18操作系统

(2)由于 Linux 操作系统的版本众多,推荐使用 Ubuntu 18.04 版本的 Linux 操作系统有关如何安装 Ubuntu 操作系统本文不做介绍,有关 Linux 的基本使用本文也不做介绍,请用户自行查阅资料学习。

**步骤二:**将 e200_opensource 项目下载到本机 Linux 环境中,使用如下命令:

git clone https://github.com/SI-RISCV/e200_opensource.git

**步骤三:**编译 RTL 代码,使用如下命令:

cd /vsim

// 进入到 e200_opensource 目录文件夹下面的 vsim 目录。

make install CORE=e203

// 运行该命令指明需要为 e203 进行编译,该命令会在 vsim 目录下生成一个 install

// 子文件夹,在其中放置所需的脚本,且将脚本中的关键字设置为 e203。

make compile

// 编译 Core 和 SoC 的 RTL 代码

// 注意:在此步骤之中,编译 Verilog 代码需要使用到仿真器工具,在 github 上的 Makefile

// 中使用的是免费的 iverilog 工具,如果需要使用商业 EDA 的用户需要自行修改 Makefile 中的

// 对于免费的 iverilog 工具如何安装请用户在互联网上自行搜索。

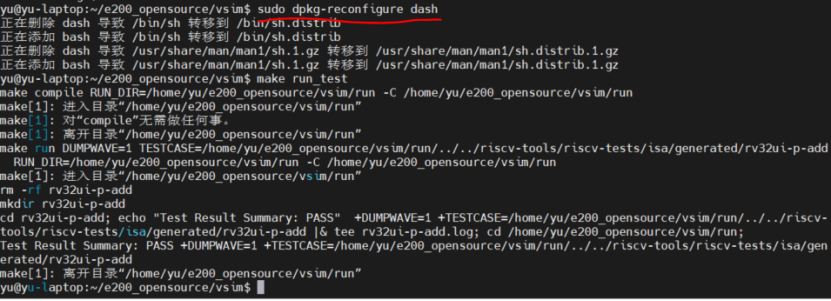

步骤四 :运行默认的一个 testcase(测试用例),使用如下命令:

make run_test

注意:在此步骤中,运行仿真需要使用仿真器工具,在 github 上的 Makefile 中此部分空缺,实际运行的是”echo PASS”命令打印一个虚假的 PASS 到 log 文件中。用户需要使用真正的仿真器运行仿真得到真实的运行结果。

注意:make run_test 将执行 e200_opensource/riscv-tools/

riscv-tests/isa/generated 目录中的一个默认 testcase,如果希望运行所有的

回归测试,请参见步骤五。

当用make去编译Makefile文件的时候,如果有出现/bin/sh:Syntax error: 的错误时候,一般是当前默认的shell不正确的原因首先可以用命令ls -l /bin/sh 看看当前默认的是什么shell,Ubuntu一般默认为bash再用要修改默认的shell,可以采用命令sudo dpkg-reconfigure dash。会出现如下窗口,然后选择否。

步骤五 :运行回归(regression)测试集,使用如下命令:

make regress_run

注意:这使用 e200_opensource/ riscv-tools/riscv-tests/isa/generated 目录中 testcases,逐个的运行 testcase。

步骤六 :查看回归测试结果: make

regress_collect // 该命令将收集步骤五中运行的测试集的结果,将打印若干行的结果,每一行对应一个测 // 试用例,如果那个测试用例运行通过,那一行则打印的 PASS,如果运行失败,那一行则 // 打印的 FAIL。如图 所示

代码编译下载

工程导入

在Opensource

目录下FPGA文件夹创建一个新的文件夹gowin,

将相关的rtl文件拷入,并对top文件进行的对应修改,文件目录如下图:

打开gowin软件,创建工程,选择好对应的器件并导入文件。导入具体软件操作说明参见SUG100-1.7_Gowin云源软件用户指南,本项目中导入之后界面如下:

程序编译和下载

修改完程序之后保存点击Process 点击Place&Route编译,编译通过之后前面会出现绿

.编译通过后双击Program Device弹出下载窗口,点击开始下载

运行和调试软件

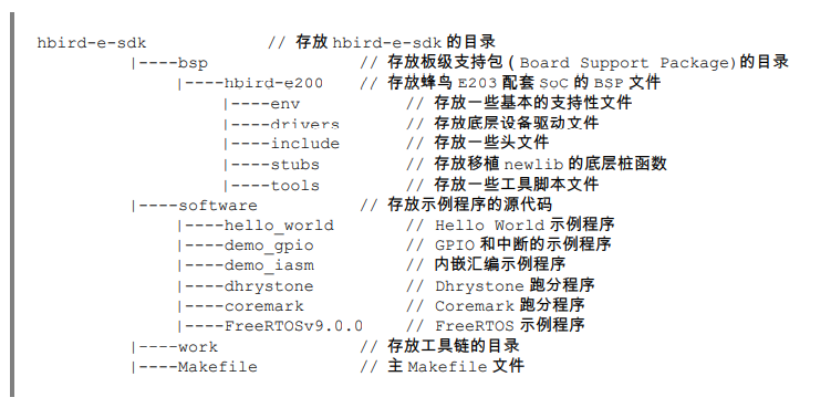

HBird-E-SDK介绍

HBird-E-SDK 并不是一个软件,它本质上是由一些 Makefile、板级支持包(Board Support Package,

BSP)、脚本和软件示例组成的一套开发环境。HBird-E-SDK 基于 Linux 平台,使用标准的 RISC-V GNU

工具链对程序进行编译,使用 OpenOCD+GDB 将程序下载到硬件平台中并进行调试。

HBird-E-SDK 代码结构

编译 demo_gpio 示例程序,使用如下命令: cd // 进入 hbird-e-sdk 目录文件夹 make dasm PROGRAM=demo_gpio NANO_PFLOAT=0 //注意:由于 Demo_GPIO 程序的 printf 函数不需要输出浮点数,上述选项 NANO_PFLOAT=0 指明 newlib-nano 的 printf 函数无需支持浮点数,请参见《RISC-V 架构与嵌入式开发快速入门》第 11 章了解相关信 息。

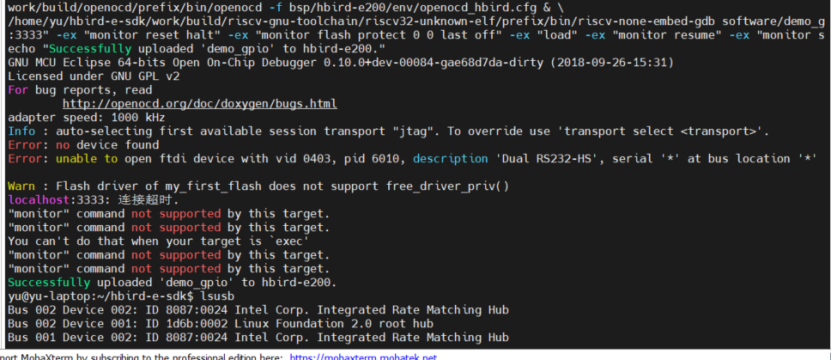

将编译好的

demo_gpio 程序下载至 FPGA 原型开发板中,使用如下命令:

很遗憾,我这里因为使用的下载器有问题,最终还是没有成功下载MCU bin文件。

但是基本的流程走通了。时间有限试用期已经结束了。期待下一次还会有继续!

-

如何把蜂鸟E203的核移植在N4DDR平台上?2025-11-10 1498

-

RISC-V 蜂鸟E203平台搭建2025-10-28 273

-

【高云半导体Combat开发套件试用体验】RISC-V处理器蜂鸟E203在高云FPGA平台上的移植实践2022-07-26 293766

-

【高云半导体Combat开发套件试用体验】基础测评GPIO+串口测评2022-07-04 3551

-

【高云半导体Combat开发套件试用体验】开箱测试2022-06-23 2530

-

【高云半导体Combat开发套件试用体验】+一次开箱2022-06-12 16969

-

【高云半导体Combat开发套件试用体验】完整开箱报告2022-06-05 2575

-

【高云半导体Combat开发套件试用体验】+开箱2022-06-01 2044

-

【RISC-V专题】高云半导体Combat开发套件首发试用#RISC-V开发板评测硬声评测 2022-04-21

-

【RISC-V专题】高云半导体Combat开发套件首发试用2022-04-15 7171

-

开源Hummingbirdv2 E203 RISC-V处理器内核和SoC项目2022-03-17 1592

-

高云半导体携带RISC-V FPGA设计易用性方案出席RISC-V论坛2018-11-17 9670

全部0条评论

快来发表一下你的评论吧 !