【高云半导体Combat开发套件试用体验】基础测评GPIO+串口测评

描述

本文来源电子发烧友社区,作者:mameng, 帖子地址:https://bbs.elecfans.com/jishu_2291163_1_1.html

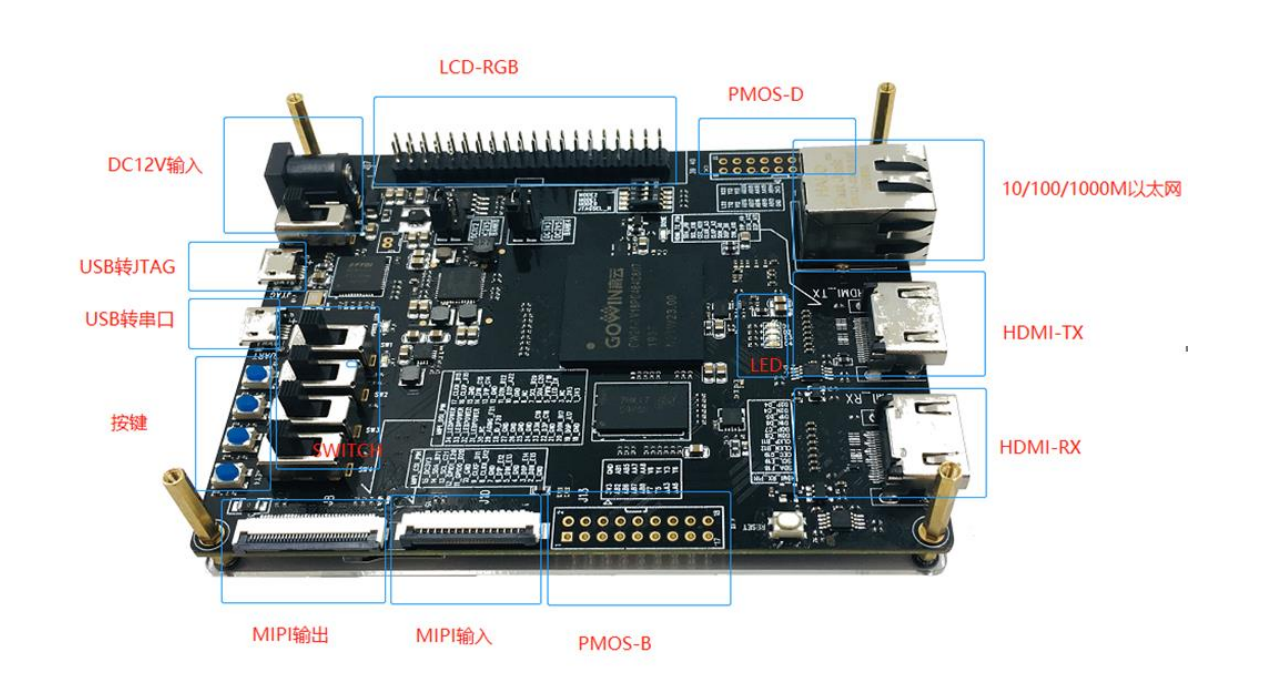

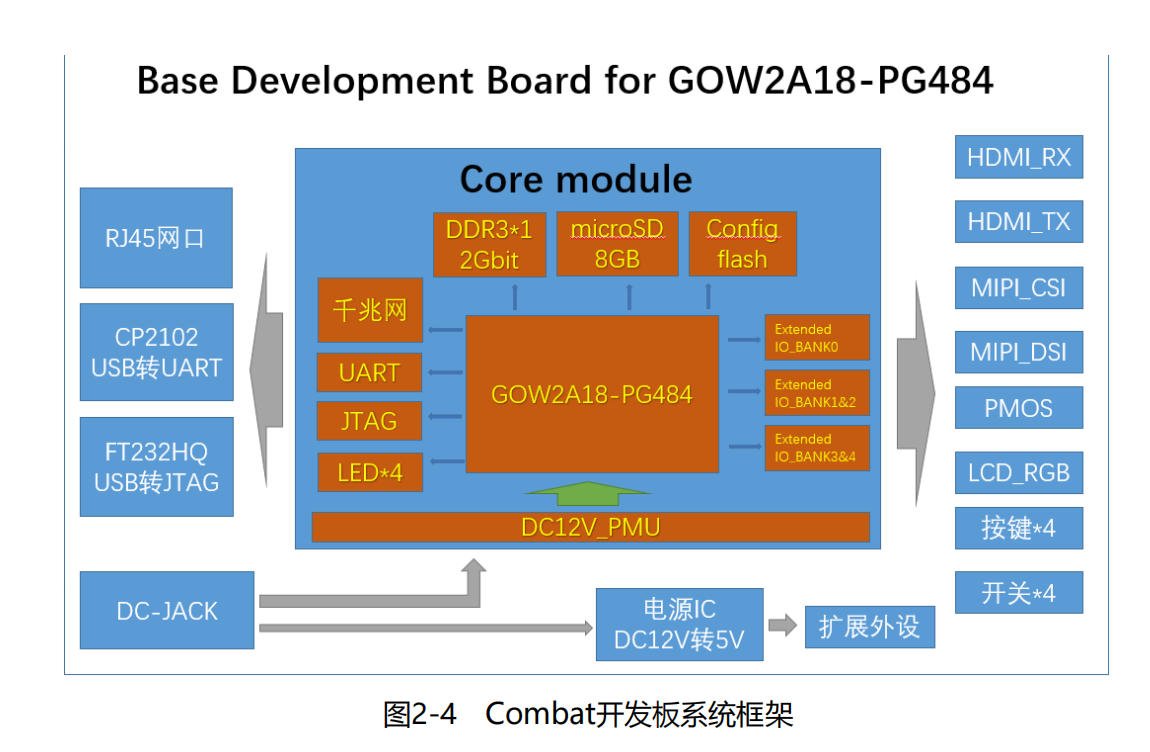

Combat开发套件是以高云半导体 GW2A 系列 FPGA 产品为核心,是高云半导体晨熙®家族第一代产品, 内部资源丰富,具有高性能的 DSP 资源,高速 LVDS 接口以及丰富的 BSRAM 存储器资源,这些内嵌的资源搭配精简的 FPGA 架构以及 55nm 工艺使 GW2A 系列 FPGA 产品适用于高速低成本的应用场合Combat开发套件对外扩展多种接口,部分接口支持功能复用,方便用户自定义扩展并进行各类视频,工业应用等验证。完全自主研发的Gowin云源软件能够完成Combat板卡的综合、布局、布线、产生数据流文件及下载文件等FPGA开发全流程支持。

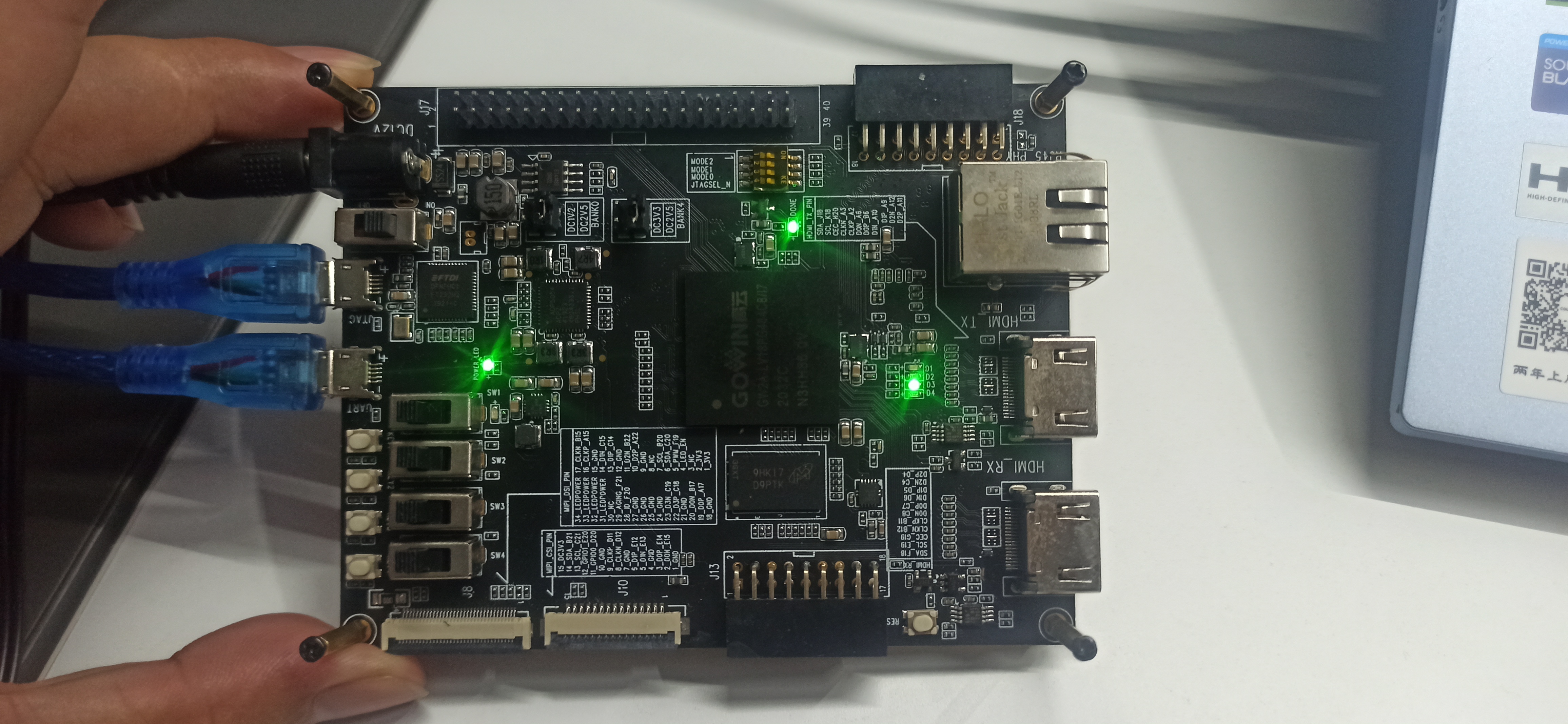

开发板图片:

系统框架:

高云半导体 GW2A 系列 FPGA 产品是高云半导体晨熙®家族第一代产品, 内部资源丰富,具有高性能的 DSP 资源,高速 LVDS 接口以及丰富的 B-SRAM 存储器资源,这些内嵌的资源搭配精简的 FPGA 架构以及 55nm 工艺使 GW2A 系列 FPGA 产品适用于高速低成本的应用场合。可以对标Altera Cyclone II 系列的 EP2C8。

高云半导体 GW2A 系列 FPGA 产品(车规级)是高云半导体晨熙®家族第一代产品,内部资源丰富,具有高性能的 DSP 资源,高速 LVDS 接口以及丰富的 BSRAM 存储器资源,这些内嵌的资源搭配精简的 FPGA 架构以及55nm工艺使GW2A系列FPGA产品(车规级)适用于高速低成本的应用场合。

高云半导体 GW2AR 系列 FPGA 产品是高云半导体晨熙®家族第一代产品,是一款系统级封装芯片,在GW2A系列基础上集成了丰富容量的SDRAM存储芯片,同时具有 GW2A 系列高性能的 DSP 资源,高速 LVDS 接口以及丰富的 B-SRAM 存储器资源,这些内嵌的资源搭配精简的 FPGA 架构以及55nm 工艺使 GW2AR 适用于高速低成本的应用场合。

高云半导体 GW2AN 系列 FPGA 产品是高云半导体晨熙®家族第一代具有非易失性的 FPGA 产品,内部资源丰富,高速 LVDS 接口以及丰富的BSRAM 存储器资源、NOR Flash 资源,这些内嵌的资源搭配精简的 FPGA架构以及 55nm 工艺使 GW2AN 系列 FPGA 产品适用于高速低成本的应用场合。

高云半导体 GW2ANR 系列 FPGA 产品是高云半导体晨熙®家族第一代产品,是一款系统级封装、具有非易失性的 FPGA 产品,在 GW2A 系列基础上集成了丰富容量的 SDRAM 及 NOR Flash 存储芯片,同时具有 GW2A系列高性能的 DSP 资源,高速 LVDS 接口以及丰富的 B-SRAM 存储器资源,这些内嵌的资源搭配精简的 FPGA 架构以及 55nm 工艺使 GW2ANR 适用于高速低成本的应用场合。

高云半导体推出云源软件设计系统,专为高云半导体的 FPGA 芯片而配套的集成电路设计与实现工具。云源系统针对高云 FPGA 芯片构架的低功耗、低成本特点进行了全面的优化设计,覆盖了从 HDL 电路功能描述到 FPGA 位流(bit stream)的完整流程,包括了优化设计、自动设计、图形交互设计等功能,具有性能优越、容易使用等特点。Synopsys 为高云提供前 SynplifyPro 高云版端软件软件,是中国唯一由新思授权的 FPGA 前端软件,具有 SynplifyPro 的所有功能,可针对高云芯片架构进行优化,覆盖 FPGA 设计的全流程,从 RTL 综合到产生 FPGA 位流(bit stream),支持高云 FPGA 芯片所有功能,支持高速输入输出模块和嵌入式存储器模块、DSP,支持 10 万宏单元(100K LUTs)设计规模。在后端软件方面,高云半导体推出星核计划,以建立 FPGA 的生态系统和 IP 核的资源库,将与高校、科研机构、企业联动,形成联合研发群体,实现知识产权共享,促进产业链发展。作为该计划的发起人,将从软件工具、实验板和芯片层面为研发环境提供便利。

高云云EDA软件;

详细说明参考B 站视频讲解 :

https://www.bilibili.com/video/BV1FA411J7GF?spm_id_from=333.999.0.0

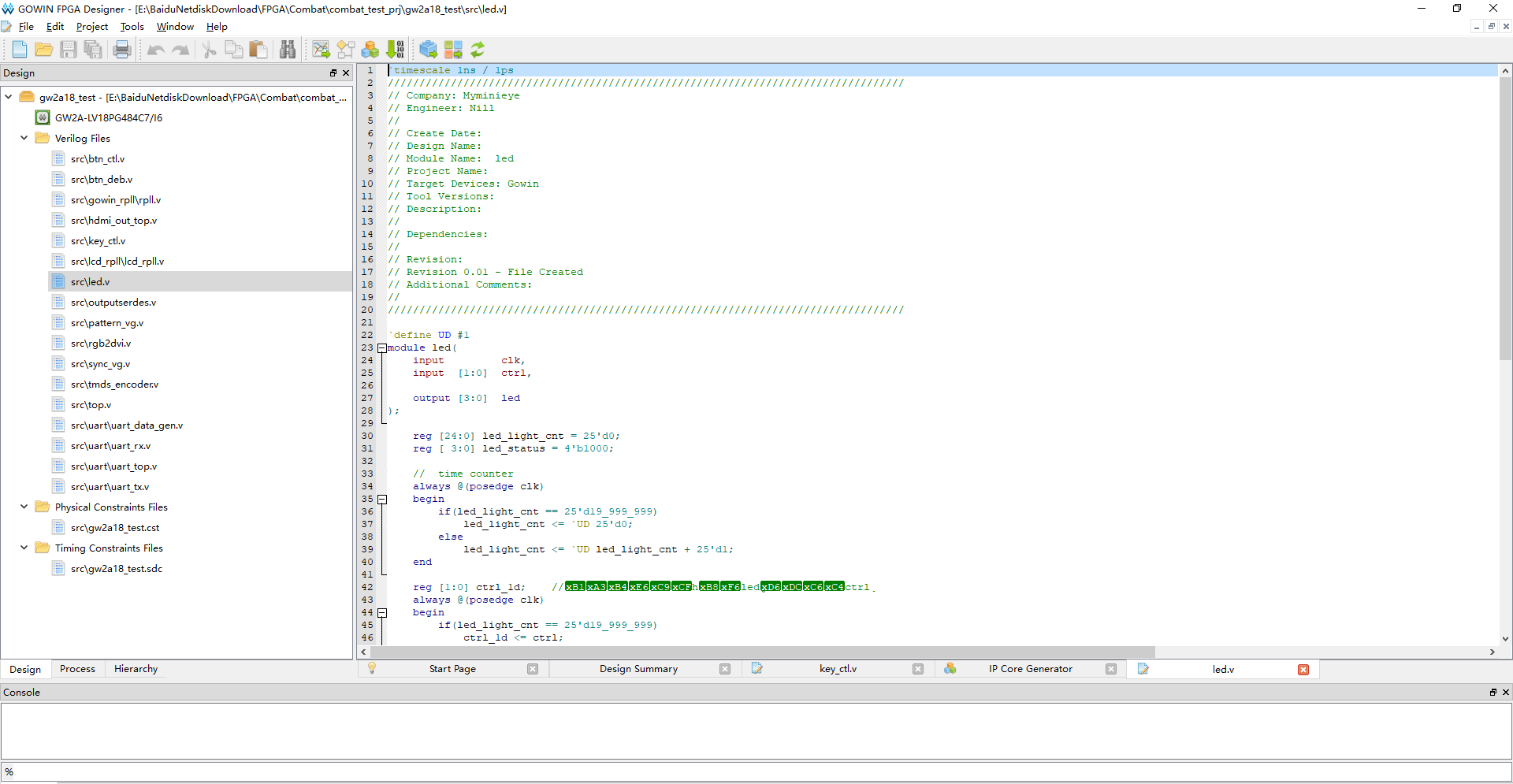

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company: Myminieye

// Engineer: Nill

//

// Create Date:

// Design Name:

// Module Name: led

// Project Name:

// Target Devices: Gowin

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

`define UD #1

module led(

input clk,

input [1:0] ctrl,

output [3:0] led

);

reg [24:0] led_light_cnt = 25'd0;

reg [ 3:0] led_status = 4'b1000;

// time counter

always @(posedge clk)

begin

if(led_light_cnt == 25'd19_999_999)

led_light_cnt <= `UD 25'd0;

else

led_light_cnt <= `UD led_light_cnt + 25'd1;

end

reg [1:0] ctrl_1d; //������һ��led״̬���ڵ�ctrlֵ

always @(posedge clk)

begin

if(led_light_cnt == 25'd19_999_999)

ctrl_1d <= ctrl;

end

// led status change

always @(posedge clk)

begin

if(led_light_cnt == 25'd19_999_999)//0.5s ����

begin

case(ctrl)

2'd0 : //�Ӹ�λ����λ��led��ˮ��

begin

if(ctrl_1d != ctrl)

led_status <= `UD 4'b1000;

else

led_status <= `UD {led_status[0],led_status[3:1]};

end

2'd1 : //�ӵ�λ����λ��led��ˮ��

begin

if(ctrl_1d != ctrl)

led_status <= `UD 4'b0001;

else

led_status <= `UD {led_status[2:0],led_status[3]};

end

2'd2 : //�ӵ�λ����λ������Ƶĸ���

begin

if(ctrl_1d != ctrl || led_status == 4'b1111)

led_status <= `UD 4'b0000;

else

led_status <= `UD {led_status[2:0],1'b1};

end

2'd3 : //�Ӹ�λ����λ�������Ƶĸ���

begin

if(ctrl_1d != ctrl || led_status == 4'b0000)

led_status <= `UD 4'b1111;

else

led_status <= `UD {1'b0,led_status[3:1]};

end

endcase

end

end

assign led = led_status;

endmodule

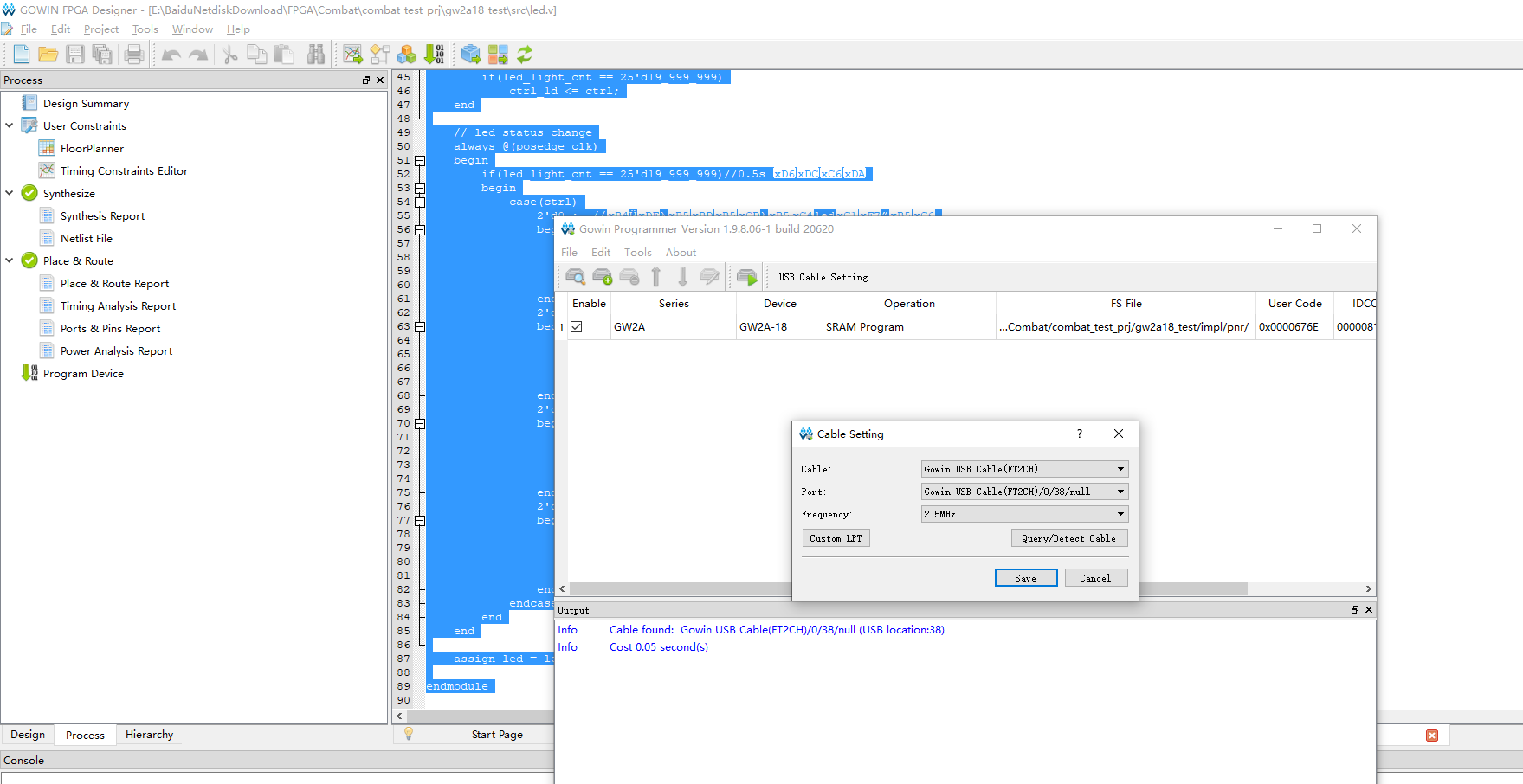

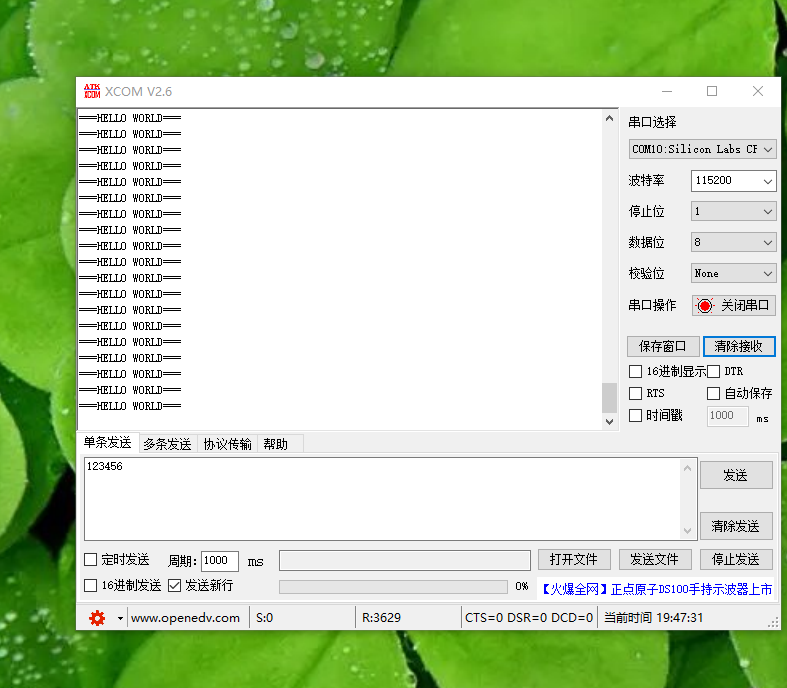

编译下载:

完美!

-

【高云半导体Combat开发套件试用体验】RISC-V处理器蜂鸟E203在高云FPGA平台上的移植实践2022-11-10 5216

-

【高云半导体Combat开发套件试用体验】基础测评GPIO+串口测评2022-07-04 3551

-

【高云半导体Combat开发套件试用体验】Combat demo调试运行及小建议2022-07-01 3830

-

【高云半导体Combat开发套件试用体验】开箱测试2022-06-23 2530

-

【高云半导体Combat开发套件试用体验】开箱及开发准备工作2022-06-20 3384

-

【高云半导体Combat开发套件试用体验】+一次开箱2022-06-12 16969

-

【高云半导体Combat开发套件试用体验】完整开箱报告2022-06-05 2574

-

【高云半导体Combat开发套件试用体验】之开箱测试2022-06-01 3627

-

【RISC-V专题】高云半导体Combat开发套件首发试用#RISC-V开发板评测硬声评测 2022-04-21

-

【RISC-V专题】高云半导体Combat开发套件首发试用2022-04-15 7170

-

【Combat FPGA开发板】开发板简介+原理图+使用手册2021-04-22 3958

全部0条评论

快来发表一下你的评论吧 !