【高云半导体Combat开发套件试用体验】FPGA基本语法及Combat使用小技巧

描述

本文来源电子发烧友社区,作者:james, 帖子地址:https://bbs.elecfans.com/jishu_2288839_1_1.html

FPGA常用的基本类型wire、reg和parameter。

打开APP阅读更多精彩内容

FPGA常用的基本类型wire、reg和parameter。

wire:线网型数据,表示硬件单元之间的物理连线,是verilog中默认的数据类型,由assign操作关键字赋值,可以是一个赋值表达式,assign关键字是实现组合逻辑操作的一种主要描述方式。

reg:寄存器型数据,会保持数据原有的值,直到被改变,无符号数。

parameter:表示常量,只能赋值异常。

所有操作都是在module中完成,module/endmodule表示模块的开始与结束,模块的参数由input/output信号组成。

在模块中,assign只能实现组合逻辑赋值,且一个assign后面只能跟一个赋值表达式,always既能实现组合逻辑赋值,又能实现时序逻辑赋值操作,且可以包括多条赋值表达式,多条赋值表达式应位于begin/end中间。在always中被赋值的信号应该定义为reg类型。

FPGA其中很多操作符及其用法和C语言有很多通之处,有时间大家可以系统性的了解一下verilog的语法。

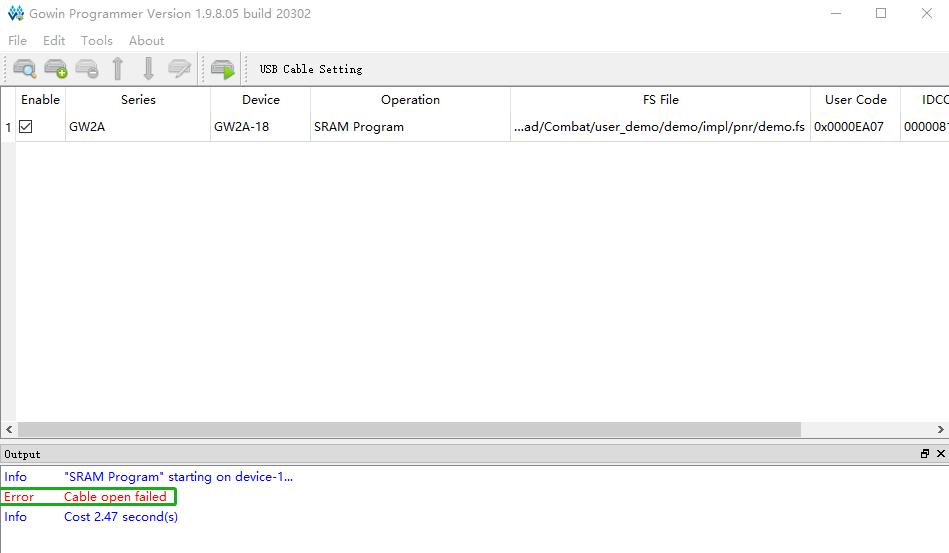

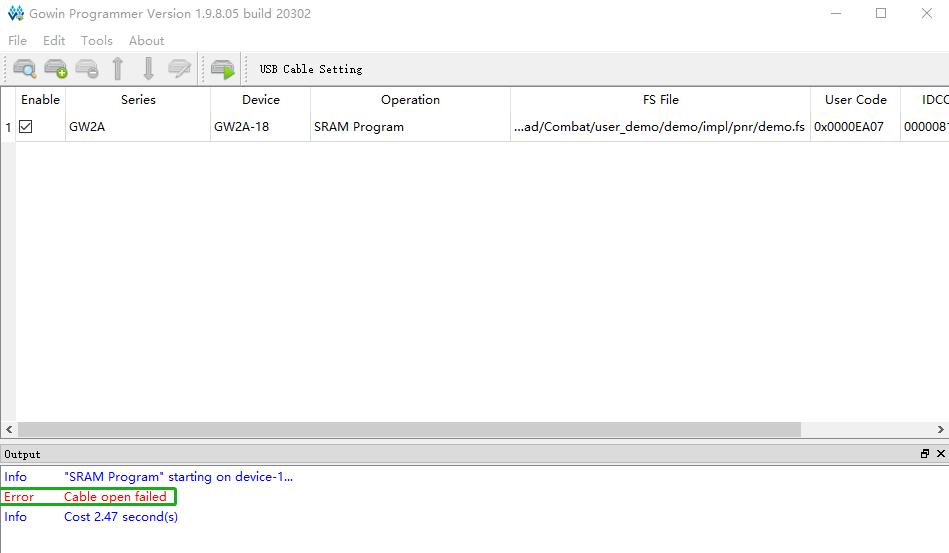

使用高云烧录工具Gowin Programmer烧录程序中第一次上电经常会出现找不到仿真器的错误,如下图所示。

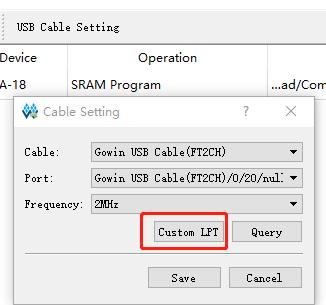

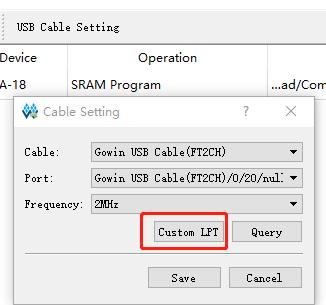

经过摸索,发现了一个基本100%上解决的办法。第一步点击“USB Cable Setting”,在弹出的窗口界面中点击“Custom LPT”按键,如下图所示。

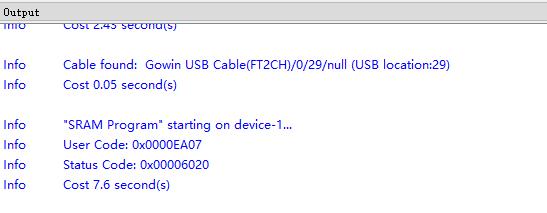

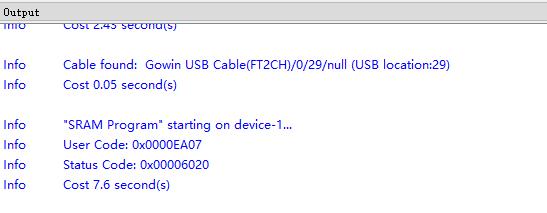

在弹出的界面中点击“Add”按钮,然后再在上图的界面中点击“Query”按键,最终点击“Save”按键,再次进行烧录,可以看到烧录成功的界面,如下图所示。

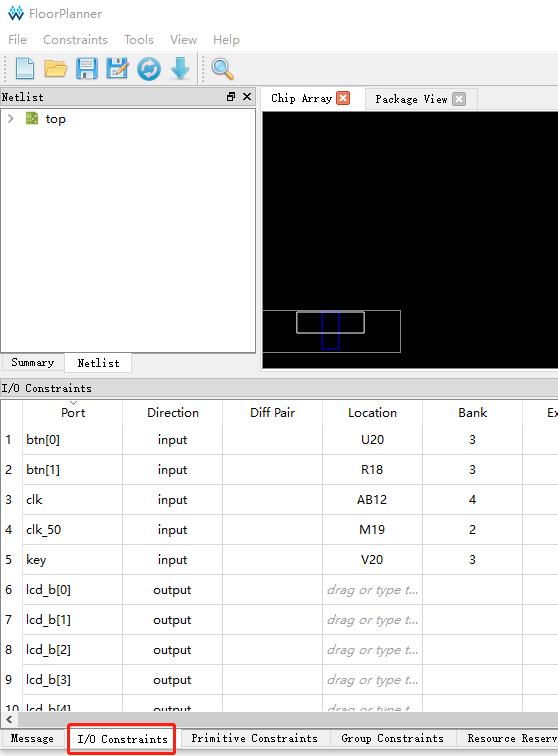

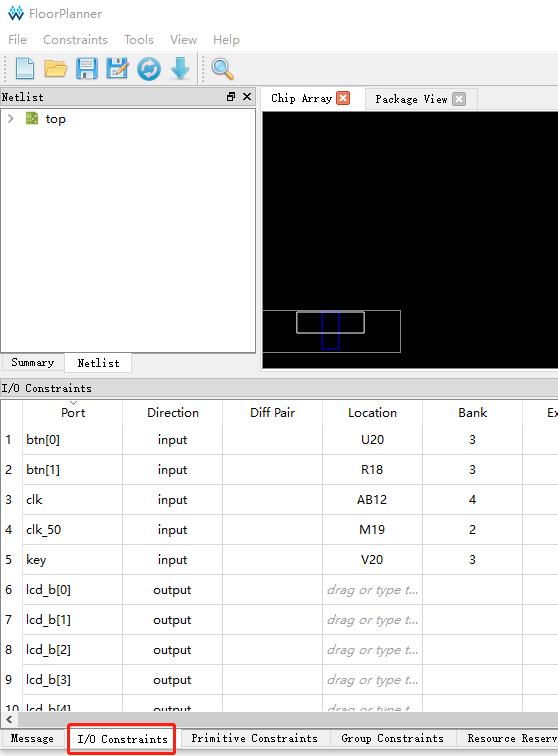

FPGA工程是通过顶层Verilog文件和真实的硬件原理图的连接进行对应的,将其称之为用户约束(布线器),云源软件通过“Process”Tab中的“User Constraints”选项下“FloorPlanner”子选项进入FloorPlanner显示界面,如下图所示,真实的引脚通过图中红色部分的“I/0 Constraints”选择不同信号的硬件管脚号、电平、速度、驱动能力等。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

【高云半导体Combat开发套件试用体验】RISC-V处理器蜂鸟E203在高云FPGA平台上的移植实践2022-11-10 5238

-

【高云半导体Combat开发套件试用体验】基础测评GPIO+串口测评2022-07-04 3553

-

【高云半导体Combat开发套件试用体验】Combat demo调试运行及小建议2022-07-01 3832

-

【高云半导体Combat开发套件试用体验】FPGA基本语法及Combat使用小技巧2022-06-23 3751

-

【高云半导体Combat开发套件试用体验】+一次开箱2022-06-12 16969

-

【高云半导体Combat开发套件试用体验】完整开箱报告2022-06-05 2576

-

【高云半导体Combat开发套件试用体验】之开箱测试2022-06-01 3630

-

【RISC-V专题】高云半导体Combat开发套件首发试用2022-04-15 7173

-

【Combat FPGA开发板】开发板简介+原理图+使用手册2021-04-22 3961

全部0条评论

快来发表一下你的评论吧 !