浅谈PCB串扰及降低方法

PCB设计

描述

先来说一下什么是串扰,串扰就是PCB上两条走线,在互不接触的情况下,一方干扰另一方,或者相互干扰。主要表现是波形有异常杂波,影响信号完整性(Signal integrity, SI)等等。一般情况下可以分为容性串扰和感性串扰两种。

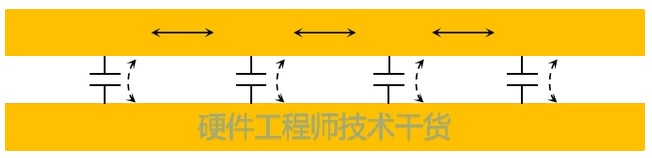

容性串扰,如上图所示:

PCB中两条平行的走线可以等效为一个电容器,当然这电容器容值非常小,虽然非常小,有时候足以影响信号完整性。当其中一条走线中有高速信号传输时,这个等效电容器不断的充放电,电容的特性是通交流阻直流,高速信号会通过电容器耦合到另外一条走线上,使信号完整性降低。上图中两条走线如果位于相邻上下层,且距离很近,等效电容更大,容性串扰更严重。

感性串扰,如上图所示:

PCB中两条平行的走线,当其中一条走线有高速信号传输时,产生交变磁场,这个交变磁场作用到另外一条走线后,会在这条走线内部产生感应电流。原理类似变压器。容性串扰和感性串扰是同时存在的。

现在的电子产品集成度越来越高,封装越来越小,走线越来越密集,串扰不可避免,也不可消灭,尽量降低,只要能够保证产品稳定可靠就好。以下列举了几种降低串扰的方法:

1、敏感的信号线,比如音频等模拟信号,尽量远离数字信号线。

2、敏感线严禁和数字信号线平行走线。

3、关键的高速信号线尽量使用GND包裹,上下左右立体式,GND能够吸收各种串扰噪声,把干扰源扼杀在摇篮里,GND包裹后也基本满足了3W法则。

举个例子:

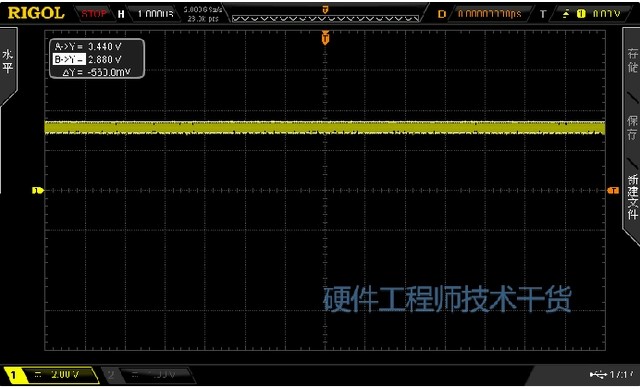

我司某产品在做板级测试的时候,发现某个GPIO波形异常,下图所示,直观感受是:高电平很“粗”。

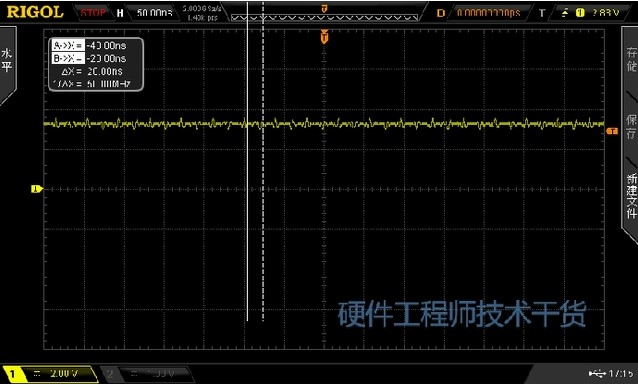

示波器拉开波形是这样的,几十MHz的高频信号,如下图:

看了一下电路发现这个GPIO和一个25MHz的CLK并行了很长距离。

-

什么是串扰?PCB走线串扰详解2023-09-11 2487

-

消除串扰的方法2009-06-18 5105

-

高速PCB设计中如何消除串扰?2019-07-25 4287

-

解决串扰的方法2019-08-14 20726

-

如何解决PCB串扰问题2020-07-19 2949

-

如何解决PCB布局中的串扰问题2021-01-13 3841

-

浅谈串扰溯源,串扰是怎么产生的2021-03-29 4452

-

浅谈“串扰”2021-01-23 2988

-

如何降低串扰对PCB板的影响2022-07-07 1353

-

串扰是怎么引起的 降低串扰有哪些方法2022-08-15 11967

-

PCB布线减少高频信号串扰的措施都有哪些?2023-10-19 2763

-

减少串扰的方法有哪些2024-01-17 3513

-

PCB产生串扰的原因及解决方法2024-01-18 3367

-

在PCB设计中,如何避免串扰?2024-02-02 3173

全部0条评论

快来发表一下你的评论吧 !