如何理解HLS Block-level输入输出信号之间的时序关系

描述

默认情况下,VitisHLS会对待综合的C函数使用ap_ctrl_hs接口,这其实是一种握手方式。在这个接口中,我们会看到ap_start、ap_idle、ap_ready和ap_done等信号(这些信号被称为Block-level输入/输出信号)。其中ap_start是输入信号,而其余三个信号是输出信号。那么我们如何根据这些信号管理输入数据呢?这就要理解这些信号之间的时序关系。为便于说明,我们以一个简单的算法为例。

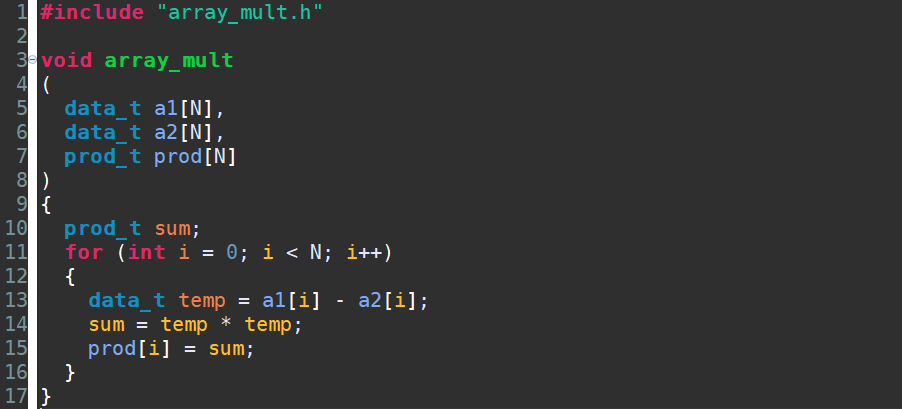

如下图所示代码片段。函数array_mult有3个形参。其中a1和a2是长度为N的一维数组,两者对应元素相减再平方即为另一形参prod。显然,prod也是长度为N的一维数组。

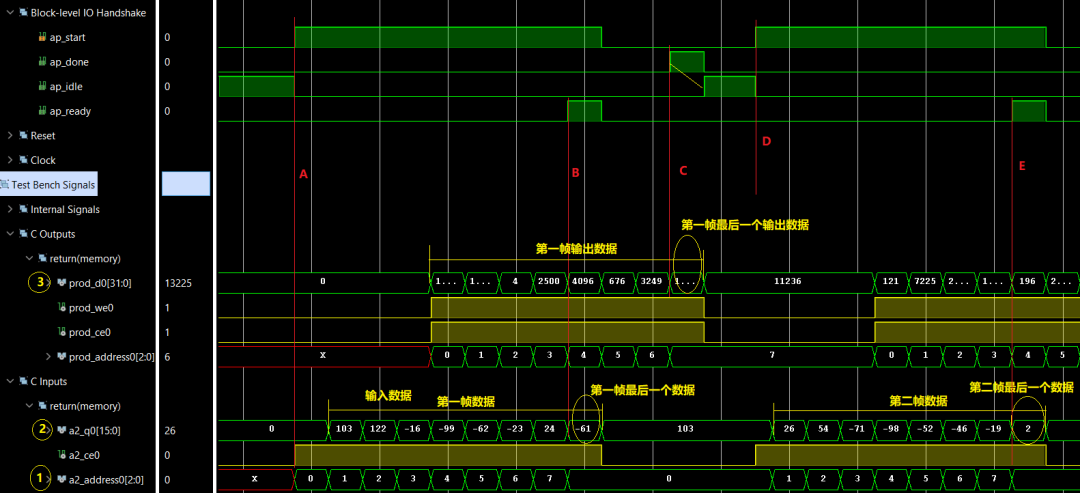

为了观察这些Block-level信号之间的时序关系,我们在仿真时将多次调用函数array_mult。为此,在描述测试激励时,输入激励以两个二维数组形式给出,这两个二维数组对应的每一列作为array_mult的输入。假定这两个二维数组是8行4列的数组,C/RTLco-sim仿真结果波形如下图所示。

标记1为数组a2对应存储单元的读地址a2_address,共8个数据;标记2显示了读书的数据数值a2_q0,可以看到两者相差一个时钟周期。那么什么时候a2_address可以发生变化呢?我们从标记A可以看到,在标记A左边,ap_idle为高电平,表明该模块处于空闲状态,标记A之后,ap_start为高电平,同时ap_idle变为低电平。一旦ap_start为高,a2_ce0即为高,表明可以开始读取a2对应的数据。当第一帧8个数据读取完毕,即读取到第一帧最后一个数据时,ap_ready为由低电平变为高电平且持续一个时钟周期,表明第一帧输入数据已读取完毕,如图中标记B。紧接着ap_start也由高电平变为低电平。当第一帧计算完毕,输出对应的8个数据后,ap_done由低电平变为高电平并持续一个时钟周期,如图中标记C。当ap_done由高变低时,ap_idle则由低变高,表明可以再次启动该模块。因此,我们可以看到标记D处ap_start为高,之后a2_ce0由低变高开始读取第二帧输入数据。读取到第二帧输入数据的最后一个数据后,ap_ready由低电平变为高电平。

由此我们可以得出如下结论:

ap_start受ap_idle影响,只有当ap_idle为高时,才可以启动ap_start,将其由低电平变为高电平;

ap_ready为高电平时,表明已完成一帧的输入数据读取任务;

ap_done为高电平时,表明已完成一帧的输出数据写入任务;

ap_done持续一个时钟周期由高变低后,ap_idle会由低变高。

审核编辑:汤梓红

-

IGBT的原理,输入输出和控制信号2025-12-06 1773

-

误差放大器的输入输出关系2024-09-11 2985

-

锁相环的输入输出相位一致吗?2024-01-31 2324

-

输入输出电压差与效率的关系2024-01-05 1692

-

plc带模拟量输入输出和不带模拟量输入输出有什么区别啊?2023-10-17 2535

-

boost升压电路输入输出关系2023-08-27 4308

-

创建输入输出接口时序约束的窍门2022-08-02 3303

-

GPIO通用输入输出2021-12-20 878

-

请问倍频器的输入信号和输出信号的相位关系?2018-10-12 6335

-

一文详解FPGA编程技巧输入输出偏移约束2018-07-14 6082

-

什么是输入输出模块_输入输出模块有什么作用2018-05-21 121418

-

HLS系列 – High LevelSynthesis(HLS) 的端口综合12017-02-08 1132

-

数字信号输入输出接口电路2016-12-16 1039

-

视频打印机的输入输出2009-12-31 1754

全部0条评论

快来发表一下你的评论吧 !