浅谈Perl在IC设计中的运用

EDA/IC设计

描述

1、数字IC设计中为什么要使用perl脚本?

Perl脚本能够高效批量化操作,降低错误率,提高效率。如批量生成verilog代码,快速生成仿真testbench,verilog代码的自动对齐,module模块的例化连接。

2、perl脚本有哪些应用?

Perl脚本可以用于生成有规律的代码,如SOC地址仲裁模块verilog代码、不同规格的CRC校验verilog代码、不同规格的FIFO代码。

在芯片设计过程中,所用到的FIFO数量很多,大于100多个很常见,甚至大于500个都是存在的。而不同规格的FIFO基本都是用最基础的RAM模块来搭建实现的,如果依靠人工编写,错误率高而且效率极其低下。因此,使用perl脚本编写不同规格的FIFO代码是可靠高效的方式。

快速生成testbench:在进行功能仿真的时候,需要编写测试案例testbench,可以利用perl脚本快速生成测试案例的大部分代码,手动添加少量verilog,即可快速完成testbench的编写,有效减少工作量。

Verilog代码自动对齐:verilog代码在人工编写时全靠手敲空格符会很累,并且效率低下,采用perl脚本一键对齐,效率高节省体力。

Module例化连接:有些module模块的输入输出信号有上百条,依靠手动添加会很繁琐,此时利用perl脚本生成例化模块可以有效提高效率,降低错误率。

3、如何使用perl脚本?

生成RAM代码步骤:--在window环境中

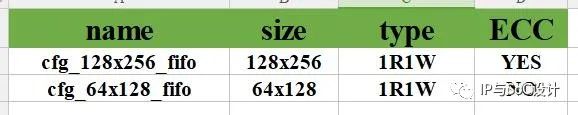

1)在Excel表格中填写不同规格的RAM参数,如128*256 FIFO 1R1W 读写延时 名称等

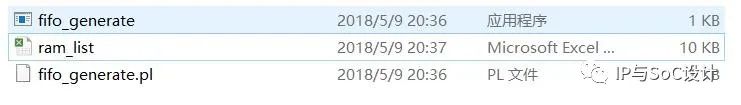

2)写好Perl脚本后保存为pl格式后,编译为exe格式的程序

3)在Windows系统里将填写好的表格拖拽到Perl脚本图标上,即可生成代码

图 1 FIFO在表格中的填写(参数没列全)

图 2 将ram_list表格拖拽到fifo_generate的程序图标上

生成RAM代码步骤:--在linux环境中

1) 在Excel表格中填写不同规格的RAM参数,如128*256 FIFO 1R1W 读写延时 名称等,将填写好的表格保存为CSV格式: ram_list.csv

2) 写好Perl脚本后保存为pl格式:fifo_generate.pl

3) 将perl脚本和ram_list.csv放在同一个目录下,在此目录下的terminal终端中输入./fifo_generate.pl即可生成verilog代码

Perl在IC设计中的运用:关键字替换

1、采用perl更新文件关键字

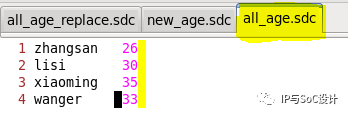

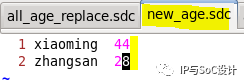

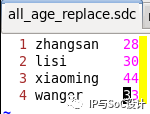

New_age.sdc和all_age.sdc中包含人名和对应的年龄,使用new_age.sdc中的年龄更新all_age.sdc中的年龄信息。如xiaoming 年龄需要更新到44,zhangsan年龄更新到28

2、perl脚本如何实现

脚本实现原理如下:

1.打开已有的文件new_age.sdc

2.逐行匹配,关键字匹配,是否包含name + age,保存为name和new_age。如果包含,打开all_age.sdc,逐行匹配name,如果匹配上,则将new_age替换old_age.否则保持不变。将替换结果保存在line_save里,保存到tmp_file。

3.一次内部循环后,将tmp_file move为output

4.所有循环完成后输出output

3、perl脚本如何使用

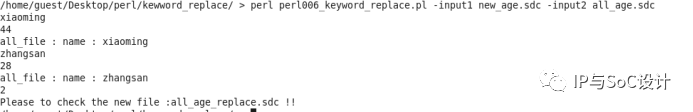

使用命令:perl perl006_keyword_replace.pl -input1 new_age.sdc -input2 all_age.sdc

原文件:all_age.sdc和new_age.sdc

生成的新文件:all_age_replace.sdc

xiaoming和wanger 年龄替换成功:

来源:

https://blog.csdn.net/icxiaoge/article/details/80259324

https://blog.csdn.net/icxiaoge/article/details/103842266

编辑:黄飞

- 相关推荐

- 热点推荐

- IC设计

-

perl语法2024-11-04 368

-

浅谈智能电表远程抄表在电力系统中的运用分析2024-02-20 1841

-

perl进程管理2023-12-01 994

-

展频IC在摄像头上的运用2023-04-14 485

-

搞芯片怎么能不懂perl语言呢?2023-03-15 1204

-

浅谈IC设计/验证中ChatGPT的应用2023-02-10 1687

-

如何在我的分发包中添加perl模块?2023-02-02 473

-

浅谈光伏并网柜的实际运用2021-09-23 1475

-

浅谈智能电网在智慧城市中的应用2020-07-16 2068

-

浅谈磁性槽楔在高效率电机中的应用2017-01-01 823

-

浅谈盐雾试验在电能表中的应用2016-04-06 2546

-

PERL编程24学时教程(完整版)2015-11-17 1410

-

perl语言在IC设计中的应用2012-01-11 46218

-

Perl语言入门教程2009-07-30 3673

全部0条评论

快来发表一下你的评论吧 !